Article

# Impact of Residual Stress on a Polysilicon Channel in Scaled 3D NAND Flash Memory

Juyoung Lee 1, Dong-Gwan Yoon 2, Jae-Min Sim 2, and Yun-Heub Song 2,\*

- Department of Nanoscale Semiconductor Engineering, Hanyang University, Seoul 04763, Republic of Korea; gnuoyujeel@.hanyang.ac.kr

- Department of Electronics Engineering, Hanyang University, Seoul 04763, Korea; wja03015@hanyang.ac.kr, yhsong2008@hanyang.ac.kr

- \* Correspondence: yhsong2008@hanyang.ac.kr; Tel.: +82-2-2220-4136

**Abstract:** The effects of residual stress in a tungsten gate on a polysilicon channel in scaled 3D NAND flash memories were investigated using a technology computer-aided design simulation. The NAND strings with respect to the distance from the tungsten slit were also analyzed. The scaling of the spacer thickness and hole diameter induced compressive stress on the polysilicon channel. Moreover, the residual stress of polysilicon channel in the string near the tungsten slit had greater compressive stress than the string farther away. The increase in compressive stress in the polysilicon channel degraded the Bit-Line current ( $I_{on}$ ) because of stress-induced electron mobility deterioration. Moreover, a threshold voltage shift ( $\triangle V_{th}$ ) occurred in the negative direction because of conduction band lowering.

Keywords: 3D NAND; hole profile; mechanical stress; polysilicon channel; scaling; TCAD

### 1. Introduction

The memory market, originally driven solely by the mobile device industry, has expanded because of emerging artificial intelligence and automobiles industries. The explosive growth of data generated by these industries demands an increase in the storage capacity of 3D NAND. This demand has been met by increasing the number of stacking gate layers (WL), which reached 128 levels in 2019 [1,2]. As the number of WL layers increases, the difficulties in fabrication, such as hole etching and control of the mechanical stress, have increased [3,4]. Therefore, vertical scaling is necessary to achieve 3D NAND technology with 200 levels and beyond because the thickness of the total chip is limited to approximately 25 µm for stacking 16 chips [5]. Moreover, lateral scaling, such as of the hole diameter, is another way to achieve a higher density [6]. In our previous work, the annealing temperature, channel hole angle, and tungsten intrinsic stress were parameters that changed the residual stress of the polysilicon channel in 3D NAND, and the change in stress distribution of the polysilicon channel affects the electrical characteristics, degrading the 3D NAND BL current [7]. Furthermore, the residual stress generates the dangling bond, which increases the trap site leading to deterioration of the interface properties. Therefore, cell characteristics, such as the leakage current and memory window, were degraded [8]. Although there are various studies on the mechanical stress in 3D NAND, the impact of vertical and lateral scaling on the residual stress of the polysilicon channel has not been studied. This work investigated the residual stress of the polysilicon channel according to the spacer oxide thickness and hole diameter and its impact on the Ion and Vth of 3D NAND. The distribution of threshold voltage was also analyzed using TCAD simulation.

#### 2. Materials and Methods

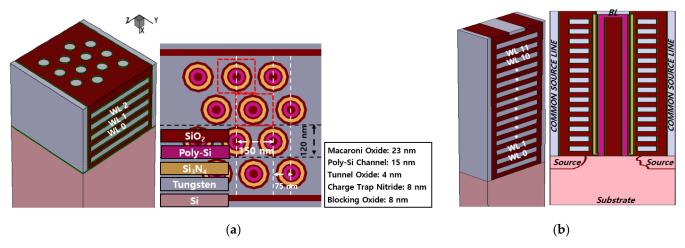

The simulations were conducted on two types of 3D NAND structures to investigate the residual stress of films and stress-induced effects on the electrical characteristics, respectively, and minimize simulation time. Figure 1a shows the structural and stack details of the 3D NAND device for stress analysis simulation. Twelve strings, with each string comprising 3 WLs with a string select line (SSL) and a ground select line (GSL), were considered. The diameter of the vertical hole was 120 nm with 150 nm of cell string pitch. Two strings with the red square dotted box were selected for the stress simulation to investigate the position of strings relative to the common source line. The string located near the center and the common source line of 3D NAND will be called center and slit string, respectively. The structure for the stress-induced effects simulation consists of 12 WLs, as shown in Figure 1b. The thickness of the macaroni oxide, polysilicon channel, tunnel oxide, charge trap nitride, and blocking oxide were identical for both structures.

**Figure 1.** 3D NAND model used for stress simulation and material parameters. 3D simulation model of 3D NAND used in (a) the stress simulation and (b) the stress-induced electrical characteristics variation simulation.

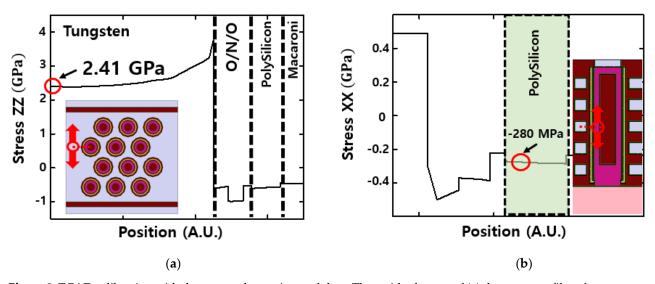

To accurately analyze the impact of scaling on the residual stress of films, the internal stress of tungsten films was tuned to match the industrial devices. As shown in Figure 2a, the residual stress of the tungsten films after the tungsten replacement gate process was approximately 2.41 GPa, which matches reported experimental data [9]. The residual stress of the polysilicon channel at the final structure in the simulation, as shown in Figure 2b, was –280 MPa, which is also similar to the reported data [10]. The distribution of the residual stress of the polysilicon channel in 3D NAND was then analyzed when scaled. The residual stress was calculated using the Maxwell model, which takes dilatational and deviatoric stress into consideration [11]. The mechanical parameters used in this study are summarized in Table 1.

**Table 1.** Mechanical parameters used in the 3D NAND simulation. The Young's modulus (YM), bulk modulus (BM), shear modulus (SM), Poisson's ratio (PR), and coefficient of thermal expansion (CTE) were used to calculate the mechanical stress simulation.

| Materials       | YM [GPa] | BM [GPa] | SM [GPa] | PR   | CTE  |

|-----------------|----------|----------|----------|------|------|

| Silicon Oxide   | 70       | 39       | 29       | 0.20 | 1.37 |

| Polysilicon     | 160      | 99       | 65       | 0.23 | 3.00 |

| Silicon Nitride | 270      | 196      | 106      | 0.27 | 3.20 |

| Tungsten        | 410      | 311      | 160      | 0.28 | 4.60 |

| Silicon         | 130      | 98       | 51       | 0.28 | 3.00 |

**Figure 2.** TCAD calibration with the reported experimental data. The residual stress of (a) the tungsten film after tungsten replacement gate process and (b) the polysilicon channel at the final structure.

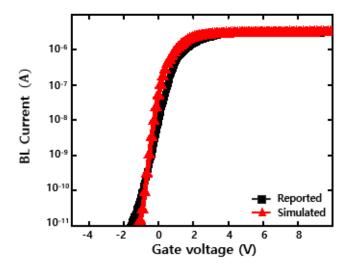

To accurately investigate the impact of residual stress on the electrical characteristics, the BL current and threshold voltage were calibrated by tuning the doping and interface trap parameters of polysilicon to match the reported data as shown in Figure 3 [12]. Moreover, the deformation potential (minimum, ekp, and hkp) and subband (doping, effective mass, and scattering) model were incorporated in the TCAD device simulations.

Figure 3. TCAD calibration for the initial state Id-Vg characteristics of the memory transistor with the reported data [12].

## 3. Results and Discussion

## 3.1. Impact of scaling on the residual stress of the polysilicon channel

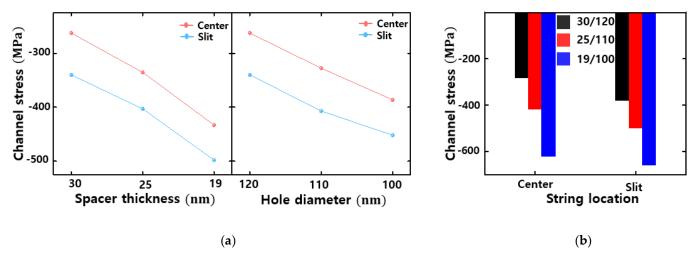

The residual stress of the polysilicon channel in two strings was considered for analyzing the impact of tungsten films in a common source line. As shown in Figure 4a, the polysilicon channel in the string closest to the common source line had greater compressive residual stress than that in the string closest to the center. When the thickness of the spacer oxide was scaled from 30 nm to 25 nm and 19 nm, with the hole diameter fixed to 120 nm, the channel stress increased in the compressive direction because of the adjacent tungsten gates, which had greater tensile stress than the other films because of their proximity [7]. When the hole diameter was scaled from 120 nm to 100 nm by 10 nm, with the spacer thickness fixed to 30 nm, the channel stress was also increased in compression because of the increase in volume of the tungsten gates surrounding the hole. Figure 4b

shows the channel stress when the spacer thickness and hole diameter were both scaled. The channel stress nearly doubled in compression from -260 MPa to -620 MPa in the string closest to center, and from -340 MPa to -660 MPa in the string closest to the common source line when scaled.

**Figure 4.** The channel stress of the two strings with respect to the distance from the common source line. The channel stress of two strings when the spacer thickness and hole diameter were (a) individually scaled and (b) both scaled.

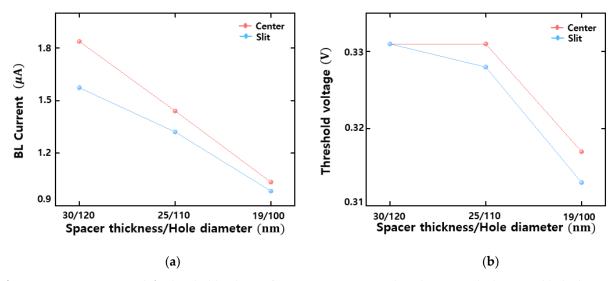

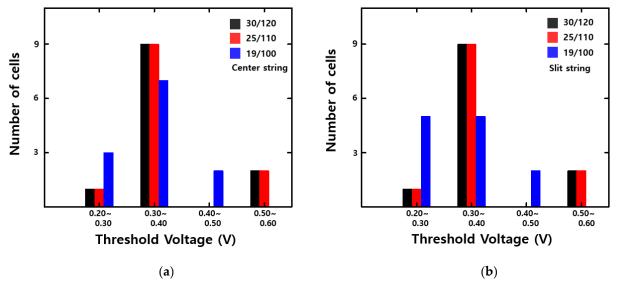

Electrical characteristics, such as BL current (Ion) and threshold voltage (Vth), are affected by the residual stress of the channel region in 3D NAND [13,14]. The compressive channel stress decreases the Ion value because of the degradation of electron mobility caused by piezo-resistance effect [15]. Furthermore, V<sub>th</sub> is negatively shifted with increasing compressive channel stress because of the lowering of the conduction band [16,17]. The electrical characteristics of the scaled structure are affected by the stress factors and scaling factors. To analyze the impact of only the stress factors, the structure shown in Figure 1b was used, and the residual stress of the polysilicon channel was modulated by depositing tungsten film with different internal stress to match the simulation data of the channel stress shown in Figure 4b. The BL current and threshold voltage were measured on WL5. Figure 5 presents the BL current and threshold voltage as a function of spacer thickness and hole diameter with the string location. As shown in Figure 5a, the BL current of the string located near the center degraded from  $1.84 \mu A$  to  $1.44 \mu A$  and 1.03μA with scaling. Moreover, the BL current of the string located near the slit was deteriorated from 1.57  $\mu A$  to 1.32  $\mu A$  and 0.98  $\mu A$ . The degradation of the BL current in the two studied strings was attributed to the deterioration of the electron mobility with increased compressive residual channel stress with scaling [18]. The threshold voltage was shifted negatively in both strings with scaling, as shown in Figure 5b, which can be attributed to conduction band lowering because of the increased channel compressive stress. Therefore, the scaling of the spacer thickness and hole diameter deteriorates the BL current and negatively shifts the threshold voltage of 3D NAND. Figure 6 shows the histogram of threshold voltage of cells in the string located near the center and common source line. When the spacer thickness and hole diameter were scaled to 25 nm and 110 nm, the distribution of threshold voltage of cells showed no change on both strings. However, the negative shift of threshold voltage distribution occurred on both string by the scaling of spacer thickness and hole diameter to 19 nm and 100 nm, respectively.

Figure 5. (a) BL current and (b) threshold voltage of two strings on WL5 when the spacer thickness and hole diameter are both scaled.

**Figure 6.** Distribution of initial threshold voltages of cells when the spacer thickness and hole diameter are both scaled on the string located near the (a) center and (b) common source line

## 4. Conclusions

The impact of scaling on the residual stress of a polysilicon channel of two strings in 3D NAND was investigated using TCAD simulation. When the spacer thickness and hole diameter were scaled, the residual polysilicon channel stress was increased in compression, causing detrimental effects on the electrical characteristics. Moreover, the polysilicon channel stress of the string located close to the common source line was greater than the string located close to center. Compressive residual channel stress degraded the BL current because of the electron mobility deteriorated and a negative shift of V<sub>th</sub> was induced because of the reduced conduction band energy of the polysilicon channel.

This study implies that the residual compressive stress of tungsten must be controlled to prevent degradation of the BL current and the negative shift of the threshold voltage. Further studies are necessary for investigating the impact of stress induced channel residual stress on the memory characteristics of 3D NAND.

**Author Contributions:** Conceptualization, J.L., J.S., and D.-G.Y.; methodology, J.L., J.S., and D.-G.Y.; software, J.L. and D.-G.Y.; validation, J.L.; formal analysis, J.L.; investigation, J.L. and D.-G.Y.; resources, J.L. and D.-G.Y.; data curation, J.L. and D.-G.Y.; writing—original draft preparation, J.L.; writing—review and editing, Y.-H.S.; visualization, J.L. and D.-G.Y; supervision, Y.-H.S.; project administration, J.L.; funding acquisition, Y.-H.S. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by Samsung Electronics Co., LTD, and also supported by the Ministry of Trade, Industry & Energy (MOTIE (project number 20003808 and project number 10080625)) and Korea Semiconductor Research Consortium (KSRC) support program for the development of the future semiconductor device.

**Acknowledgments:** The authors would like to thank Dr. Lee, J. K. and Dr. Lim, J. H. at the Memory Division, Memory R&D Center, Samsung Electronics Co., Ltd., Hwaseong, South Korea, for their technical advice and feedback with regards to this paper.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Siau, C.; Kim, K. H.; Lee, S.; Isobe, K.; Shibata, N.; Verma, K.; Ariki, T.; Li, J.; Yuh, J.; Amarnath, A.; Nguyen, Q.; Kwon, O.; Jeong, S.; Li, H.; Hsu, H. L.; Tseng, T. y.; Choi, S.; Darne, S.; Anantula, P.; Yap, A.; Chibvongodze, H.; Miwa, H.; Yamashita, M.; Watanabe, M.; Hayashi, K.; Kato, Y.; Miwa, T.; Kang, J. Y.; Okumura, M.; Ookuma, N.; Balaga, M.; Ramachandra, V.; Matsuda, A.; Kulkani, S.; Rachineni, R.; Manjunath, P. K.; Takehara, M.; Pai, A.; Rajendra, S.; Hisada, T.; Fukuda, R.; Tokiwa, N.; Kawaguchi, K.; Yamaoka, M.; Komai, H.; Minamoto, T.; Unno, M.; Ozawa, S.; Nakamura, H.; Hishida, T.; Kajitani, Y.; Lin, L. In 13.5 A 512Gb 3-bit/Cell 3D Flash Memory on 128-Wordline-Layer with 132MB/s Write Performance Featuring Circuit-Under-Array Technology, 2019 IEEE International Solid-State Circuits Conference (ISSCC), 17-21 Feb. 2019; 2019; pp 218-220.11.

- 2. Goda, A., 3-D NAND Technology Achievements and Future Scaling Perspectives. IEEE Transactions on Electron Devices 2020, 67 (4), 1373-1381.

- 3. Kim, H.; Ahn, S.; Shin, Y. G.; Lee, K.; Jung, E. In Evolution of NAND Flash Memory: From 2D to 3D as a Storage Market Leader, 2017 IEEE International Memory Workshop (IMW), 14-17 May 2017; 2017; pp 1-4.Author 1, A.; Author 2, B. *Book Title*, 3rd ed.; Publisher: Publisher Location, Country, 2008; pp. 154–196.

- 4. Parat, K.; Goda, A. In Scaling Trends in NAND Flash, 2018 IEEE International Electron Devices Meeting (IEDM), 1-5 Dec. 2018; 2018; pp 2.1.1-2.1.4.

- 5. Lee, S. In Technology scaling challenges and opportunities of memory devices, 2016 IEEE International Electron Devices Meeting (IEDM), 3-7 Dec. 2016; pp 1.1.1-1.1.8.

- 6. Kim, J. H.; Lim, J.; Kim, H. S.; Cho, E. S.; Yeo, C.; Lee, W.; You, B.; Lee, B.; Kang, M.; Jang, W.; Kwon, Y.; Lee, K.; Lee, J.; Kim, M. C.; Lee, J. Y.; Hur, S.; Ahn, S. J.; Hong, H., Shin, Y. G.; Kim, H. -S.; and Song, J., Highly Manufacturable 7th Generation 3D NAND Flash Memory with COP structure and Double Stack Process. VLSI Symposium Tech 2021.

- 7. Namkoong, Y.; Yang, H. J.; Song, Y. H., Mechanical Stress Distribution and the Effects of Process Parameter Changes in Vertical NAND Flash Memory. Journal of Nanoscience and Nanotechnology 2017, 17, 5055-5060(6).

- 8. Oh, Y.; Sim, J.; Kino, H.; Kim, D.; Tanaka, T.; Song, Y., The Effect of Tungsten Volume on Residual Stress and Cell Characteristics in MONOS. IEEE Journal of the Electron Devices Society 2019, 7, 382-387.

- 9. Luoh, T.; Huang, Y.; Chen, C.; Hung, Y.; Yang, L.; Yang, T.; Chen, K. In Tungsten Gate Replacement Process Optimization in 3D NAND Memory, 2019 Joint International Symposium on e-Manufacturing & Design Collaboration(eMDC) & Semi-conductor Manufacturing (ISSM), 6-6 Sept. 2019; 2019; pp 1-4.

- 10. Kruv, A.; Arreghini, A.; Verreck, D.; Gonzalez, M.; bosch, G. V. d.; Wolf, I. D.; Rosmeulen, M., Impact of Mechanical Stress on 3-D NAND Flash Current Conduction. IEEE Transactions on Electron Devices 2020, 67 (11), 4891-4896.

- 11. Roylance, D., Engineering Viscoelasticity. Massachusetts Institute of Technology, Cambridge, MA 2001.

- 12. Bhatt, U. M.; Manhas, S. K.; Kumar, A.; Pakala, M.; Yieh, E., Mitigating the Impact of Channel Tapering in Vertical Channel 3-D NAND. IEEE Transactions on Electron Devices 2020, 67 (3), 929-936.

- 13. Shimizu, A.; Hachimine, K.; Ohki, N.; Ohta, H.; Koguchi, M.; Nonaka, Y.; Sato, H.; Ootsuka, F. In Local mechanical-stress control (LMC): a new technique for CMOS-performance enhancement, International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224), 2-5 Dec. 2001; 2001; pp 19.4.1-19.4.4.

- 14. Kruv, A.; Arreghini, A.; Gonzalez, M.; Verreck, D.; bosch, G. V. d.; Wolf, I. D.; Furnémont, A. In Impact of Mechanical Stress on the Electrical Performance of 3D NAND, 2019 IEEE International Reliability Physics Symposium (IRPS), 31 March-4 April 2019; 2019; pp 1-5.

- 15. Ito, S.; Namba, H.; Yamaguchi, K.; Hirata, T.; Ando, K.; Koyama, S.; Kuroki, S.; Ikezawa, N.; Suzuki, T.; Saitoh, T.; Horiuchi, T. In Mechanical stress effect of etch-stop nitride and its impact on deep submicron transistor design, International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), 10-13 Dec. 2000; 2000; pp 247-250.

- 16. Weimin, Z.; Fossum, J. G., On the threshold Voltage of strained-Si-Si/sub 1-x/Ge/sub x/ MOSFETs. IEEE Transactions on Electron Devices 2005, 52 (2), 263-268.

- 17. Lim, J. S.; Yang, X.; Nishida, T.; and Thompson, S. E., Measurement of conduction band deformation potential constants using gate direct tunneling current in n-type metal oxide semiconductor field effect transistors under mechanical stress. Applied Physics Letters 2006, 89 (7).

- 18. Smith, C. S., Piezoresistance Effect in Germanium and Silicon. Physical Review 1954, 94 (1), 42-49.