Article

# Linearization Technique of Low Power Opamps in CMOS FD-SOI Technologies

Wieslaw Kuzmicz\*

Faculty of Electronics and Information Technology, Institute of Microelectronics and Optoelectronics, Warsaw University of Technology, Warsaw, Poland; wieslaw.kuzmicz@pw.edu.pl

\* Correspondence: wieslaw.kuzmicz@pw.edu.pl

**Abstract:** Negative feedback to the back gate of MOS devices available in FD-SOI technologies can be used to improve linearity of operational amplifiers. Two operational amplifiers designed and fabricated in a 22nm FD-SOI technology illustrate this technique, its advantages and limitations.

Keywords: CMOS analog integrated circuit; FD-SOI; feedback; linearity; operational amplifier

#### 1. Introduction

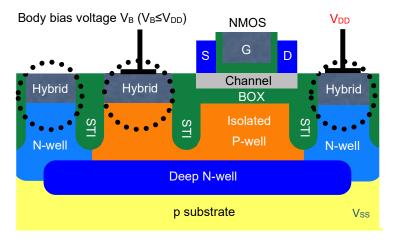

In comparison with the mainstream bulk CMOS, CMOS FD-SOI technology [1,2] provides a set of benefits for analog circuits, such as e.g. better transconductance efficiency  $(g_m/I_D)$ , higher bandwidth  $(f_T$  and  $f_{max})$ , better matching, lower subthreshold leakage. However, a really unique feature of FD-SOI MOS devices is that they are double-gate transistors. The semiconductor region under the transistor channel (called similarly as in the bulk CMOS: N-well or P-well) is isolated from the channel by buried oxide (BOX) layer and can be used as the second, back gate. N-wells are isolated from p-type substrate by a pn junction. P-wells can also be isolated from p-type substrate by the third deep well (Figure 1). This allows to apply bias voltage to N-wells as well as to P-wells. Back bias, i.e. voltage applied to the back gate, can be applied to each device individually or to a group of devices located over a common P-well or N-well. Back bias allows to change the threshold voltage  $V_T$  as seen by the front gate and fine tune the performance and power consumption of FD-SOI-based digital circuits.

**Figure 1.** NMOS device located over isolated P-well. "Hybrid" regions are regions where BOX is removed and serve as contact areas to N-wells and P-wells.

It is worth noting that FD-SOI technologies can be technologies of choice for ultralow voltage CMOS circuits. With proper back bias the supply voltage in digital circuits can be reduced to  $0.4\ldots0.5$  V. Such a reduction is more difficult in the case of analog circuits, but even without it the maximal supply voltages in industrial deep submicron FD-SOI technologies are at the level of  $0.8\ldots1$ V.

While in digital circuits back bias is applied as a constant (but often variable) voltage, in analog circuits ac signals can be applied to the back gate as well. This creates new opportunities for analog circuit design, which are still rather unexplored. In the majority of analog circuits published so far back biasing is used in a similar way as in digital circuits – to enhance or tune circuit performance by means of forward or reverse back bias (see e.g. three amplifiers [17 – 19] as examples).

It has been shown experimentally in [21] that a negative feedback loop between the output and the back gate of one of the input transistors can very effectively linearize the characteristics of an operational amplifier. This paper provides theoretical analysis of this linearization technique, including its limitations, in Section 2. In Section 3 characteristics of two opamps designed and fabricated in 22 nm FD-SOI technology are compared with theory. It is also shown how this linearization technique affects frequency response and variability of the amplifiers. Conclusions and possible extensions of this linearization technique are presented in Section 4.

# 2. Opamp linearization technique: the concept and theory

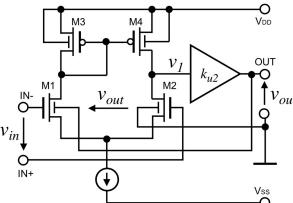

Many methods of linearization of operational amplifiers' characteristics, applicable to bulk CMOS technologies, have been proposed, see e.g. [3-10]. In this paper a technique is proposed that is specific to CMOS FD-SOI: negative feedback loop between the output of the opamp and the back gate of one of the transistors in the input differential pair, see Figure 2.

**Figure 2.** The concept of the linearization technique: output voltage between the output and the virtual ground is applied between the back gates of the input differential pair.

The front gates of devices of the input differential pair are driven by the input voltage  $v_{in}$  and the back gates of these devices are driven by the output voltage  $v_{out}$ . The output voltage of the input differential pair  $v_1$  is given by

$$v_1 = \frac{v_{in}g_{mf} - v_{out}g_{mb}}{g_{ds} + g_{ds4}} \tag{1}$$

where  $g_{mf}$  is the transconductance related to the front gate,  $g_{mb}$  is the transconductance related to the back gate,  $g_{ds2}$  and  $g_{ds4}$  are output conductances of the input transistors M2

and M4, respectively. The output voltage of the input differential pair is amplified by the second stage with voltage gain  $k_{u2}$ :

$$v_{out} = k_{u2} \frac{v_{in}g_{mf}}{g_{ds2} + g_{ds}} - k_{u2} \frac{v_{out}g_{mb}}{g_{ds2} + g_{ds}} . \tag{2}$$

This gives for the voltage gain  $k_u$  of the amplifier with the feedback loop

$$k_{u} = \frac{v_{out}}{v_{in}} = \frac{g_{mf}}{(g_{ds} + g_{ds})/k_{u2} + g_{mb}}.$$

(3)

It can be safely assumed that  $(g_{ds} + g_{ds})/k_{u2} \ll g_{mb}$ . As a result, the voltage gain  $k_u$  can be approximated with good accuracy by

$$k_u = \frac{v_{out}}{v_{in}} \approx \frac{g_{mf}}{g_{mb}}.$$

(4)

This small signal analysis suggests the necessary linearity condition of the feedback loop. The ratio  $g_{mf}/g_{mb}$  must be constant in the whole range of gate voltages at the front and back gates  $V_{CSJ}$  and  $V_{CSJ}$  and drain current  $I_D$  of the input transistors. This condition is satisfied when the input transistors work in weak inversion region for all combinations of the front and back gate voltages. In weak inversion the transconductance efficiency  $g_m/I_D$  is constant. It is demonstrated in [22] that both transconductance efficiencies  $g_{mf}/I_D$  and  $g_{mb}/I_D$  are constant in weak inversion. Since the drain current is, of course, the same for both gates,  $g_{mf}$  and  $g_{mb}$  are proportional to each other and their ratio is constant.

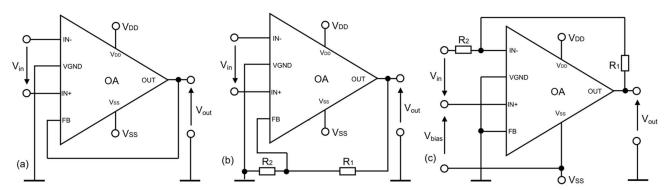

**Figure 3.** Three configurations of the amplifiers: (a) direct feedback (as in Figure 2), (b) feedback with voltage divider, (c) external linear negative feedback.

In Section 3 properties of two simple OTA-type amplifiers, to be used for acquisition of biological signals, are discussed. They have been designed and fabricated in an industrial 22 nm FD-SOI technology. Their properties will be discussed in three configurations (Figure 3). In these schematic diagrams VGND is the virtual ground. The voltage at this node equals  $0.5V_{DD}$ . FB is the connection to the back gate of the transistor M1. In the first configuration (Figure 3a, direct feedback configuration) the output voltage is applied directly to the body of M1, as in Figure 2. The second configuration (Figure 3b, feedback with voltage divider) the output voltage applied to the body of M1 is reduced by a voltage divider R1-R2. This is equivalent to reduction of  $g_{mb}$  in (4) by R2/(R1+R2). If  $(g_{ds2}+g_{ds})/k_{u2} \ll g_{mb} R2/(R1+R2)$ , the voltage gain is:

$$k_u = \frac{v_{out}}{v_{in}} \approx \frac{g_{mf}}{g_{mb}} \frac{(R1+R2)}{R2} \tag{5}$$

The voltage divider can be used to adjust the voltage gain to any value between the minimal gain (3) and the maximal gain that is obtained without direct feedback, i.e. when no output signal applied to the back gate of the input transistor. The maximal gain is given by

$$k_{umax} = k_{u2} \frac{g_{mf}}{g_{ds2} + g_{ds4}}. (6)$$

From (3) and (6) a general expression for the voltage gain, in terms of the minimal gain  $k_{umin}$  and maximal gain  $k_{umax}$ , is obtained

$$k_{u} = \frac{k_{umax}}{\frac{k_{umax}g_{mb}}{g_{mf}} \frac{R_{2}}{(R_{1}+R_{2})} + 1} = \frac{k_{umax}}{\frac{k_{umax}}{k_{umin}} \frac{R_{2}}{(R_{1}+R_{2})} + 1}$$

(7)

where it is assumed that the minimal voltage gain is given by (4) with sufficient accuracy.

As it will be shown in the next Section, the minimal gain of the amplifiers discussed in this paper is quite small. It is sufficient for the purpose for which these amplifiers were designed, but for other applications much higher gain may be needed. Higher gain can be obtained with the voltage divider R1-R2; however, reduction of the feedback signal by the divider results in reduced range of linearity of the response of the amplifier. When R1 is very large,  $k_u$  reaches  $k_{umax}$  and the linearization effect vanishes.

It is worth noting here that bulk-driven CMOS circuits, i.e. the circuits in which *ac* signals are applied to the bodies of the MOS devices, are well known [8 – 16]. However, in bulk CMOS technologies the linearization technique described here would not be possible. The body (either N-well or P-well) of a MOS device in bulk CMOS technologies is separated from the channel by the depletion region, not by BOX dielectric, and by *pn* junctions from the source and drain regions. This limits the range of voltages that can be applied to the body because reverse bias of the body vs. the channel, source and drain must be maintained.

### 3. Experimental results

# 3.1. The first amplifier

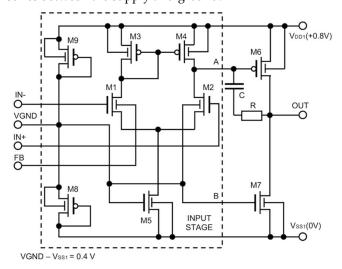

The first amplifier is shown in Figure 4. Its supply voltage is 0.8 V. Such a low supply voltage dictated the simplest OTA-type amplifier architecture, without more than three MOS devices in series between the supply and ground.

Figure 4. The first amplifier [21]

Detailed description of this amplifier, including layout and results of measurements (voltage gain, input offset, bandwidth, noise and power consumption) can be found in [21].

The input transistors M1 and M2 are located over P-wells isolated from p-type substrate by deep N-wells. Electrical contacts to the wells are located in "hybrid" regions where BOX has been removed (Figure 1). Deep N-wells are connected to V<sub>DD1</sub> (connection not shown in Figure 4). The voltages applied to the isolated P-wells, in particular output voltage applied to the P-well of M1, are always lower or equal to V<sub>DD</sub>. As a result, reverse bias of all *pn* junctions is maintained.

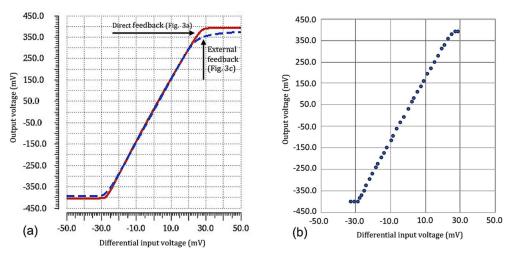

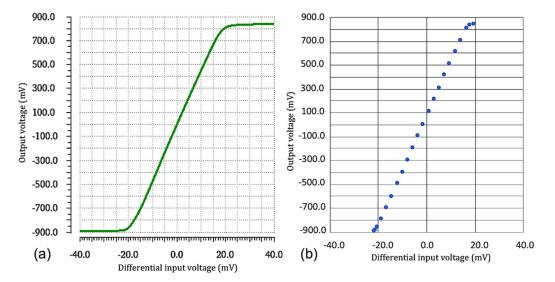

Figure 5a shows the simulated response of the amplifier. Simulations were performed with device models provided by the foundry. Curve labeled "Direct feedback" shows the response in the direct feedback configuration (Figure 3a). For comparison curve labeled "External feedback" shows response obtained in configuration with external linear negative feedback (Figure 3c). The resistances R1, R2 and the bias voltage  $V_{bias}$  have been chosen in such a way that both curves match for the differential input voltage  $V_{in}$  equal to zero. The simulated response (Figure 5a) has been confirmed experimentally. Figure 5b shows measured response in one of 50 fabricated and measured prototype chips.

**Figure 5.** Simulated in two configurations (a) and measured in the direct feedback configuration (b) response of the first amplifier

The direct feedback from the output to the body of the input transistor gives linear response extending almost "rail to rail".

Experimental results are in agreement with (4). Transconductances of M1 obtained from simulation for the differential input voltage equal to zero are:  $g_{mb} = 0.523 * 10^{-6} \, A/V$ ,  $g_{mf} = 7.64 * 10^{-6} \, A/V$ . This gives:  $k_u = 14.616 \, V/V$ . Measured voltage gain (average for 49 chips [21]) is  $14.5 \, V/V$ .

## 3.2. The second amplifier

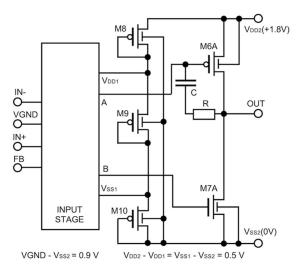

Figure 6 shows the schematic diagram of the second amplifier.

Figure 6. The second amplifier. The input stage is the same as in the first one, see Figure 4.

The design goal of the second amplifier (Figure 6) was to increase the maximum output amplitude to  $0.9~\rm V$ . This amplifier is similar to the first one. The input stage is the same. In the output stage transistors for  $1.8~\rm V$  maximum  $\rm V_{DS}$  and  $\rm V_{CS}$  were used. The supply voltage for the input stage is  $0.8~\rm V$ , as in the first amplifier. The voltage divider  $\rm M8-M10$  is the source of this voltage. Deep N-wells are connected to  $\rm V_{DD2}$  (+1.8 V) (connection not shown in Figure 6). Layout of the second amplifier (Figure 7) is very similar to the layout of the first one shown in [21].

Figure 7. Layout of the second amplifier.

The input transistors M1 – M2 (Figure 4) are visible at the upper left corner. Each transistor is divided into two connected in parallel in the common centroid configuration. Each of these four transistors is internally designed as four arrays of 100 relatively small (W/L = 10  $\mu$ m/90 nm) devices. All other transistors are also designed as arrays of smaller devices. The big M5 (Figure 4) device can be seen as three rows of arrays of smaller transistors in the bottom part of the layout. The empty space between these rows is needed to meet the layout density rules. The big rectangle in the upper right corner is a MOM

capacitor C. The divider (transistors M8 – M10) and the output transistors M6A and M7A can be seen in the upper right part of the layout.

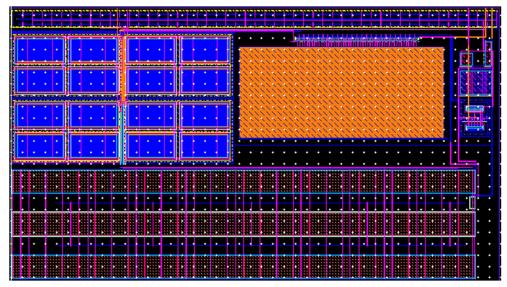

Figure 8 shows the simulated response of the second amplifier. Curve labeled "Direct feedback" shows the response in the direct feedback configuration (Figure 3a). For comparison curve labeled "External feedback" shows response obtained in configuration with external linear negative feedback (Figure 3c). The resistances R1, R2 and the bias voltage  $V_{bias}$  have been chosen in such a way that both curves match for the differential input voltage  $V_{iin}$  equal to zero. The simulated response (Figure 8a) has been confirmed experimentally. Figure 8b shows measured response in one of 25 fabricated and measured prototype chips.

Since the input stage is the same as in the first amplifier and the operating point of M1 and M2 for the differential input voltage equal to zero is the same, the measured voltage gain (average for 25 chips) for the differential input voltage equal to zero is almost the same: 15.5 V/V. However, linearity in the configuration with direct feedback is worse than in the case of the first amplifier. Deviation from linearity is clearly visible for the input voltages exceeding 20 mV. The reason is that the amplitude of output voltage applied to the back gate of M1 is higher than in the case of the first amplifier. As a result, the maximum back gate voltage  $V_{\text{CSb1}}$  of M1 reaches 970 mV – at the boundary between weak and moderate inversion.

**Figure 8.** Simulated in two configurations (a) and measured in the direct feedback configuration (b) response of the second amplifier.

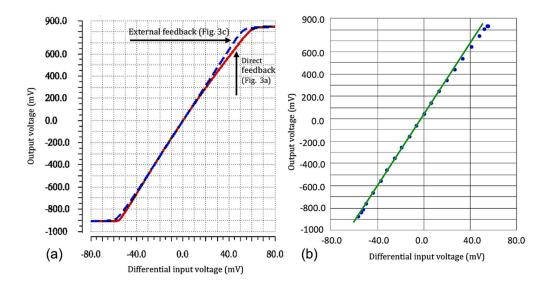

To improve linearity of the response of the second amplifier, the amplitude of the voltage applied to the back gate of M1 can be reduced by means of a voltage divider, as in configuration shown in Figure 3b. Figure 9a shows the result of simulation with R1 = 9.4 M $\Omega$  and R2 = 4.7 M $\Omega$  and Figure 9b shows measured results in a fabricated chip. Linearity in the input voltage range –15mV...+15 mV is almost perfect. As shown in previous Section, attenuation of the feedback signal by the voltage divider results in higher voltage gain. Simulated gain  $k_u$  = 46.19 V/V, measured gain  $k_u$  = 46.39 V/V, in quite good agreement with (5).

**Figure 9.** Simulated (a) and measured (b) response of the second amplifier in the configuration with voltage divider in the feedback loop (Figure 3b, R1 =  $9.4 \text{ M}\Omega$ , R2 =  $4.7 \text{ M}\Omega$ ).

Figure 9 shows that with increased gain the range of linearity of the response of the amplifier decreases. The response is no longer "almost rail to rail", as in the case of the first amplifier with direct feedback (Figure 5).

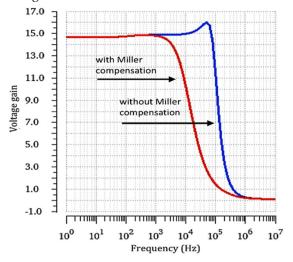

# 3.3. Frequency response

As shown in Section 2, the necessary condition of linearity is that the input transistors must work in weak inversion region for all combinations of the voltages at the front and back gates. This is acceptable for low power amplifiers but reduces achievable bandwidth. Additional problem with the frequency response is that the output resistance of the output stage together with the capacitance of the back gate creates low pass filter for the feedback signal. As a result, the amplitude of this signal decreases with frequency. This leads to a peak in the frequency response. It can be suppressed by appropriate Miller compensation. This is illustrated in Figure 10.

**Figure 10**. Simulated frequency response of the first amplifier (Figure 4) with Miller compensation and without it.

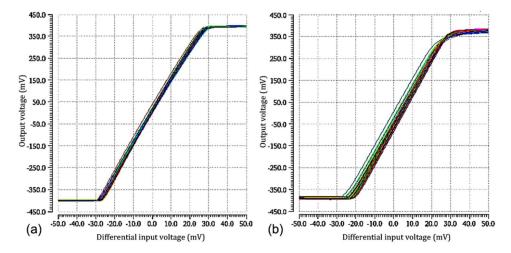

# 3.4. Variability

Direct feedback (Figure 3a) may result in reduction of variability of the amplifier in comparison with the same amplifier with external feedback loop (Figure 3c). Results of Monte Carlo simulations of the response of the first amplifier (N=100, nominal process corner, both process and mismatch variabilities included) are shown in Figure 11. While the nominal responses in both kinds of feedback loop (shown in Figure 5) are almost identical, variabilities are not. It can be seen (Figure 11) that statistical spread of the responses of the amplifier with direct feedback loop (Figure 3a) is noticeably lower than that of the amplifier with external feedback (Figure 3c).

**Figure 11**. Results of Monte Carlo simulation of the response of the first amplifier in the direct feedback loop configuration (a) and external feedback loop configuration (b). Both process and mismatch statistical variations included.

## 4. Discussion and conclusions

Since the input differential pair must work in weak inversion (i.e. low drain currents), the linearization technique discussed in this paper is a good technique for low power amplifiers. The first one (Section 3.1) consumes an average of 1  $\mu$ A only at 0.8 V supply voltage [21]. The second one consumes more: 58  $\mu$ A at 1.8 V supply voltage. Larger current consumption results from design of the output stage (Figure 6, larger devices M6A and M7A) and additional current consumption by the voltage divider (Figure 6, devices M8 – M10).

The advantages of this linearization technique include: very good linearity and simplicity. There are no additional devices in the case of direct feedback configuration (Figure 3a), and in particular no circuit components (e.g. resistors, as in the case of resistive degeneration) connected in series with the transistors in the input stage. As a result, this linearization technique is suitable for low voltage amplifiers. Reduction of variability may be an additional benefit. A voltage divider in the feedback loop (R1 – R2, Figure 3b) allows to achieve the desired voltage gain (equation (5)). These resistors can be either external or on chip. If one of them is variable (e.g. voltage-dependent), a variable gain amplifier is obtained. Of course, attenuation of the feedback signal by the voltage divider reduces the linearity range of the response of the amplifier.

Operating point in weak inversion of the input pair devices reduces achievable bandwidth. However, both amplifiers described in this paper were designed as front end amplifiers for acquisition of biological signals. In this particular application bandwidth extending from DC to several kHz is sufficient. As it has been shown in [21], not only linearity, but also low noise, and in particular low flicker noise can be achieved.

10 of 11

**Funding:** This work was supported by THINGS2DO, an international project co-funded by the European Commission (ENIAC grant agreement 621221) and Polish National Centre for Research and Development (agreement ENIAC C-2013-2/1/2014).

**Conflicts of Interest:** The author declares no conflict of interest.

### References

- Cathelin, A. Fully Depleted Silicon on Insulator Devices CMOS: The 28-nm Node Is the Perfect Technology for Analog, RF, mmW, and Mixed-Signal System-on-Chip Integration. *IEEE Solid-St. Circuits Magazine* 2017, 9, pp. 18–26. 10.1109/MSSC.2017.2745738.

- 2. Planes, N. *et al.* 28nm FDSOI Technology Platform for High-Speed Low-Voltage Digital Applications. In 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 2012; pp. 133-134. 10.1109/VLSIT.2012.6242497.

- 3. Sansen, W. Distortion in elementary transistor circuits. *IEEE Trans. Circuits Syst. II, Anal. and Dig. Signal Proc.* **1999**, 46, pp. 315-325. 10.1109/82.754864.

- 4. Zhang, H.; Sánchez-Sinencio, E. Linearization Techniques for CMOS Low Noise Amplifiers: A Tutorial. *IEEE Trans. Circuits Syst. I: Regular Papers* **2011**, 58, pp. 22-36. 10.1109/TCSI.2010.2055353.

- 5. Coppejans, P; Steyaert, M. Dynamic Biasing: a Low Power Linearisation Technique. In 29th European Solid-State Circuits Conference (ESSCIRC 2004), Estoril, Portugal, 2004; pp. 369-372. 10.1109/ESSCIRC.2003.1257149.

- Hernes, B.; Moldsvor, Ø; Sæther, T. A -80dB HD3 Opamp in 3.3V CMOS Technology using Tail Current Compensation. In 2001 IEEE International Symposium on Circuits and Systems (ISCAS 2001), Sydney, NSW, Australia, 2001, pp. 216-219. 10.1109/IS-CAS.2001.921829.

- 7. Barbieri, A; Pernici, S. A Differential Difference Amplifier with Dynamic Resistive Degeneration for MEMS Microphones. In 42nd European Solid-State Circuits Conference (ESSCIRC 2016), Lausanne, Switzerland, 2016; pp. 285-288. 10.1109/ESSCIRC.2016.7598298.

- 8. Popa, C.; Coada, D. A new linearization technique for a CMOS differential amplifier using bulk-driven weak inversion MOS transistors. In Int. Symp. on Signals, Circuits and Systems (SCS 2003), Iasi, Romania, 2003; pp. 589-592, 10.1109/SCS.2003.1227121.

- 9. Yodtean, A.; Isarasena, P.; Thanachayanont, A. 0.8-mW CMOS Bulk-Driven Linear Operational Transconductance Amplifier in 0.35-mm Technology. In 2010 IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur, Malaysia, 2010; pp. 784-787. 10.1109/APCCAS.2010.5774958.

- Zhang, L. et al. A Low-Voltage High Linear Body-Driven Operational Transconductance Amplifier and Its Applications. In 2007 Canadian Conference on Electrical and Computer Engineering, Vancouver, BC, Canada, 2007; pp. 534-537. 10.1109/CCECE.2007.139.

- 11. Khateb, F; Biolek, D; Khatib, N; Vávra, J. Utilizing the Bulk-driven Technique in Analog Circuit Design. In 13th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Vienna, Austria, 2010; pp. 16–19. 10.1109/DDECS.2010.5491827

- 12. Carrillo, J. M.; Duque-Carrillo, J. F.; Torelli, G. Design Considerations on CMOS Bulk-Driven Differential Input Stages. In 2012 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Seville, Spain, 2012; pp. 85-88. 10.1109/SMACD.2012.6339423.

- 13. Grech, I; Micallef, I; Azzopardi, G.; Debono, C. J. A low-voltage wide-input-range bulk-input CMOS OTA. *Analog Integr Circ Sig Proces* **2005**, 43, pp. 127-136. 10.1007/s10470-005-6786-1.

- 14. Raikos, G.; Vlassis, S. 0.8 V Bulk-driven variable gain amplifier. In 17th IEEE International Conference on Electronics, Circuits and Systems, Athens, Greece, 2010; pp. 343-346. 10.1109/ICECS.2010.5724524.

- Tai, C-F.; Lai, J-L.; Chen, R-J. Using Bulk-driven Technology Operate in Subthreshold Region to Design a Low Voltage and Low Current Operational Amplifier. In 2006 IEEE International Symposium on Consumer Electronics, Saint Petersburg, Russia, 2006; pp. 562-566. 10.1109/ISCE.2006.1689495.

- Rakús, M.; Stopjaková, V.; Daniel, A. Analysis of Bulk-Driven Technique for Low-Voltage IC Design in 130 nm CMOS Technology. In 15th International Conference on Emerging eLearning Technologies and Applications (ICETA), Starý Smokovec, Slovakia, 2017; pp. 385-390. 10.1109/ICETA.2017.8102522.

- 17. Yang, E.; Lehmann, T. High Gain Operational Amplifiers in 22 nm CMOS, In 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019. 10.1109/ISCAS.2019.8702381.

- 18. Harikumar, P.; Wikner, J. J.; Alvandpour, A. An ultra-low-voltage OTA in 28 nm UTBB FDSOI CMOS using forward body bias. In 2015 Nordic Circuits and Systems Conference (NORCAS), Oslo, Norway, 2015. 10.1109/NORCHIP.2015.7364416.

- 19. Harikumar, P.; Wikner, J. J.; Alvandpour, A. A fully-differential OTA in 28 nm UTBB FDSOI CMOS for PGA applications. In 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, Norway, 2015. 10.1109/ECCTD.2015.7300114.

- 20. Wołodźko, M; W. Kuźmicz. A low power input amplifier for bio-signal acquisition in 28 nm FDSOI technology. In 20th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Dresden, Germany, 2017; pp. 79-82. 10.1109/DDECS.2017.7934562.

- 21. Kuzmicz, W.; A Simple Ultra-Low Power Opamp in 22 nm FDSOI. In 26th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Rzeszów, Poland, 2019; pp. 167-170. 10.23919/MIXDES.2019.8787017.

11 of 11

22. El Ghouli, S. *et al.* Experimental g<sub>m</sub>/I<sub>D</sub> Invariance Assessment for Asymmetric Double-Gate FDSOI MOSFET. *IEEE Trans. Electron Devices* **2018**, 65, pp. 11–18. 10.1109/TED.2017.2772804.