*Article*

## Basic modifications of "floating" differential stages based on complementary field-effect transistors with a control p-n junction

Chumakov V.E.<sup>1</sup>, Prokopenko N.N.<sup>1</sup>, Pakhomov I.V.<sup>1</sup>, Titov A.E.<sup>2</sup>

<sup>1</sup> Don State Technical University, Rostov-on-Don, Russia

<sup>2</sup> South Federal University, Taganrog, Russia

\*E-mail: chumakov.dssa@mail.ru. ORCID: 0000-0002-3446-743X

**Abstract:** The circuitry of the summarized "floating" differential stages (FDS) based on complementary field-effect transistors with a control p-n junction (CJFET), intended for use in low-noise analog microcircuits, for example, operational amplifiers. The results of modeling the flow characteristics of one of the CJFET FDSs in the LTSpice XVII environment at low temperatures (down to -197 °C) and exposure to a neutron flux in the range of  $1\text{e}13 \div 1\text{e}15 \text{ n/cm}^2$  are presented.

**Keywords:** Analog microcircuit, differential stage, complementary field-effect transistors with control p-n junction, low temperatures, neutron flux

---

### 1. Introduction

One of the promising circuit solutions that have been used in low-noise Op-amps are "floating" differential stages [1], which have low sensitivity characteristics to changes in supply voltages and input common-mode signals. The FDS circuitry of this class has received further development in recent years in works [2-9].

The use of complementary JFETs, which are mastered in the framework of a number of modern technological processes [10,11], provides a low noise level and increased resistance of analog microcircuits to the effects of penetrating radiation. For many problems of analog circuitry, floating FDSs are promising not only on silicon JFETs, but also on JFETs based on SiC, GaN, GaAs transistors [12].

The purpose and novelty of this article is to consider the main properties of the new topologies JFet FDS [1-9], which are studied on the models of JFET transistors of corporation "Integral" (Minsk) and corporation "SPE" Pulsar "(Moscow).

## 2. Basic CJFET circuits for floating differential stages.

According to a number of publications [3-9,15-20], to date, more than 10 variants for constructing differential cascades of this FDS class have been developed.

The classic "floating" DS circuit in Fig. 2.1, as a system in the case, is implemented on two JFET microcircuits LSJ698 and LSK489 [1], which contain pairs of transistors with p-channel (LSJ698) and n-channel (LSK489). At the same time, a sufficiently stable static mode is provided over a wide temperature range.

Figure 2.1-Classical scheme of "floating" input DS on JFET chips LSJ689 [21] and LSK489 [22]

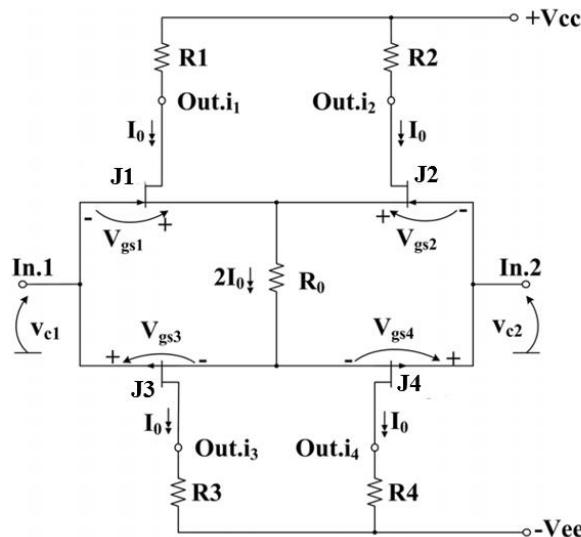

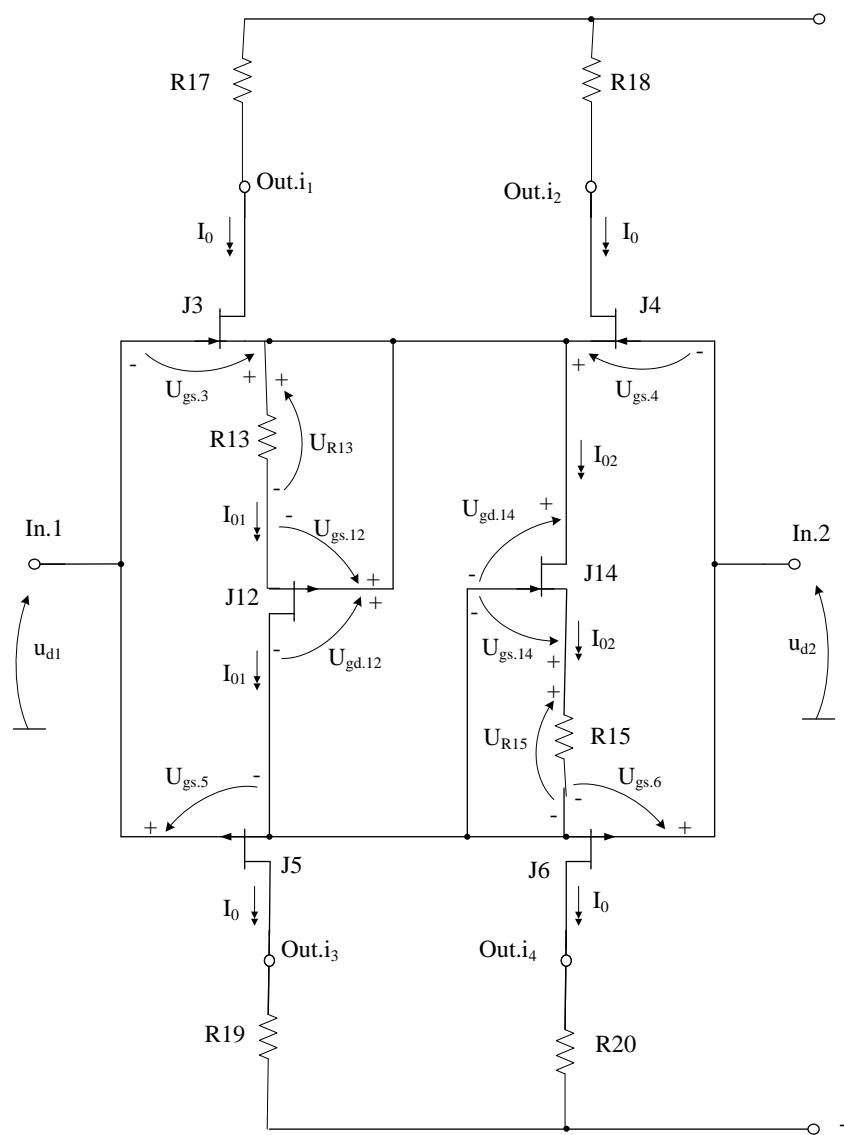

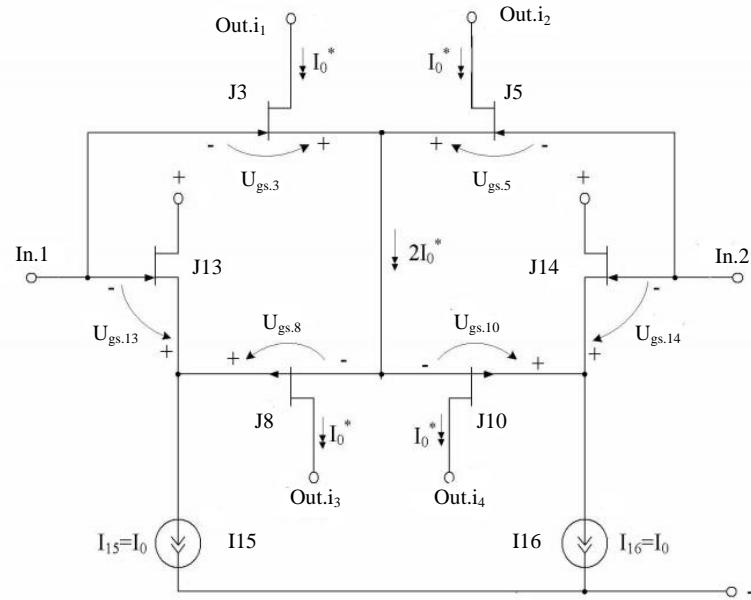

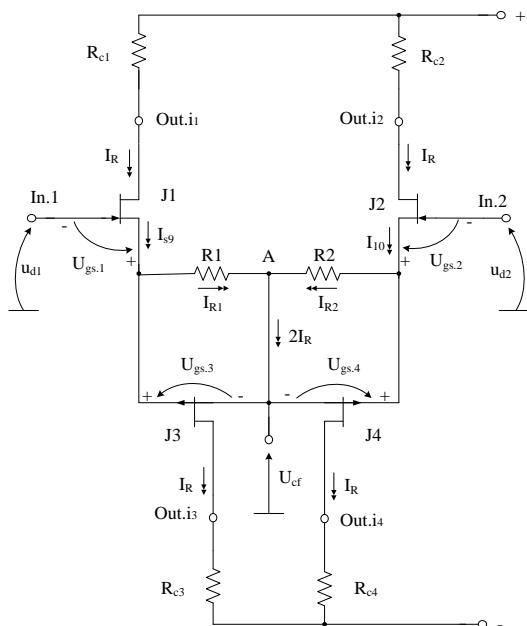

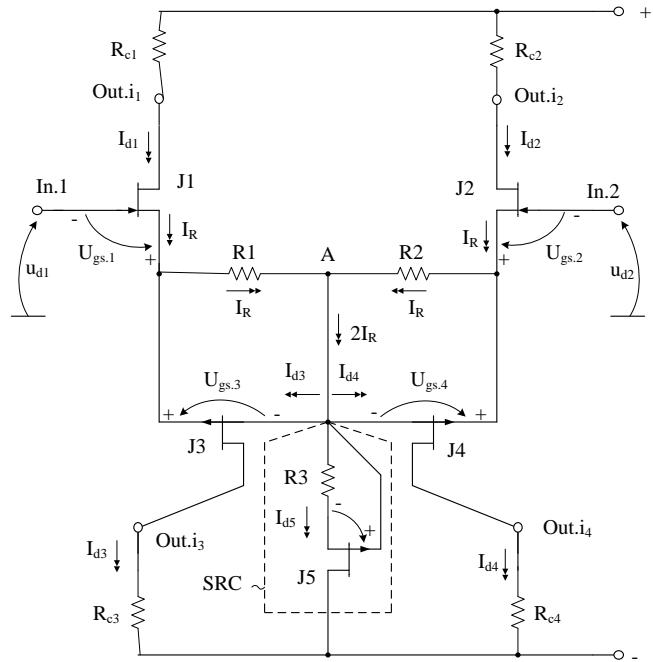

CJFET DS in Fig.2.2 [3] provides increased attenuation coefficients common-mode rejection ratio (Kcm) and suppression of noise on the power buses (Ksn).

Figure 2.2 - "Floating" DC with increased Kcm and Ksn

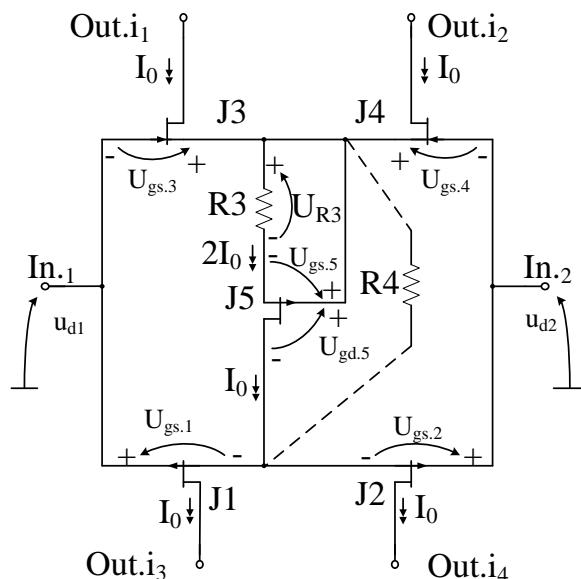

Figure 2.3 shows a CJFET multichannel DS class AB [7], which converts the input differential voltage into paraphase output currents in a wide range of input signals. This circuit is recommended for use in operational amplifiers with an increased maximum output voltage rise rate.

Figure 2.3 - CJFET multi-channel DS class AB

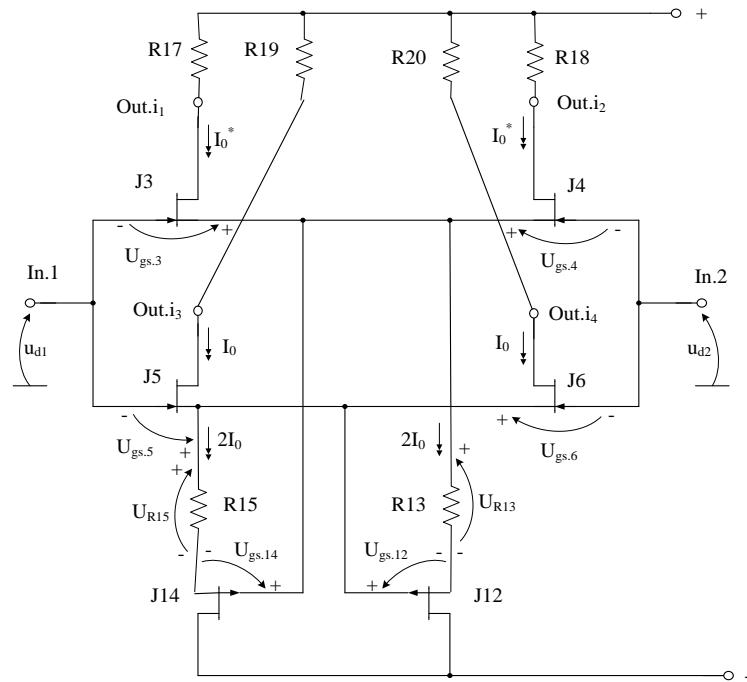

The DS circuit in Fig.2.4 [6,8,9] provides for wide-range adjustment of the voltage limiting the pass-through characteristic, which is important for constructing high-speed Op-amps. In addition, the DS in Fig. 2.4 in comparison with the DS in Fig. 2.2 has a doubled input capacitance.

Figure 2.4 - CJFET DS with reduced input capacitance

Figure 2.5 shows the DS [4] on CJFET transistors with a control pn-junction, which provides higher values of  $K_{cm}$  and  $K_{sn}$ , incl. at negative temperatures (down to  $-197^{\circ}\text{C}$ ) and providing the conversion of the input common mode voltage of the DS  $u_c$  into the currents of the DS outputs (Out.1, Out.2, Out.3, Out.4) in the range  $V_{in} = \pm 1 \text{ V}$ .

Figure 2.5 - DS [4] on complementary JFET field-effect transistors with increased attenuation of the input common mode signal

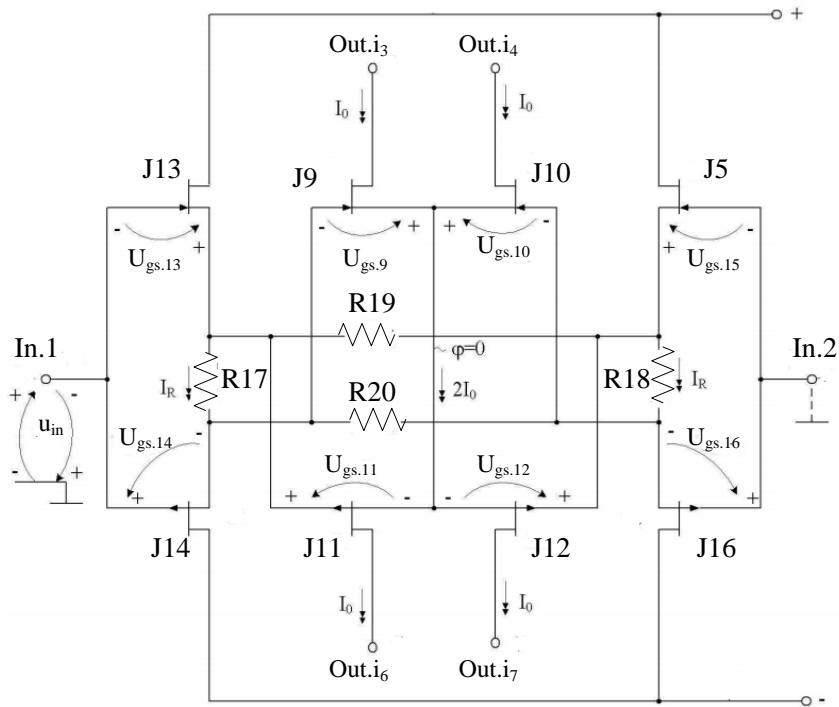

In Fig.2.6 DS [4] with increased stability of the static mode is presented, which provides, due to the rational choice of the numerical values R19, R20, insignificant changes in the currents in the resistor R20 over a wide temperature range. This allows you to stabilize the steepness of the DS and provide temperature stable values of its main static and dynamic parameters.

Figure 2.6-DS with increased stability of static modes [4]

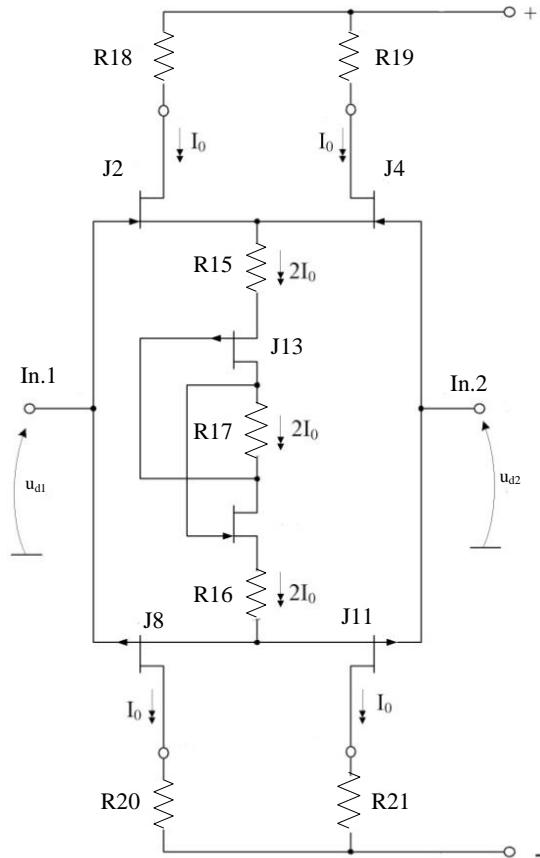

Figure 2.7-DS on complementary field-effect transistors with increased static mode stability [17]

In Fig.2.7 The DS [17] is presented, in which the static mode for the source currents of the field-effect transistors J2 and J4, as well as J8 and J11, is set by a static mode stabilization circuit integrated into a single functional node, including as a whole the input J2, J4, J8, J11 and additional field – effect transistors J13, J14 with a control pn - junction. This makes it possible to do without classical reference current sources and solve the problem of establishing the static mode of the remote control in an unconventional way.

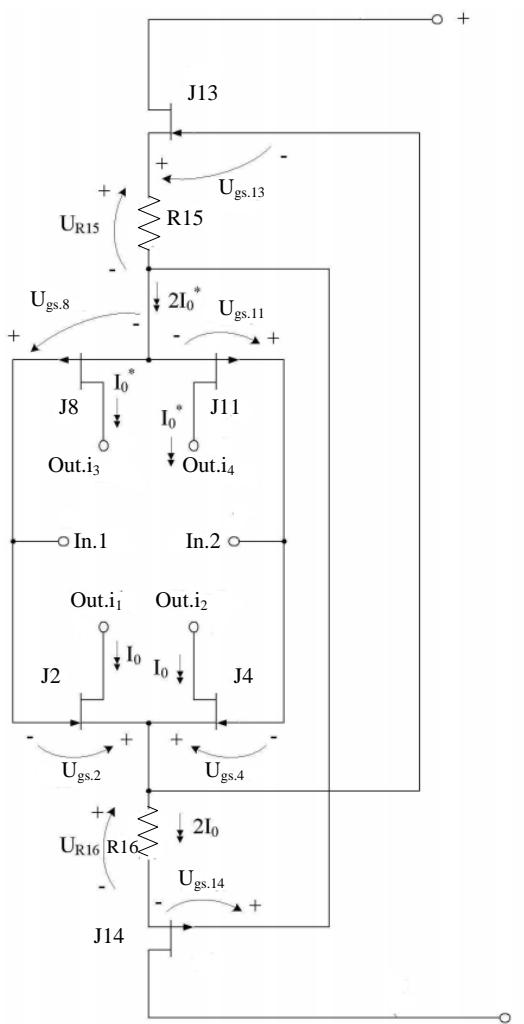

Figure 2.8-Input DS [18] on complementary field-effect transistors for operation at low temperatures

In Fig.2.8 The DS [18] is presented, in which the static mode for the source currents  $J_2, J_4, J_8$  and  $J_{11}$  of the input field-effect transistors, as well as the input field-effect transistors, is set by the DS static mode stabilization circuit integrated into a single functional node, which includes as a whole  $J_2, J_4, J_8, J_{11}$  input field-effect transistors, as well as  $J_{13}$  and  $J_{14}$  additional field-effect transistors with a control pn - junction. Thus, the static DC mode in Fig.2.8 [18] practically does not depend on the value of the input common-mode signal  $u_c = u_{c1} = u_{c2}$  and changes in the

bus voltages of power sources. This allows you to exclude the DC from the scheme in Fig.2.8 traditional reference current sources that negatively affect its many parameters.

(a)

(b)

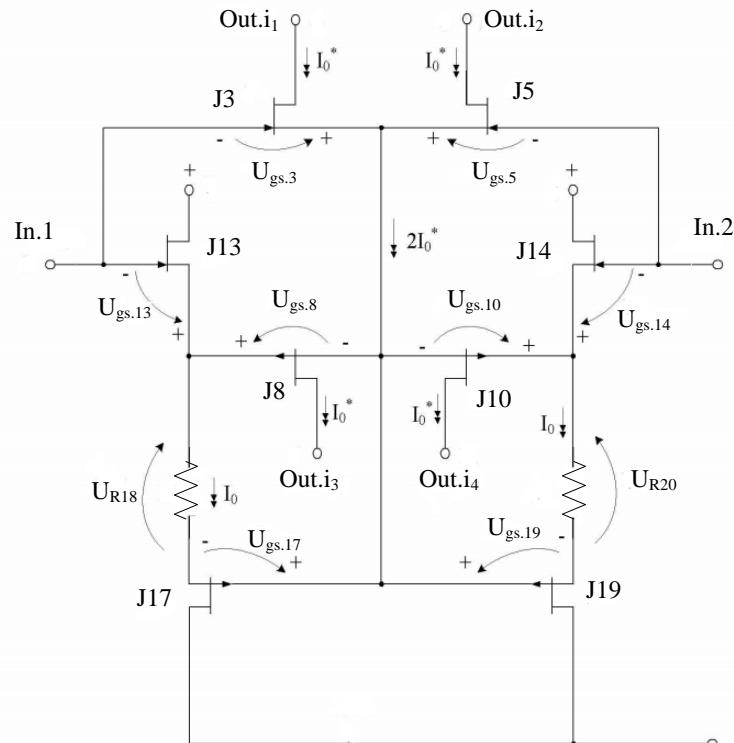

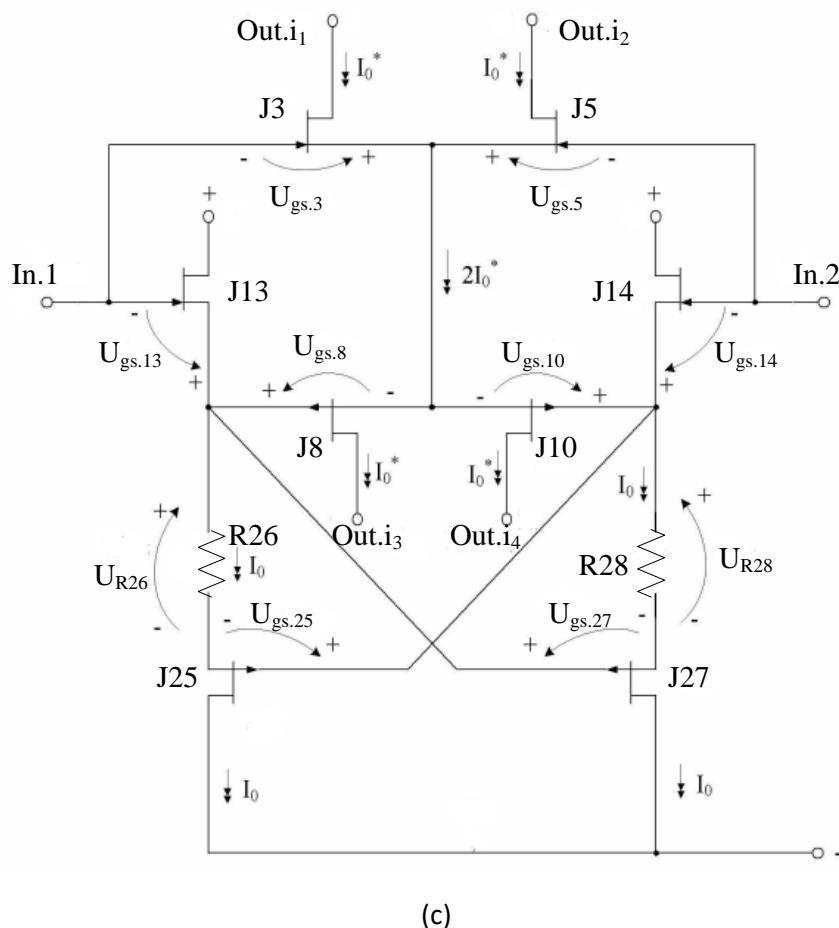

Figure 2.9-Modified DS class AB [19] on complementary field-effect transistors with a control pn – junction

In Fig.2.9 (a) shows a DS [19] operating in the class "AB" mode, when its maximum output currents exceed the static value  $I_0$  by 5÷7 times. Large voltage limitations of the DS flow characteristic allow you to create a circuit based on Fig.2.9 (a) High-speed CJFet operational amplifiers. Figure 2.9 (b) and Figure 2.9 (c) show special cases of DC construction in Figure 2.9 (a), in which auxiliary field-effect transistors J17, J19, J21, J23, J25, J27 are introduced, which improve other parameters of the basic circuit in Fig. 2.9 (a) - the attenuation coefficient of the input common mode signals, the suppression coefficient of interference on the power buses.

In Fig.2.10 DS is presented on complementary field-effect transistors with a control pn - junction of class AB with a variable voltage limiting the pass characteristic [20]. To set the set value of the DS limit voltage, see Fig.2.10 additional resistors R19 and R20 are introduced. The change in the resistance of these resistors significantly affects both the maximum output currents of the DS and the voltage limiting its flow characteristics. This effect is realized both at room and cryogenic temperatures.

Fig. 2. 10-DS on complementary field-effect transistors with a class AB control pn junction with a variable voltage of the pass-through characteristic limitation [20]

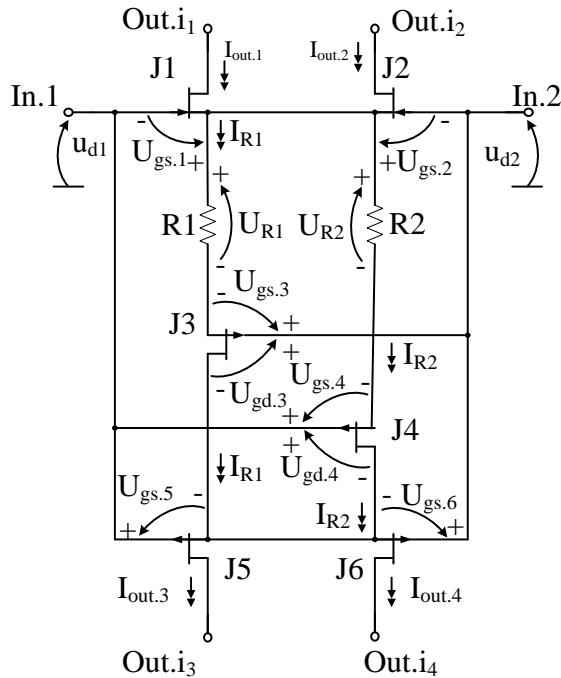

### 3. Study of FS CJFet differential cascades with reduced input capacitance

In contrast to the well-known "floating" FS [1], the input capacitances of the gate-drain transistors J1, J2 are reduced by half in the scheme of Fig. 3.1 [16]. The current outputs of the circuit in Fig. 5 are matched with the positive (Out. i<sub>1</sub>, Out.i<sub>2</sub>) and negative (Out. i<sub>3</sub>, Out.i<sub>4</sub>) buses of the power supply. They can be connected to intermediate "bent" cascodes [1] for further amplification and conversion of signals, for example, into an Op-amp.

In the proposed FS in Fig. 5, the static currents of the field-effect transistors J1, J2 are determined by the following equations:

$$I_{s1} = \frac{U_{gs.3}}{R_1} = I_{R1} = I_R, \quad (1)$$

$$I_{s2} = \frac{U_{gs.4}}{R_2} = I_{R2} = I_R, \quad (2)$$

$$I_{d.3} = I_{s3} = I_R = I_{d4} = I_{s.4}, \quad (3)$$

$$2I_R = I_{R1} + I_{R2}, \quad (4)$$

where  $I_{si}$  is the source current of the  $i$ -th field-effect transistor;

$U_{gs.3}, U_{gs.4}$  – the gate-source voltage of the corresponding input field-effect transistors J3, J4 at the operating point at a source current equal to  $I_R$ .

Thus, by selecting the resistances of the resistors R1, R2 with the known drain-gate characteristics of JFET, the specified static current mode of all FS field-effect transistors is provided.

A distinctive feature of FS Fig. 3.1 is that its static mode does not depend on the value of the input common mode signal and changes in supply voltages.

If a positive input voltage of the is applied to input 1 relative to input 2, this causes an increase in the current through the input field-effect transistors J1, J4 and a decrease in the drain current of the field-effect transistors J2, J3.

Figure 3.1 Circuit of a "floating" DC with a reduced input capacitance [16]

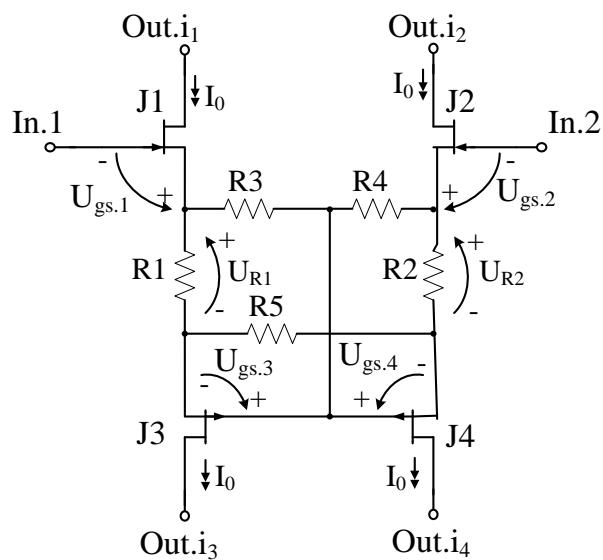

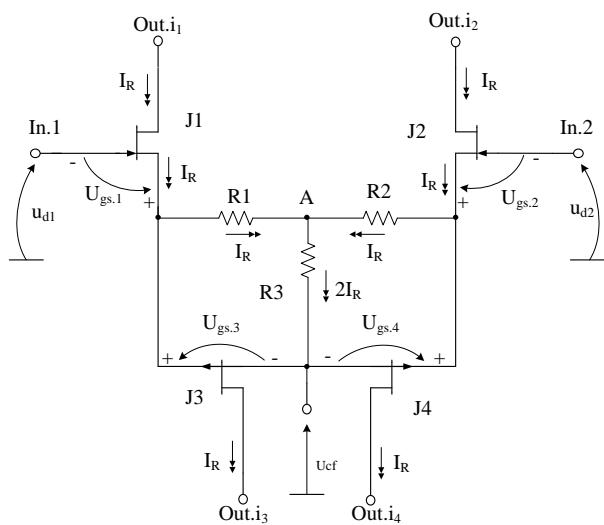

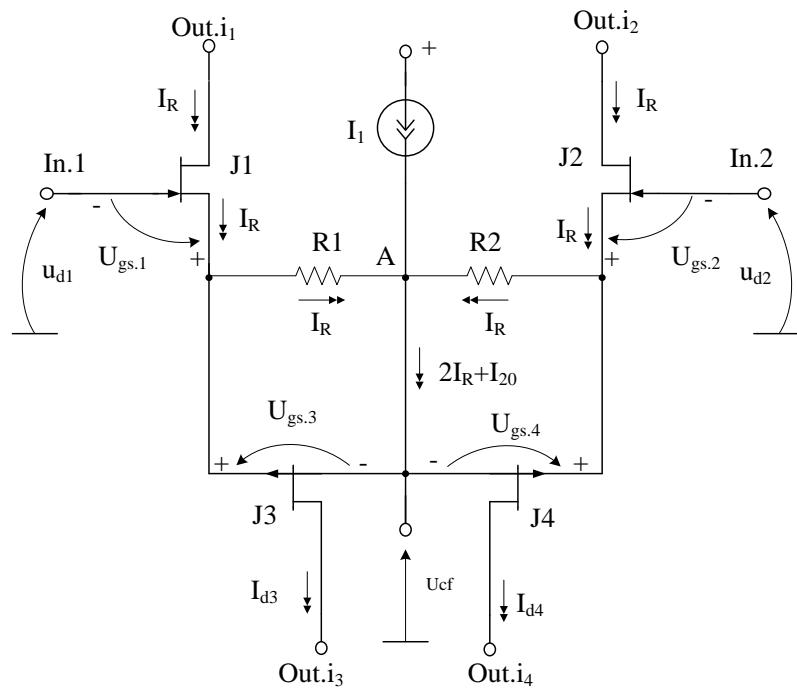

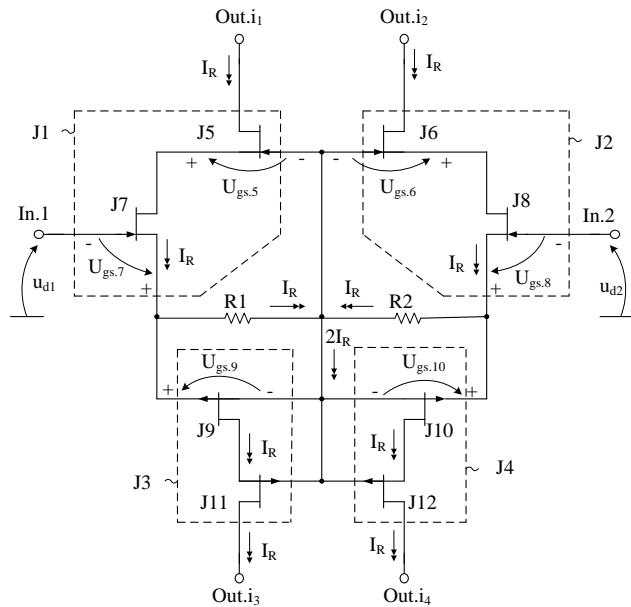

Figure 3.2, Figure 3.3 show other FS modifications that extend the properties of the basic circuit in Figure 3.1.

Figure 3.2 First modification of CJFET FS

Figure 3.3 The second modification of the proposed in [16] FS

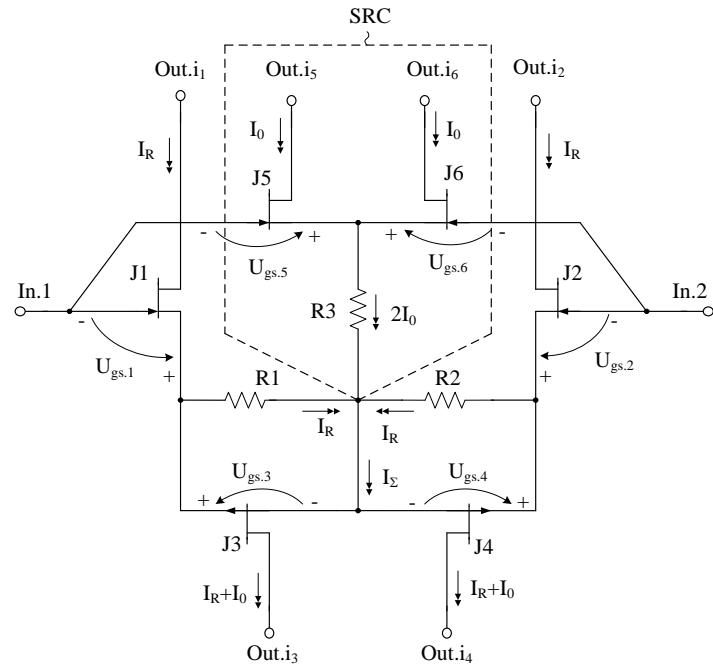

The FS circuit in Figure 3.4 has 4 current outputs (Out.  $i_1$ , Out.  $i_2$ , Out.  $i_5$ , Out.  $i_6$ ) aligned with the positive bus of the power supply, as well as an increased steepness of converting the FC input voltage into the output currents of Out.  $i_5$ , Out.  $i_6$ .

Figure 3.4 The third modification of the proposed in [16] FS

In the FS circuit in Figure 3.5, the set values of the drain currents of the input field-effect transistors J3, J4 are also set by the resistor R3.

Figure 3.5 The fourth modification of the proposed in [16] FS

The peculiarity of the FS circuit in Fig. 3.6 is that here it has increased output resistances for all current outputs. This is achieved through the use of staged composite transistors and allows you to obtain higher values of the maximum voltage gain in the Op-amp on the basis of the circuit Fig. 3.6.

Figure 3.6-Diagram of the proposed FS with increased output resistances in [16]

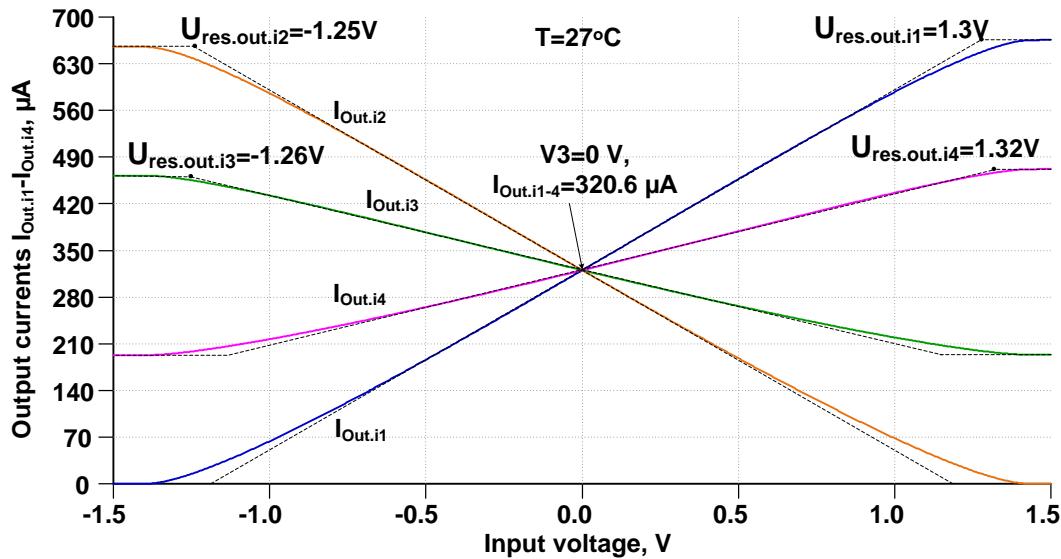

Figure 3.7 shows the pass-through characteristics of CJFet FS Figure 3.1 in the LTspice environment on JFET transistor models of Integral SPE (Minsk), at  $t=27^\circ\text{C}$ ,  $R1=R2=1\text{k}$  and measuring the input voltage in the range  $V= -1.5 \div 1.5 \text{ V}$ .

Figure 3.7 CJFet FS flow characteristics Figure 3.1 at  $t=27^\circ\text{C}$

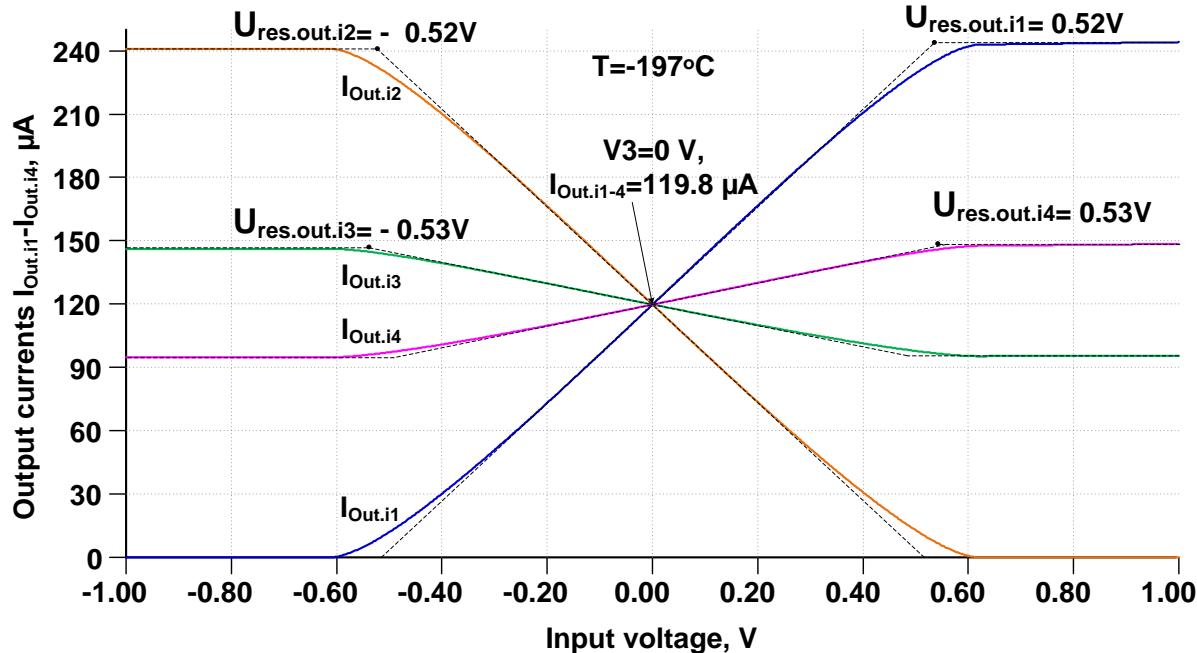

The flow characteristics of CJFet FS Fig. 3.1 at negative temperatures " $t= -197^\circ\text{C}$ ",  $R1=R2=1 \text{ k}$  and measuring the input voltage in the range  $V= -1.5 \div 1.5 \text{ V}$  are shown in Fig. 3.8.

Figure 3.8 CJFet FS flow characteristics at  $t=-197^\circ\text{C}$

The simulation results (Fig. 3.7, Fig. 3.8) show that on the basis of the FS proposed in [16], it is possible to implement a wide range of pass characteristics with different numerical values of the limiting voltage  $U_1$  for the first and second, as well

as the third and fourth current outputs. This allows you to purposefully select the numerical values of the  $U_1$  when designing differential and multidifferential operational amplifiers with a given speed in the large signal mode. Thus, the maximum rate of rise of the output voltage of the Op-amp with the classical architecture [13] is determined by the formula  $SR=2nf_1U_1$ , where  $f_1$  is the frequency of the unit gain of the corrected Op-amp;  $U_1$  is the voltage limiting the pass characteristic of the input stage.

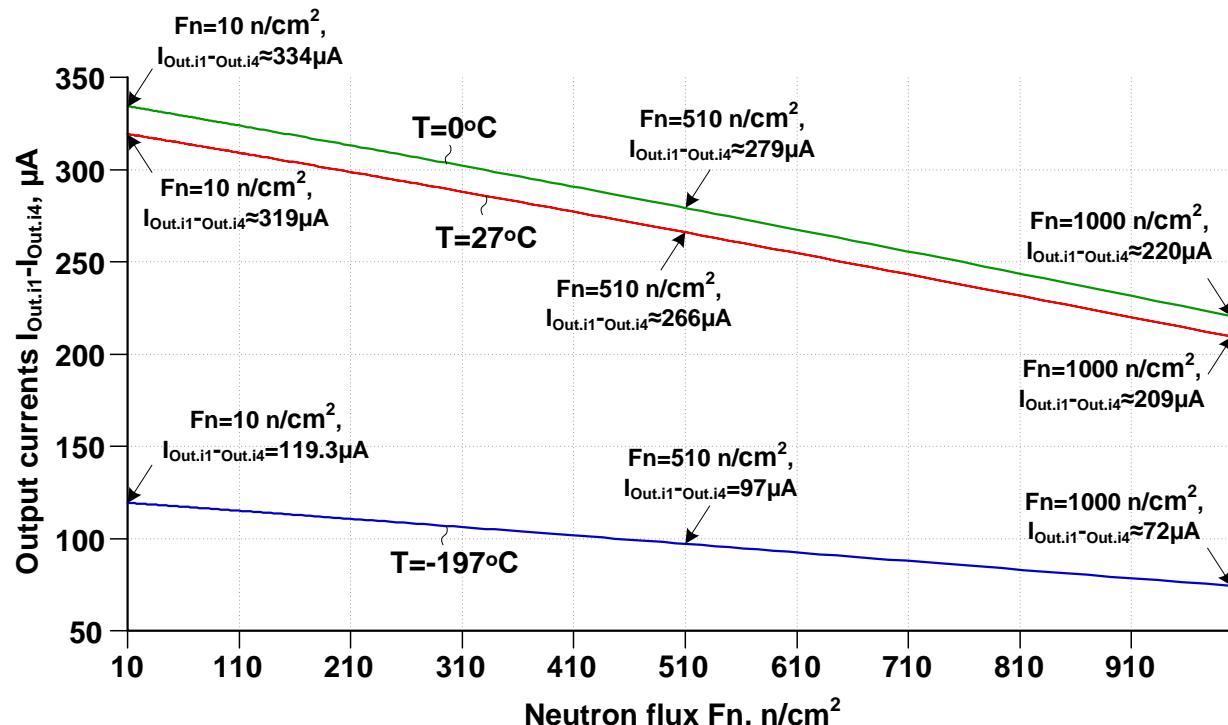

Figure 3.9 shows the dependence of the output currents of CJFet FS in Figure 3.1 on the neutron flux in the range  $F_n=1e13 \div 1e15 \text{ n/cm}^2$  at resistances  $R_1=R_2=1 \text{ k}$ . At the same time, well-known models with JFet were used [14].

Figure 3.9 Dependence of the output currents of CJFet FS Fig. 3.7 and Fig. 3.8 on the neutron flux in the range  $F_n=1e13 \div 1e15 \text{ n/cm}^2$

## Conclusion

The circuit design of "floating" CJFET differential stages is generalized, which is recommended for the design of analog chips with a low noise level and relatively high resistance to radiation and low temperatures. At the same time, CJFET of various microelectronic companies can be used, including CJFet of corporation "Integral" (Minsk) and corporation "SPE" Pulsar "(Moscow).

The research has been carried out at the expense of the Grant of the Russian Science Foundation (project No. 18-79-10109).

## References

1. Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17. URL: [http://www.linearsystems.com/lsdata/others/Headphone\\_Amplifier\\_Evaluation\\_Board.pdf](http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf)

2. Patent No. 2688225 Russian Federation, IPC H03F 3/34, H03F 3/45. Differential amplifier on complementary field-effect transistors with a control p-n junction: No. 2018126843/08; application No. 23.07.2018; publ. 21.05.2019, Bull. No. 15 / Bugakova A.V., Zhuk A. A., Prokopenko N. N.; applicant DSTU (in Russian).

3. Patent No. 2710296 Russian Federation, IPC H03F 1/00, H03F 3/34. Differential stage on complementary MOSFET field-effect transistors with increased attenuation of the input common-mode signal: No. 2019131161/08; application No. 03.10.2019; publ. 25.12.2019, Bull. No. 36 / Prokopenko N. N., Zhuk A. A., Bugakova A.V., Pahomov I. V.; applicant DSTU (in Russian).

4. Differential stage on complementary field-effect transistors with increased temperature stability of the static mode: application for patent of the Russian Federation No. 2020134402; application 20.10.2020 / Prokopenko N. N., Zhuk A. A., Budyakov P. S., Chumakov V. E.; applicant DSTU (in Russian).

5. Patent No. 2724975 Russian Federation, IPC H03F 1/00, H03F 3/34. Differential input voltage converter with paraphase current outputs based on complementary field-effect transistors with a control P-N junction: No. 2020110731/08; application No. 13.03.2020; publ. 29.06.2020, Bull. No. 19 / Bugakova A.V., Titov A. E., Prokopenko N. N., Kleymenkin D. V.; applicant DSTU (in Russian).

6. Patent No. 2736412 Russian Federation, IPC H03F 3/34, H03F 3/45. Differential amplifier based on complementary field-effect transistors with a control p-n junction: No. 2020115040/08; application No. 29.04.2020; publ. 17.11.2020, Bull. No. 32 / Bugakova A.V., Prokopenko N. N., Dvornikov O. V., Drozdov D. G.; applicant DSTU (in Russian).

7. Patent No. 2736085 Russian Federation, IPC H03F 3/45. Multichannel converter of differential voltage to paraphase output currents on complementary field-effect transistors with a control p-n junction: No. 2020119006; application No. 09.06.2020; publ. 11.20, Bull. No. 32 / Bugakova A.V., Kuznetsov D. V., Prokopenko N. N., Zhuk A. A.; applicant DSTU (in Russian).

8. Patent No. 2679970 Russian Federation, IPC H03F 3/45. Differential amplifier on complementary field-effect transistors with controlled voltage limiting of the pass characteristic: No. 2018121088/08; application No. 07.06.2018; publ. 14.02.2019, Bull. No. 5 / Bugakova A.V., Prokopenko N. N., Dvornikov O. V.; applicant DSTU (in Russian).

9. Patent No. 2684473 Russian Federation, IPC H03F 3/34. Differential cascade on complementary field-effect transistors: No. 2018126846/08; application No.

23.07.2018; publ. 09.04.2019, Bull. No. 10 / Bugakova A.V., Prokopenko N. N., Dvornikov O. V., Budyakov P. S.; applicant DSTU(in Russian).

10. Technological and devices modeling of complementary JFETs over a wide temperature range / Drozdov D.G., Prokopenko N.N., Savchenko E.M., Dukanov P.A., Rodin V.G., Grushin A.I. // Microelectronics Journal, Vol. 105, Nov. 2020, 104911. <https://doi.org/10.1016/j.mejo.2020.104911>

11. Comparison of Complementary JFET Parameters on Technological Processes of JSC "integral" (Minsk) and JSC "sPE "pulsar" (Moscow) at Low Temperatures / O.V. Dvornikov, V.L. Dziatlau, V.A. Tchekhovski, N.N. Prokopenko, D.G. Drozdov, E.M. Savchenko // 2020 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, Russia, 2020, pp. 1-4, DOI: 10.1109/MWENT47943.2020.9067463

12. M. Kaneko and T. Kimoto, "High-Temperature Operation of n- and p-Channel JFETs Fabricated by Ion Implantation Into a High-Purity Semi-Insulating SiC Substrate," in IEEE Electron Device Letters, vol. 39, no. 5, pp. 723-726, May 2018, doi: 10.1109/LED.2018.2822261.

13. N.N. Prokopenko, A.S. Budyakov, "Architecture and Circuitry of the High-Speed Operational Amplifiers", Shakhty: SRSUES, 2006, 232 p. (in Russian)

14. O.V. Dvornikov, V.L. Dziatlau, V.A. Tchekhovski, N.N. Prokopenko, A.V. Bugakova, "Features of JFET Computer Models in Microcurrent Mode on Exposure to Low Temperatures and Neutron Fluence", Proceedings of 18th IEEE East-West Design & Test Symposium (EWDTS-2020), September 4-7, 2020, Varna, Bulgaria, P.59-63 DOI: 10.1109/EWDTS50664.2020.9224827.

15. N. Prokopenko, A. Zhuk and I. Pakhomov, "Floating Complementary JFET Differential Stage with Increased Rejection of input Common Mode Signal and Power-Supply Noises," 2020 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, Russia, 2020, pp. 1-4, doi: 10.1109/MWENT47943.2020.9067377.

16. Pat. 2736412 Russian Federation, IPC H03F 3/34, H03F 3/45. Differential amplifier based on complementary field-effect transistors with a control p-n junction / Bugakova A.V., Prokopenko N. N., Dvornikov O. V., Drozdov D. G.; applicant and patent holder of the Don State Technical University. – No. 2020115040; application No. 29.04.2020; publ. 17.11.2020, Bull. No. 32. - 23 p (in Russian).

17. Pat. 2710930 Russian Federation, IPC H03F 3/34, H03F 3/45. Differential amplifier on complementary field-effect transistors with increased static mode stability / Prokopenko N. N., Budyakov P. S., Pakhomov I. V.; applicant and patent holder of the Don State Technical University. – No. 2019122165/08; application form 15.07.2019; publ. 14.01.2020, Bull. no. 2. – 17pp.: ill. (a. 798) (in Russian).

18. Pat. 2712416 Russian Federation, IPC H03F 3/34, H03F 3/45. Input differential cascade on complementary field-effect transistors for operation at low temperatures / Prokopenko N. N., Dvornikov O. V., Pakhomov I. V.; applicant and patent holder of the Don State Technical University. – No. 2019122270; application No. 16.07.2019; publ. 28.01.2020, Bull. No. 2. – 17pp.: ill. (a. 913) (in Russian).

19. Pat. 2710847 Russian Federation, IPC H03F 3/34, H03F 3/26. Differential cascade of class ab on complementary field-effect transistors with a control p-n junction for operation in low temperature conditions / Prokopenko N. N., Drozdov D. G., Zhuk A. A.; applicant and patent holder of the Don State Technical University. – No. 2019126326; application 21.08.2019; publ. 14.01.2020, Bull. no. 2. – 18pp.: ill. (a. 915) (in Russian).

20. Pat. 2712414 Russian Federation, IPC H03F 3/34, H03F 3/45. Differential stage on complementary field-effect transistors with a control p-n junction of class ab with a variable voltage limiting the pass characteristic/ Prokopenko N. N., Bugakova A.V., Budyakov P. S.; applicant and patent holder of the Don State Technical University. – No. 2019126310; application 21.08.2019; publ. 28.01.2020, Bull. no. 4. – 15pp.: ill. (a. 918) (in Russian).

21. Bob Cordell, “Linear Systems LSJ689 Application Note”, URL: [http://www.linearsystems.com/lsdata/appnotes/LSJ689\\_P-Channel%20Dual%20JFETs.pdf](http://www.linearsystems.com/lsdata/appnotes/LSJ689_P-Channel%20Dual%20JFETs.pdf)

22. Bob Cordell, “LSK489 Application Note”, URL: [http://www.linearsystems.com/lsdata/other/LSK489\\_Application\\_Note.pdf](http://www.linearsystems.com/lsdata/other/LSK489_Application_Note.pdf)