## Article

# An 18.8–33.9-GHz, 2.26-mW Current-Reuse Injection-Locked Frequency Divider for Radar Sensor Applications

Kwang-Il Oh <sup>1</sup>, Goo-Han Ko <sup>1</sup>, Jeong-Geun Kim <sup>2</sup> and Donghyun Baek <sup>1,\*</sup>

<sup>1</sup> Microwave Embedded Circuit & System (MECAS) Lab., School of Electrical Engineering, Chung-Ang University, 84 Heukseok, Dongjacket, Seoul 06974, Korea; dhrhkddlf123@cau.ac.kr (K.-I.O.), rngks79@cau.ac.kr (G.-H.K.)

<sup>2</sup> Integrated Radar Lab., Department of Electronic Engineering, KwangWoon University, 20 Gwangun, Nowon, Seoul 01897, Korea; junggun@kw.ac.kr

\* Correspondence: dhbaek@cau.ac.kr; Tel.: +82-02-820-5828

**Abstract:** An 18.8–33.9-GHz, 2.26-mW current-reuse (CR) injection-locked frequency divider (ILFD) for radar sensor applications is presented in this paper. A fourth-order resonator is designed using a transformer with a distributed inductor for wideband operating of the ILFD. The CR core is employed to reduce the power consumption compared to conventional cross-coupled pair ILFDs. The targeted input center frequency is 24 GHz for radar application. The self-oscillated frequency of the proposed CR-ILFD is 14.08 GHz. The input frequency locking range is from 18.8 to 33.8 GHz (57%) at an injection power of 0 dBm without a capacitor bank or varactors. The proposed CR-ILFD consumes 2.26 mW of power from a 1-V supply voltage. The entire die size is 0.75 mm × 0.45 mm. This CR-ILFD is implemented in a 65-nm CMOS technology.

**Keywords:** Current-reuse, injection-locked frequency divider, radar sensor, wideband

## 1. Introduction

Recently, the demand for radar sensors is rapidly increasing with the development of the Internet of Things (IoT) industry and the autonomous vehicle industry. The CMOS radar is characterized by various operating methods such as doppler, frequency-modulated continuous wave (FMCW), and (continuous-wave) CW. In the doppler radar, a low frequency to millimeter-wave (mm-Wave) must be used to acquire a two-dimensional image through synthetic aperture radar (SAR). Bandwidths of 500 MHz or more are used to obtain high-resolution images [1], [2]. In addition, wideband performance is very important in frequency-modulated continuous wave (FMCW) radars because wideband chirp is directly related to the high-resolution distance information [3]. Therefore, the wideband performance of the signal generator, the core of the sensor, is required [4], [5].

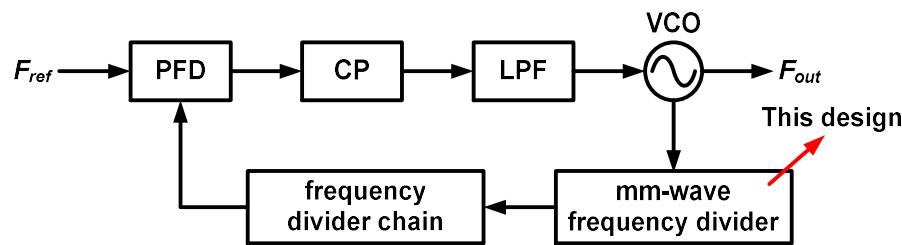

Generally, the performance of the phase-locked loop (PLL) in the signal generator must be concerned to obtain low noise mm-Wave signals. Figure 1 shows the block diagram of conventional PLL structure that consist of a phase-frequency detector (PFD), charge pump (CP), low-pass filter (LPF), voltage-controlled oscillator (VCO) and frequency divider. The key blocks that determine the specification of the PLL in the mm-Wave band are VCO [6], [7] and frequency divider [8]. The mm-Wave frequency divider should operate at high speed and should have a wide operating range for applying the wideband sensor applications.

Frequency dividers are designed as the current mode logic (CML) divider, regenerative divider, and LC oscillator-based injection-locked frequency divider (ILFD). The CML divider is a combination of two flip-flops that perform simple logical operations [9–12]. Generally, CML dividers have a wide operating range and occupy a small chip area with no inductor design. However, CML dividers suffer from large power consumption,

**Figure 1.** Conventional phase-locked loop with mm-Wave frequency divider.

limited maximum operation frequency, and process, voltage, and temperature (PVT) variation at the mm-Wave. To address these shortcomings, tunable self-resonant circuit [9], dynamic latches with load modulation [10,11], and additional calibration circuits [12] have been studied. However, these still consume large powers of 4.8 [11], and 6.2 mW [12], respectively. The regenerative divider and ILFD are also popular frequency dividers. These two types of frequency dividers are LC oscillator-based circuits and both of them are quite similar. The regenerative divider comprises an LC-based band pass filter (BPF) and active type mixer [13–15]. The active type of mixer consumes power and take over the role of  $-g_m$  core. Conversely, the ILFD comprises an LC-based BPF,  $-g_m$  core, and passive type mixer that does not consume power. Therefore, regenerative dividers consume more power than ILFDs and are not generally used for mm-Wave applications because of the influence of many parasitic capacitors of the active of type mixer such as the Gilbert cell. The even-harmonic mixer [14] and digital-assisted circuit [15] are employed to widen the locking ranges of the regenerative divider. Their locking ranges are 33% and 57.4%, respectively. However, the highest input frequencies are limited to 18.4 and 14.8 GHz, consuming 10.8 and 12 mW power, respectively.

The most attractive mm-Wave frequency divider is the LC oscillator-based ILFD. The reasons for its high popularity are as follows. First, the ILFD self-oscillates when there is no input signal applied. It is possible to obtain a large output signal with a small input signal using the oscillator-based operation. Second, because of LC resonator, the ILFD is advantageous for operation at the mm-Wave band. Finally, because the ILFD uses a passive type of mixer, it consumes less power than regenerative and CML dividers. However, the disadvantage is that the locking range is narrow because of high quality factor (Q) LC resonator. Several studies are being conducted to widen the locking range of ILFD [16–18]. The forward-body-bias techniques [16,17] are some of the effective ways of increasing the gain of the mixer and extending the locking range. Although the ILFD with the forward-body-bias techniques have a wide locking range of 90% in [17], there are several reasons why this technique is impractical in mm-Wave synthesizers. First, if a positive bias is applied to the body of an n-channel metal-oxide-semiconductor field-effect transistor (MOSFET), the leakage current cannot be ignored, and the possibility of a large diffusion current flow because of forward-bias increases. Second, the power of the harmonic signal increases because of non-linearity in devices. Applying an injection signal with an edge frequency in the locked range can make it difficult to distinguish the power difference between the output and harmonic signals. Finally, an additional circuit may be required to control the harmonic power, which can increase the circuit complexity and power consumption. The dual-resonance resonator is also considered as a suitable technique [18]. This ILFD has a locking range of 71.46%, however, it requires external bias control and has a small output power. Moreover, when a -3-dBm injection power is applied, an unlocking part occurs in the locking range.

In this paper, a low power and wide locking range LC oscillator-based current-reuse (CR) ILFD using a fourth-order resonator with the distributed inductor is proposed. The CR technique is employed to reduce power consumption. This paper is organized as

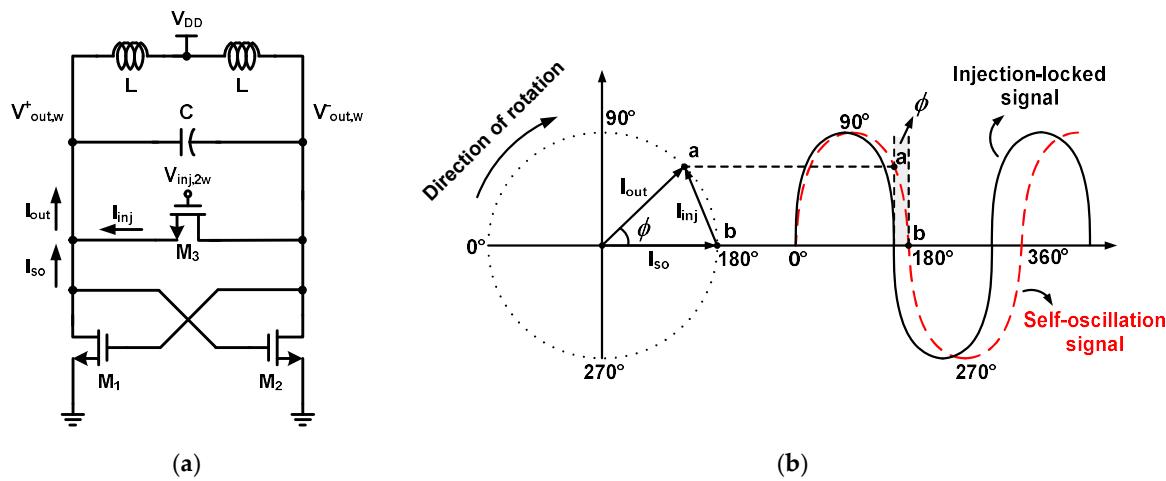

**Figure 2.** (a) Schematic of the conventional cross-coupled pair ILFD with second-order resonator and (b) phasor diagram for the basic principle of the conventional ILFD.

follows. Section 2 presents an analysis of the ILFD locking range. The limitations of the maximum locking range and harmonic issues are also presented. Section 3 presents the circuit design of the proposed CR-ILFD including the modeling of the transformer and design flow chart. The measurement results are shown in Section 4. Finally, conclusions are organized in Section 5.

## 2. Locking Range Analysis of ILFD

Figure 2(a) shows a schematic of the conventional cross-coupled pair ILFD with a second-order resonator. This ILFD consists of an NMOS cross-coupled pair (M<sub>1</sub>, M<sub>2</sub>), injection switch (M<sub>3</sub>) and LC resonator. The ILFD self-oscillates if there is no injection signal at the gate of M<sub>3</sub>. Biasing the injection signal of V<sub>inj,2w</sub> at the gate of M<sub>3</sub>, the ILFD outputs V<sub>out,w</sub> and V<sub>out,w'</sub>. When the frequency of the output signal is exactly half the frequency of the injection signal, it is referred to as 'locking'. To easily understand the locking operation, the current is classified into three types, namely, I<sub>so</sub>, I<sub>inj</sub>, and I<sub>out</sub>. I<sub>so</sub> represents the self-oscillation current flowing through the core when the ILFD self-oscillates without an injection signal. I<sub>inj</sub> is the injection current flowing through M<sub>3</sub> when an injection signal is applied. I<sub>out</sub> is the output current, which is the sum of I<sub>so</sub> and I<sub>inj</sub>. Figure 2(b) shows the phasor diagram for the three current types. The phasor rotates clockwise. Point 'a' shows that the phase has changed from I<sub>so</sub> by φ. Point 'b' shows the phase when the ILFD self-oscillates without an injection signal. The relational expression of the current vectors is as follows.

$$I_{out} = I_{so} + I_{inj}. \quad (1)$$

Two waves are shown in Figure 2(b), one is the self-oscillation signal of the ILFD and the other is the injection-locked signal. Point 'b' of the self-oscillation signal is moved to point 'a' by the injection signal. Therefore, the phase at 180° of the injection-locked signal is point 'a' of the self-oscillation signal. Injection is instantaneously performed every half period, and the range of φ can be derived using the following equations.

$$\phi = \angle I_{out} = \angle (I_{so} + I_{inj}), \quad (2)$$

$$V_{out} = Z_L \cdot I_{out}, \quad (3)$$

$$\angle I_{out} = \angle V_{out} - \angle Z_L, \quad (4)$$

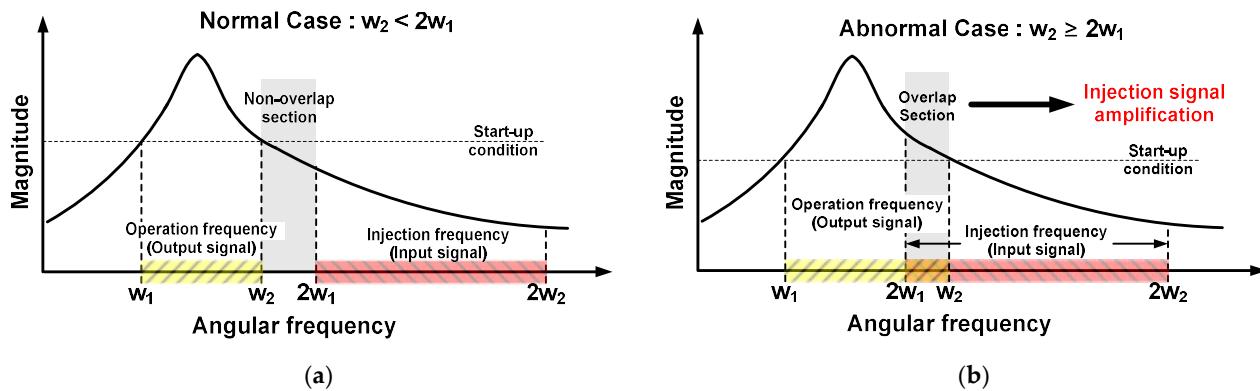

**Figure 3.** Graphs of magnitude of load impedance against angular frequency, (a) normal case (b) abnormal case.

where  $V_{out}$  is the output voltage signal when the ILFD is locked, and  $Z_L$  represents the load impedance of the LC resonator. Equation (4) can be derived using the phasor in (3). To replace  $V_{out}$  with the self-oscillation and injection signals, the following equations are derived as

$$V_{out} = V_{so} + V_{inj}, \quad (5)$$

where  $V_{so}$  is the output voltage signal when the ILFD self-oscillates and  $V_{inj}$  is the injection voltage signal generated from  $M_3$ . It should be noted that  $V_{inj}$  is different from the input voltage signal,  $V_{inj,2w}$ . According to (4) and (5), the  $\phi$  is calculated as

$$\phi = \angle(V_{so} \pm V_{inj}) - \angle Z_L. \quad (6)$$

The sign of  $V_{inj}$  is determined based on the value of the locked frequency relative to the self-oscillation frequency. When the ILFD self-oscillates with no injection signal, (6) is calculated as follows.

$$\phi|_{V_{inj}=0} = \angle V_{so} - \angle Z_L. \quad (7)$$

$V_{inj}$  is zero, and  $V_{so}$  is expressed as the product of  $I_{so}$  and  $Z_L$ . Because  $Z_L$  is canceled out, the following equation is satisfied:

$$\phi|_{V_{inj}=0} = \angle I_{so}. \quad (8)$$

Meanwhile,  $\phi_{max}$  is derived when the following condition is satisfied:

$$I_{out} \perp I_{inj}. \quad (9)$$

The largest angle between  $I_{so}$  and  $I_{out}$  can be realized by considering the phasor as shown in Figure 2(b). This is the condition of (9) where  $I_{out}$  and  $I_{inj}$  are vertical. Using the trigonometric function,

$$\sin \phi_{max} = \pm \frac{|I_{inj}|}{|I_{so}|}, \quad (10)$$

$$\phi_{max} = \pm \arcsin \left( \frac{|g_{inj} \cdot V_{inj}|}{|g_m \cdot V_{so}|} \right), \quad (11)$$

where,  $g_m$  and  $g_{inj}$  represent the transconductance of the cross-coupled pair and injection switch, respectively.

According to (6), the conditions for extending the locking range of the ILFD can be determined qualitatively. First, the magnitude of the self-oscillation signal  $V_{so}$  is decreased by reducing the sizes of  $M_1$  and  $M_2$  to decrease the transconductance of the cross-coupled pair. However, when the transconductance of the cross-coupled pair is too small, it can make failure in the self-oscillation, causing the ILFD to act as a harmonic buffer. Second, to increase the amplitude of  $V_{inj}$  generated by  $M_3$ , the size of  $M_3$  can be increased or the injection signal  $V_{inj,2w}$  can be amplified. However, the operation frequency may be limited by large parasitic capacitors. A pre-buffer, which consumes additional power will be required to increase the amplitude of  $V_{inj,2w}$ . Finally, the phase of the load impedance can be changed. The phase of  $Z_L$  can increase or decrease  $\phi$ . However, the maximum and minimum values of the phase,  $\pm\phi_{max}$ , limit the range of  $\phi$ . Therefore, the phase of  $Z_L$  should be close to zero value in the wide frequency range. In conclusion, the maximum and minimum values of  $\phi$  are determined by (11), and the method of extending the range of  $\phi$  is consistent with the equation in (6).

The power of the output signal should be greater than that of the input signal. Two graphs of the load impedance magnitude against the angular frequency are shown in Figure 3, which presents two cases. The first case is the normal case where the power of the input signal is significantly smaller than that of the output signal as shown in Figure 3(a). The range from  $w_1$  to  $w_2$  is the operation frequency band obtained by dividing-by-two, and the range from  $2w_1$  to  $2w_2$  is the injection frequency band. The operation and injection frequency bands do not overlap in the normal case because  $2w_1$  is larger than  $w_2$ . Therefore, the input signal does not exceed the start-up condition and is not amplified more than the output signal. The second case is the abnormal case where the power of the input signal can be larger than that of the output signal as in Figure 3(b). Here, the operation and injection frequency bands overlap because  $2w_1$  is smaller than  $w_2$ . The injection frequency band contains the parts that exceed the start-up conditions, which are determined by the following 'Barkhausen formula'.

$$g_m \cdot |Z_L| \geq 1. \quad (12)$$

In the abnormal case, the ILFD cannot be used in mm-Wave applications because the input and output signals are amplified together in the frequency band used.

This problem can be solved by increasing the division ratio of the ILFD. However, to operate at high division ratio, a harmonic signal with a small magnitude should be used, which results in a narrow locking range of the ILFD [19,20]. Additionally, the injection mixer for the high division ratio creates larger parasitic capacitance than the injection switch of the divide-by-two ILFD. Consequently, an ILFD that operates at a high division ratio greater than two is disadvantageous for application in the mm-Wave band. Therefore, a divide-by-two ILFD optimized to have a wide locking range without including the abnormal case would be most suited as a mm-Wave frequency divider. The following equation is used to calculate the locking range of the ILFD.

$$LR = \frac{w_2 - w_1}{w_1 + (w_2 - w_1)/2} \cdot 100 (\%). \quad (13)$$

Under the normal case condition,  $w_2 < 2w_1$ , the maximum locking range of the divide-by-two ILFD can be obtained when  $w_2$  is equal to  $2w_1$ . Therefore, the maximum locking range is

$$LR_{max} \Big|_{w_2=2w_1} = 66.7\%, \quad (14)$$

where  $LR$  is the locking range. If the locking range of the divide-by-two ILFD exceeds 66.7%, the power of the input signal may be greater than that of the output signal. In conclusion, the locking range of the ILFD should be designed to be less than 66.7%.

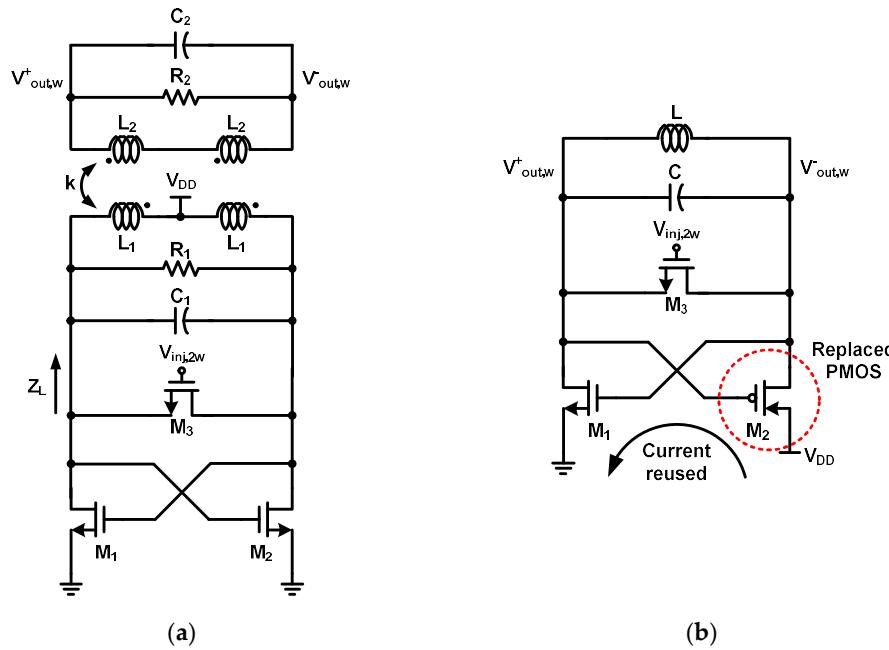

**Figure 4.** Schematic of (a) conventional cross-coupled pair ILFD with fourth-order resonator and (b) CR core based ILFD.

### 3. Circuit Design of Proposed CR-ILFD

### 3.1. Fourth-Order Resonator and CR Core

As mentioned in the previous section, to extend the locking range of the ILFD, the phase plot of the load impedance should be flat in the range of  $\pm\phi_{\max}$  [8,21]. A fourth-order resonator with two poles is required to flatten the phase plot. Figure 4(a) shows a schematic of the conventional cross-coupled pair based ILFD with a fourth-order resonator consisting of a resonator ( $L_1, C_1, R_1, L_2, C_2, R_2$ ), cross-coupled pair ( $M_1, M_2$ ) and injection switch ( $M_3$ ). The 'k' is the coupling factor between  $L_1$  and  $L_2$ .  $Z_L$  is the load impedance of the resonator, which is calculated as

$$Z_L = \frac{(1-k^2)L_1L_2C_2s^3 + L_1s}{(1-k^2)L_1L_2C_1C_2s^4 + (L_1C_1 + L_2C_2)s^2 + 1}. \quad (15)$$

$R_1$  and  $R_2$  are resistors that affect the quality (Q) factor of the resonator and have been approximated in this calculation. Two poles that make the denominator zero are represented using the following equation [22],

$$w_{R,L} = \sqrt{\frac{L_1 C_1 + L_2 C_2 \pm \sqrt{(L_1 C_1 + L_2 C_2)^2 - 4(1-k^2)L_1 L_2 C_1 C_2}}{2(1-k^2)L_1 L_2 C_1 C_2}}. \quad (16)$$

Assuming that  $L_1=L_2$  and  $C_1=C_2$ ,

$$w_{L,R} = \frac{1}{\sqrt{(1 \pm k)LC}}. \quad (17)$$

According to (17), the distance between the two poles increases as the value of  $k$  increases and the distance between the two poles decreases as the  $k$  value decreases. If  $k$  is zero, the pole value is obviously equal to that of the second-order resonator (18). Figure 4(b) shows a schematic of the conventional ILFD with the CR core. For the CR core,  $M_2$  of the cross-coupled pair ILFD in Figure 2(a) is replaced by PMOS [23–27]. The oscillation of the CR core can be divided into two half periods. In the first half period, the current flows through  $M_1$  and  $M_2$ , and in the second half period, no current flows through  $M_1$  and  $M_2$ .

Unlike the oscillation in the cross-coupled pair core, the oscillation of the CR core reduces the current by simultaneously turning the MOSFET on and off [24].

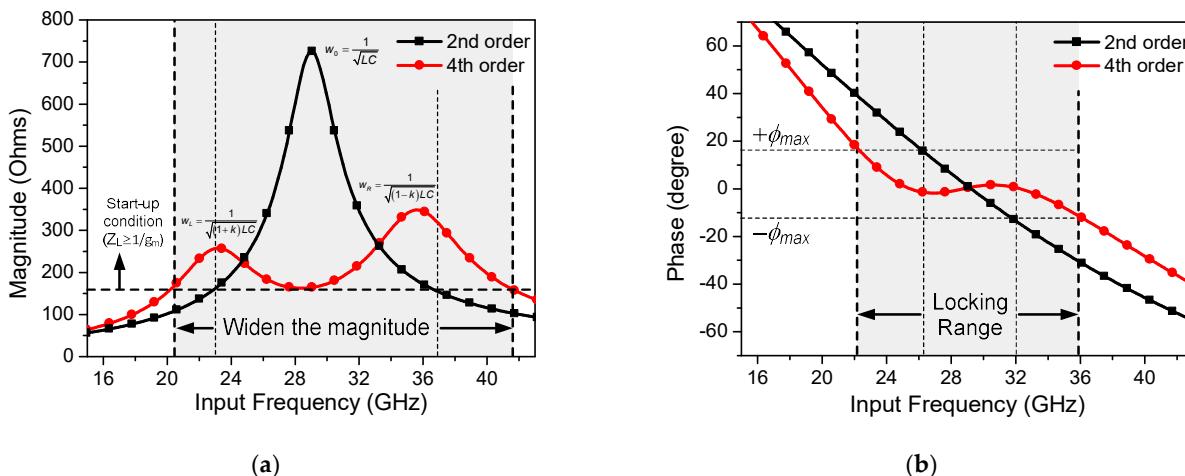

Figure 5 shows the magnitude and phase plots of the second and fourth-order resonator-based ILFDs. The schematic of the second-order resonator-based ILFD is shown in Figure 2(a). Figure 5(a) shows the graph of the load impedance magnitude against the input frequency. The second-order resonator-based ILFD has one pole,  $w_0$ , that is expressed as follows.

$$w_0 = \frac{1}{\sqrt{LC}}. \quad (18)$$

If the fourth-order rather than the second-order resonator-based ILFD is applied, the magnitude plot of the load impedance becomes wider even if the maximum magnitude value decreases. However, because a new minimum value occurs between the two poles, it is necessary to simulate whether locking is sufficiently achieved at this value. If the minimum value between the two poles is less than the start-up condition (12), the ILFD does not operate in that frequency range. Figure 5(b) shows the phase plot against the input frequency. According to (11), the  $\pm\phi_{max}$  limits the locking range of the ILFD. Unlike the phase of the second-order resonator-based ILFD, that of the fourth-order resonator-based ILFD has a value approximately equal to zero over a wide frequency range because of the formation of a ripple. Consequently, the simulated locking range of the ILFD is increased by 22% from 26 – 32 GHz (21%) to 22 – 36 GHz (43%).

**Figure 5.** (a) Simulated magnitude plot and (b) phase plot of second-order resonator-based ILFD and fourth-order resonator-based ILFD.

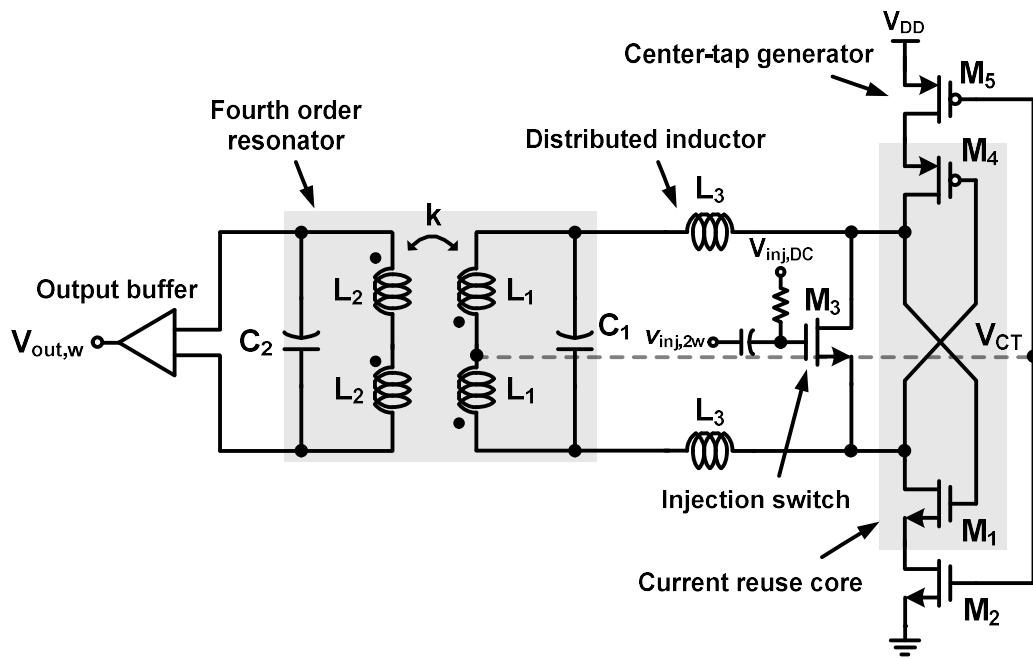

### 3.2. Proposed CR-ILFD

Figure 6 shows a schematic of the proposed CR-ILFD, consisting of a fourth-order resonator ( $L_1, C_1, L_2, C_2$ ), distributed inductor ( $L_3$ ), injection switch ( $M_3$ ), CR core ( $M_1, M_4$ ), center-tap generator ( $M_2, M_5$ ), and output buffer.  $V_{inj,DC}$  and  $V_{inj,2w}$  are the input signals, whereas  $V_{out,w}$  is the output signal. The center-tap generator biases the node of the primary coil,  $L_1$  to  $V_{CT}$ . If the  $g_m$  matching of PMOS and NMOS is well adjusted, mathematically,  $V_{CT}$  would be  $V_{DD}/2$ . The DC value of the injection switch can be biased to  $V_{CT}$  without additional supply, but it was not connected for measurement. The distributed inductor is employed to extend the locking range of the ILFD. The distributed inductor is also referred to as the inductor distributed technique [28,29]. The magnitude of the load impedance can be increased by distributing the primary inductor into two series inductors.

**Figure 6.** Schematic of the proposed CR-ILFD.

**Table 1.** Design parameters of the proposed CR-ILFD.

| Design parameter                                                             | Value                    |

|------------------------------------------------------------------------------|--------------------------|

| M <sub>1</sub> , M <sub>2</sub> , M <sub>4</sub> , M <sub>5</sub> (unit W/L) | 2 $\mu$ m / 0.06 $\mu$ m |

| M <sub>3</sub> (unit W/L)                                                    | 1 $\mu$ m / 0.06 $\mu$ m |

| Finger of M <sub>1</sub> , M <sub>3</sub> , M <sub>4</sub>                   | 20                       |

| Finger of M <sub>2</sub> , M <sub>5</sub>                                    | 50                       |

| L <sub>1</sub>                                                               | 230 pH                   |

| L <sub>2</sub>                                                               | 265 pH                   |

| L <sub>3</sub>                                                               | 433 pH                   |

| k                                                                            | 0.51                     |

| C <sub>1</sub>                                                               | 144 fF                   |

| C <sub>2</sub>                                                               | 240 fF                   |

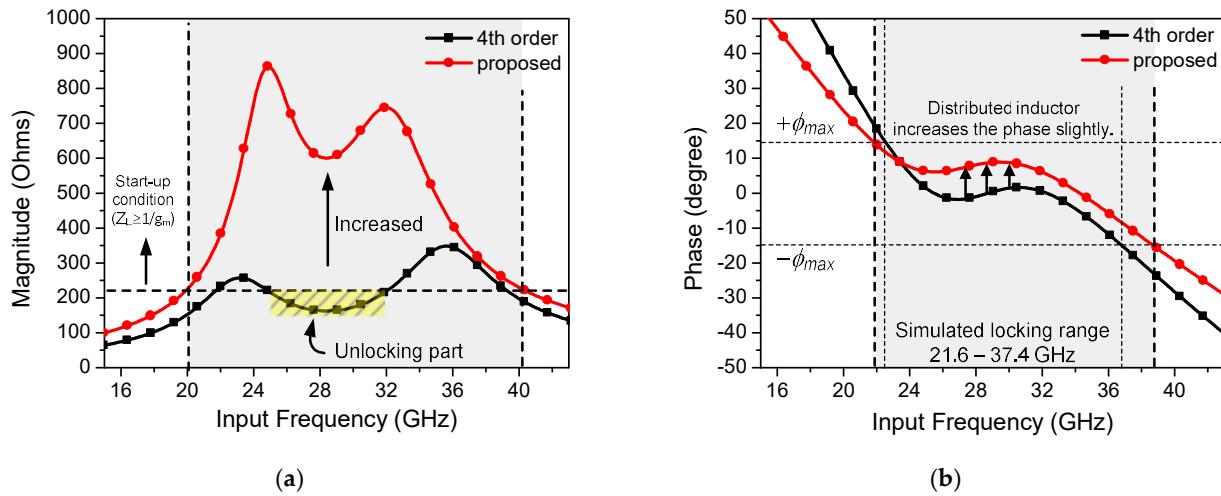

Figure 7(a) shows the simulated magnitude plot and phase plot of the fourth-order resonator-based ILFD and the proposed CR-ILFD with the fourth-order resonator with a distributed inductor. The start-up condition in Figure 7(a) is determined by the ‘Barkhausen formula’ in (12). In the case of the fourth-order resonator-based ILFD, an unlocking part may occur because of the minimum value that is less than the start-up condition. However, the magnitude of the load impedance is sufficiently increased by using the inductor distributed technique. Figure 7(b) shows the slightly increased phase. This is not a critical amount of change because the phase ripple still exists between the  $\pm\phi_{\max}$ . The simulated locking range of the proposed ILFD is from 21.6–37.4 GHz, which is limited by the  $\pm\phi_{\max}$  in (11).

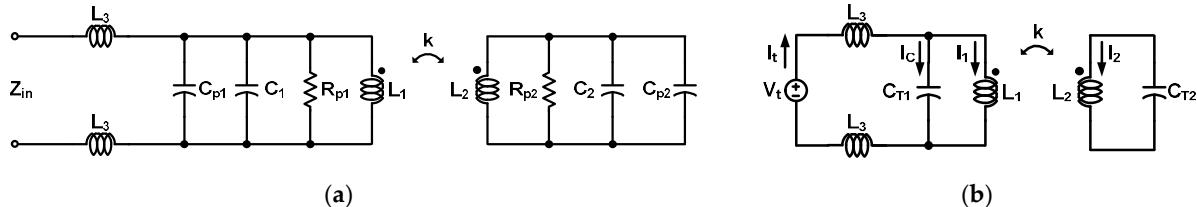

Figure 8 shows an equivalent model of the fourth-order resonator using a transformer with the distributed inductor. Figure 8(a) shows a model including the parasitic capacitors and resistors of the passive components. Z<sub>in</sub> is the input impedance and ‘k’ is the coupling factor between L<sub>1</sub> and L<sub>2</sub>. C<sub>p1</sub>, R<sub>p1</sub>, C<sub>p2</sub>, and R<sub>p2</sub> represent the parasitic components. In the mm-Wave band, the analog circuits are affected more by electromagnetism. Therefore, the modeling of the resonator must be considered at the initial design stage. Because analyzing every parasitic component is difficult, modeling should be simplified

**Figure 7.** (a) Simulated magnitude plot and (b) phase plot of the fourth-order resonator-based ILFD and proposed CR-ILFD.

**Figure 8.** (a) Modeling of the fourth-order resonator using a transformer with distributed inductor. (a) Modeling of including the parasitic capacitors and resistors. (b) Approximate modeling applied to simplify calculations.

by approximation as shown in Figure 8(b).  $C_{T1}$  is the sum of  $C_{p1}$  and  $C_1$ . Similarly,  $C_{T2}$  is the sum of  $C_{p2}$  and  $C_2$ . Additionally, the Q factor of the inductor includes the parasitic resistances.  $V_t$  and  $I_t$  are the test voltage and test current, respectively.  $V_t/I_t$  is equal to  $Z_{in}$  in the simplified model. The value of  $Z_{in}$  is calculated as follows.

$$Z_{in}(s) = \frac{(1 - k^2)L_1L_2C_{T2}s^3 + L_1s}{(1 - k^2)L_1L_2C_{T1}C_{T2}s^4 + (L_1C_{T1} + L_2C_{T2})s^2 + 1} \times (1 + 2L_3C_{T1}s^2). \quad (19)$$

If the distributed inductor ( $L_3$ ) is zero, then (19) is equal to (15). That is, the distributed inductor does not directly affect the pole value in (17), and if the distributed inductor value is increased, the magnitude of  $Z_{in}$  can be increased.

The design parameters are listed in Table 1. Because the center-tap generator should not limit the core operation, the width of the center-tap generator should be significantly larger than that of the CR core. The parasitic capacitor of the center-tap generator is separated from the resonator and does not affect the operating frequency. The sizes of the CR core and injection switch are not only determined by (11) and (12), but also by the influence of the parasitic capacitors.

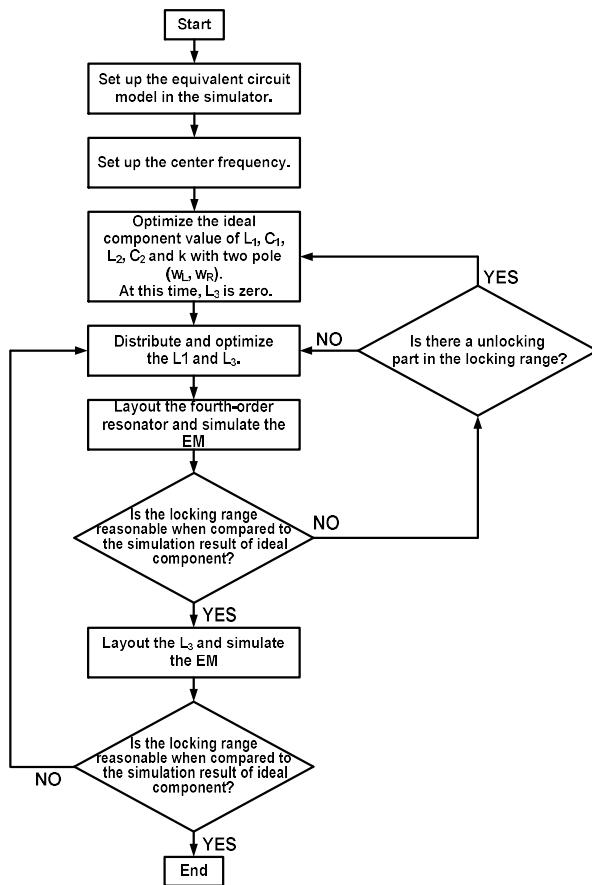

Figure 9 shows a flowchart of the design approach for the proposed CR-ILFD. First, the equivalent circuit model must be implemented in the simulator. Second, the values of the design parameters should be determined. In the proposed CR-ILFD, the center frequency is set to receive an injection signal of 28 GHz. Because the distributed inductor does not directly affect the pole value, the values of  $L_1$ ,  $C_1$ ,  $L_2$ ,  $C_2$  and  $k$  are first determined. Subsequently,  $L_1$  is divided into two series inductors,  $L_1$  and  $L_3$ . In this design,  $L_1$ ,  $L_2$ , and  $L_3$  are 230, 265, and 433 pH, respectively.  $C_1$  and  $C_2$  are 144 and 240 fF, respectively. The value of  $k$  is 0.51. When  $k < 0.5$ , which represents a weak coupling, the distance

**Figure 9.** Flowchart of the design approach for the proposed CR-ILFD.

between the poles increases, and a wide magnitude plot of the load impedance can be obtained. However, a coupling that is too weak can cause an unlocking part in which the ILFD does not work. Considering the locking range and unlocking part, the proposed CR-ILFD is designed with a coupling factor of 0.51. Finally, the layout and locking simulation are repeated in the order shown in the flowchart. Electromagnetic simulation is essential in the mm-Wave band. Therefore, it should be ensured that the difference between the equivalent modeling and implementation in the simulation of this circuit is reasonable.

#### 4. Measurement Results

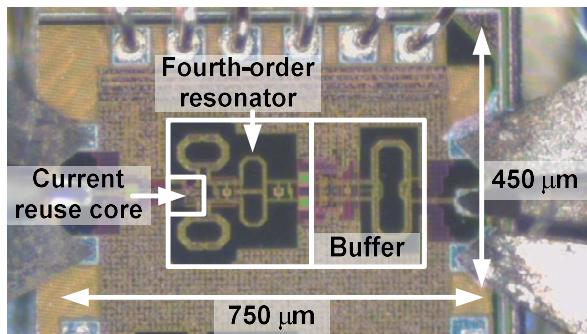

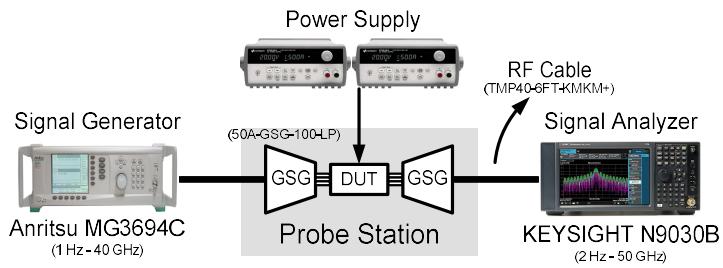

Figure 10 shows the die photograph of the proposed CR-ILFD, which was fabricated in a 65-nm CMOS technology. The die size including the entire pad is  $0.75 \text{ mm} \times 0.45 \text{ mm}$  and the chip size including the core and output buffer is  $0.49 \text{ mm} \times 0.3 \text{ mm}$ . The measurement setup for the proposed CR-ILFD is shown in Figure 11. The measurements were obtained using a probe station. The DC voltage was biased from the power supply. The CR core of the proposed CR-ILFD consumes 2.26 mW from a 1-V supply voltage, when no signal is applied to the injection switch. As  $V_{\text{inj,DC}}$  increases, the power consumption increases. When  $V_{\text{inj,DC}}$  is 0.7 V, the power consumption of the core increases by approximately 0.5 mW. The power consumption of the output buffer is approximately 3 mW. The injection signal was generated by Anritsu MG3694, which can generate frequencies up to 40 GHz. The output signal of the proposed CR-ILFD is analyzed by KEYSIGHT N9030B, which can analyze frequencies up to 50 GHz. When conducting measurements using mm-Wave signals, several losses occur around the device under test (DUT). Therefore, the calibration tests must be carried out carefully. In this measurement, the ground-signal-

**Figure 10.** Die photograph of the proposed CR-ILFD.

**Figure 11.** Measurement setup for the proposed CR-ILFD.

**Figure 12.** (a) Measured locking range results of the proposed CR-ILFD with different  $V_{inj,DC}$ ; (b) measured and simulated locking range results of the proposed CR-ILFD.

ground (GSG) probe tip has a loss of approximately 2.5 dB and that of the RF cable has approximately 3 dB. Approximately 1-dB loss occurs even when the signal generator output is 10 dBm. The loss of the signal generator was analyzed by connecting the signal analyzer and RF cable. All losses described above are based on the 28 GHz signal. Generally, the loss increases as the frequency increases, and decreases as the frequency decreases.

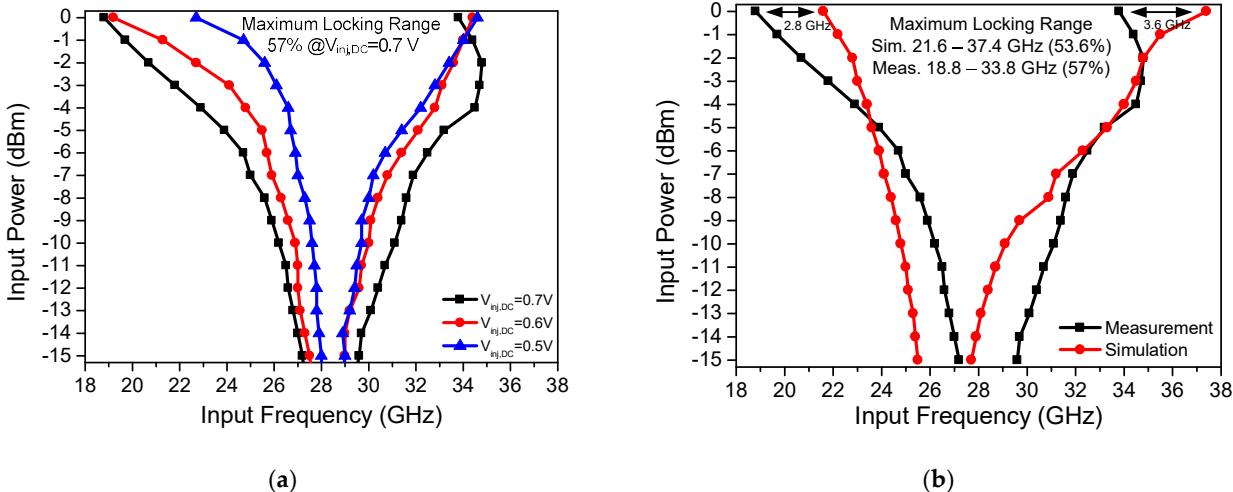

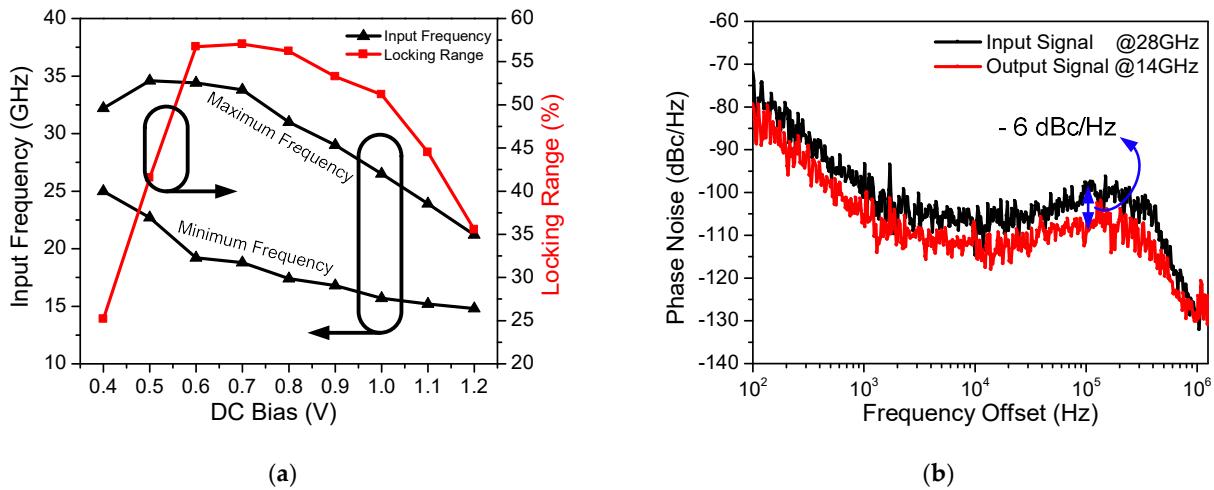

Figure 12(a) shows the measured locking range of the proposed CR-ILFD with different  $V_{inj,DC}$  values. The maximum locking range is from 18.8 to 33.8 GHz (57%) at  $V_{inj,DC}$  of 0.7 V. When the  $V_{inj,DC}$  is biased to 0.6 V, the locking range is from 19.2 to 34.4 GHz

**Figure 13.** (a) Measured maximum and minimum operation frequency of the proposed CR-ILFD with different  $V_{inj,DC}$ ; (b) Measured phase noise of input and output signal.

**Figure 14.** Spectrums of the output signal (a) when the proposed CR-ILFD self-oscillates; (b) when the proposed CR-ILFD is locked with a 28-GHz injection signal.

**Figure 15.** Full span spectrums (a) when the minimum input frequency is injected (18.8 GHz); (b) when the maximum input frequency is injected (33.8 GHz). The power difference between the output and input signals is approximately 10 dB or more.

(56.7%), and when the  $V_{inj,DC}$  is biased to 0.5 V, the locking range is reduced from 22.7 to 34.6 GHz (41.5%). The above ranges were obtained from 0-dBm input power and 1-V supply voltage. As the  $V_{inj,DC}$  decreases, the locking range also tends to decrease. Figure 12(b) shows a comparison of the measured and simulated locking range results of the proposed CR-ILFD. The measured locking range is 57%, and simulated locking range is from 21.6 to 37.4 GHz (53.6%). When 0-dBm input power is injected to the CR-ILFD, the measured locking range is typically changed to a lower frequency band than the simulated locking range. The operating frequency band was lowered by approximately 3 GHz. This is because of various electromagnetic components, such as RF pads, printed circuit board

Table 2. Performance comparison of different core ILFDs

| This work                              |                            | [30]<br>15' MTT       | [31]<br>09' MWCL             | [32]<br>08' MWCL             | [33]<br>14' MWCL                          | [34]<br>15' APMC                  | [35]<br>17' MWCL             |

|----------------------------------------|----------------------------|-----------------------|------------------------------|------------------------------|-------------------------------------------|-----------------------------------|------------------------------|

| Technology                             | 65-nm<br>CMOS              | 0.18- $\mu$ m<br>CMOS | 0.18- $\mu$ m<br>CMOS        | 0.18- $\mu$ m<br>CMOS        | 0.18- $\mu$ m<br>SiGe BiCMOS              | 0.18- $\mu$ m<br>CMOS             | 0.18- $\mu$ m<br>CMOS        |

| Core Topology                          | Current reuse              | Darlington            | Armstrong                    | Colpitts +<br>Current reuse  | Complement-<br>ary cross-<br>coupled pair | NMOS cross-<br>coupled pair       | NMOS cross-<br>coupled pair  |

| Self-oscillation<br>frequency<br>(GHz) | <b>14.08</b>               | N/A                   | 4.77 – 5.08<br>(w/ varactor) | 5.85 – 6.17<br>(w/ varactor) | N/A                                       | N/A                               | 2.97 – 4.66<br>(w/ varactor) |

| Input signal<br>power (dBm)            | <b>0</b>                   | 0                     | 0                            | 0                            | 0                                         | 0                                 | 0                            |

| Division ratio                         | <b>2</b>                   | 2                     | 2                            | 2                            | 2                                         | 2                                 | 4                            |

| Input fre-<br>quency range<br>(GHz)    | <b>18.8 – 33.8</b>         | 20.5 – 22.9           | 7.7 – 11.5                   | 7.3 – 14.4                   | 20.1 – 25.9                               | 10.2 – 15.5                       | 13 – 19                      |

| Locking range<br>(%)                   | <b>57</b>                  | 11                    | 39.6                         | 65.4                         | 25.1                                      | 41.4                              | 37.5*                        |

| Supply Voltage<br>(V)                  | <b>1</b>                   | 1.2                   | 1.4                          | 1.5                          | 1.8                                       | 1.2                               | 0.8                          |

| Power con-<br>sumption (mW)            | <b>2.26</b>                | 1.73                  | 9.02                         | 7.65                         | 4.8                                       | 2.71                              | 7.09                         |

| Phase noise<br>(dBc/Hz<br>@1 MHz)      | <b>-129.81<br/>(14GHz)</b> | -138.3<br>(N/A)       | -134.942<br>(4.9GHz)         | -134.8<br>(6GHz)             | -124<br>(12.5GHz)                         | -120.53<br>(5.495GHz<br>@ 100kHz) | -133.26<br>(4GHz)            |

| FOM <sub>1</sub><br>(GHz/mW)           | <b>6.64</b>                | 1.38                  | 0.42                         | 0.93                         | 1.21                                      | 1.96                              | 0.85                         |

| FOM <sub>2</sub><br>(GHz/mW)           | <b>13.28</b>               | 2.76                  | 0.84                         | 1.86                         | 2.42                                      | 3.92                              | 3.4                          |

| Chip size<br>(mm <sup>2</sup> )        | <b>0.75 × 0.45</b>         | 0.8 × 0.75            | 0.55 × 0.74                  | 0.46 × 0.52                  | 0.75 × 0.78                               | 0.57 × 0.68                       | 1.01 × 1.18                  |

FOM<sub>1</sub> = Input frequency range / power consumption [GHz/mW]FOM<sub>2</sub> = (Input frequency range × division ratio) / power consumption [GHz/mW]

\*: Total locking range (low band + high band)

(PCB), and metal lines that were not considered in the simulations. The measured maximum operation frequency is higher when the input power is -3 dBm compared to when the input power is 0 dBm. This is because of the saturation of the input signal level.

Figure 13(a) shows the measured maximum and minimum operation frequencies of the proposed CR-ILFD with different  $V_{inj,DC}$  values. This measurement was carried out with 0-dBm input power and 1-V supply voltage.  $V_{inj,DC}$  is swept from 0.4 to 1.2 V, and the widest locking range is obtained at the  $V_{inj,DC}$  of 0.7 V. When  $V_{inj,DC}$  increases from 0.7 V, the maximum and minimum operation frequencies decrease, and the locking range also decreases.

The measured phase noise of the input and output signal is shown in Figure 13(b). The 28 GHz input signal is generated by Anritsu MG3694, which is applied to the proposed CR-ILFD and the output signal is 14 GHz. The phase noise of the output signal is -109.57 and -129.81 dBc/Hz at 100 kHz and 1 MHz offset frequency, respectively. The phase noise of the output signal should be measured at 6 dBc/Hz lower than that of the input signal because the input signal frequency is twice that of the output signal. Figs. 17 – 20 show the results of several spectrums of the CR-ILFD's output signal measured using the

Table 3. Performance comparison of mm-Wave ILFDs

|                                  | This work             | [36]<br>15'MWCL | [37]<br>13'TCAS1 | [38]<br>11'MTT        | [39]<br>17'JSSC       | [40]<br>09'ISSCC      | [41]<br>20'MWCL   |

|----------------------------------|-----------------------|-----------------|------------------|-----------------------|-----------------------|-----------------------|-------------------|

| Technology                       | <b>65-nm<br/>CMOS</b> | 65-nm<br>CMOS   | 65-nm<br>CMOS    | 0.13- $\mu$ m<br>CMOS | 0.13- $\mu$ m<br>CMOS | 0.13- $\mu$ m<br>CMOS | 90-nm<br>CMOS     |

| Self-oscillation frequency (GHz) | <b>14.08</b>          | 17.5            | N/A              | 5.9                   | 25.9                  | N/A                   | 9.7               |

| Input signal power (dBm)         | <b>0</b>              | 0               | 0                | 0                     | 0                     | 0                     | -5                |

| Division ratio                   | <b>2</b>              | 2               | 4                | 4                     | 2                     | 2                     | 6                 |

| Input frequency range (GHz)      | <b>18.8 – 33.8</b>    | 31.7 – 39.3     | 58.5-72.9        | 13.5 – 30.5           | 35 – 44<br>41 – 59.5  | 35.6 – 39.3           | 54.5 – 60.1       |

| Locking range (%)                | <b>57</b>             | 21.4            | 21.9             | 77.3                  | 53*                   | 9.9                   | 9.8               |

| Supply Voltage (V)               | <b>1</b>              | 1               | 0.6              | 1.4                   | 1.15                  | 1                     | N/A               |

| Power consumption (mW)           | <b>2.26</b>           | 2.5             | 2.2              | 7.3                   | 3.8                   | 3.12                  | 5.6               |

| Phase noise (14 GHz)             | <b>-129.81</b>        | -102<br>(N/A)   | -126.74<br>(N/A) | -137.4<br>(6 GHz)     | -124<br>(24 GHz)      | -133.7<br>(N/A)       | -140<br>(9.7 GHz) |

| FOM <sub>1</sub> (GHz/mW)        | <b>6.64</b>           | 3.04            | 6.54             | 2.33                  | 6.45                  | 1.19                  | 1                 |

| FOM <sub>2</sub> (GHz/mW)        | <b>13.28</b>          | 6.08            | 26.16            | 9.32                  | 12.9                  | 2.38                  | 6                 |

| Chip size (mm <sup>2</sup> )     | <b>0.75 × 0.45</b>    | 0.6 × 0.75      | 0.16 × 0.26      | 0.52 × 0.64           | 1 × 0.9               | 0.13 × 0.18**         | 0.83 × 0.61       |

\*\*: Only core size

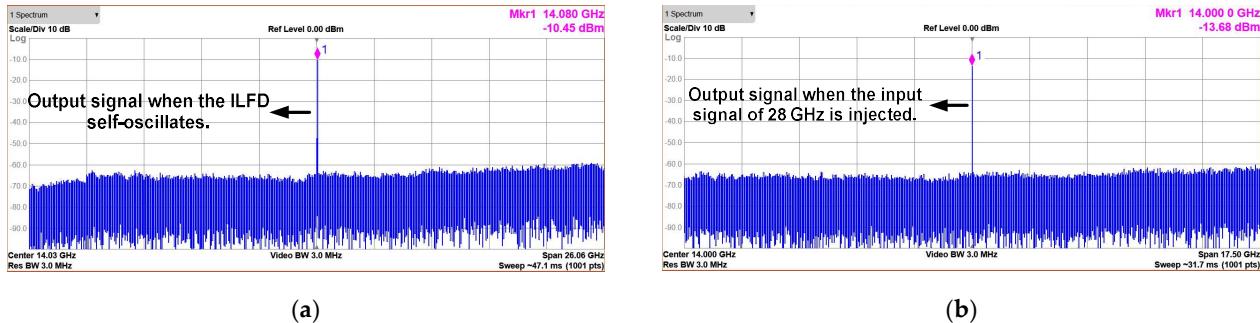

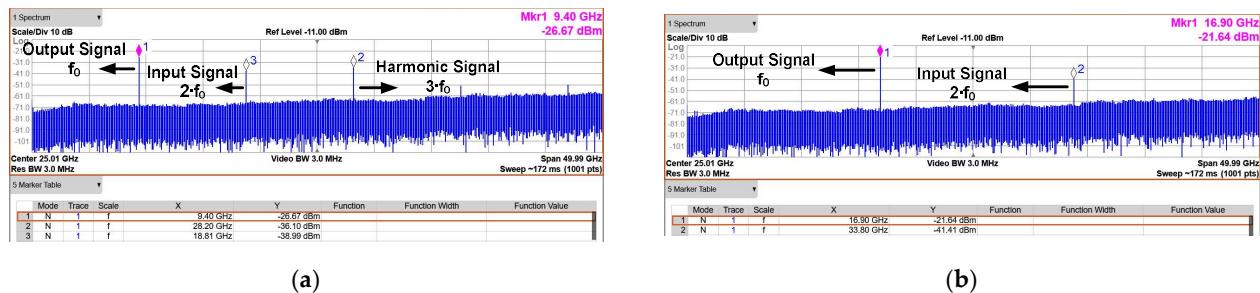

KEYSIGHT N9030B. The spectrum of the output signal when the proposed CR-ILFD self-oscillates is shown in Figure 14(a). The output frequency is 14.08 GHz, and output power is -10.45 dBm. If the loss of the RF cable and GSG probe tip is calibrated, the output power will be approximately -5 dBm. The spectrum of the output signal when the 28-GHz input signal is injected to the proposed CR-ILFD is shown in Figure 14(b). The frequency of the output signal is 14 GHz, which is exactly half the frequency of the input signal. The output power is approximately -8 dBm with loss calibration. Figure 15(a) shows the full span spectrum when the minimum input frequency, 18.8 GHz, is injected. Three tones are visible in the spectrum: the output signal ( $f_0$ ), input signal ( $2f_0$ ), and harmonic signal ( $3f_0$ ). As shown in Figure 3, several harmonic components are amplified at output when the minimum input frequency is injected to the CR-ILFD. Locking is possible even if a lower input frequency is injected. However, the input signal is amplified such that the power difference from the output signal is less than 10 dB. When 18.8 GHz is injected, the power difference between the desired output signal and the harmonic signal is approximately 10 dB. Figure 15(b) shows the full span spectrum when the maximum frequency input signal of 33.8 GHz is injected. The power difference between the output and input signals is more about 20 dB. It can be observed that the amplified input signal is smaller when the maximum input frequency is injected than when the minimum input frequency is injected.

Table 2 summarizes the performance comparison of different core ILFDs. These include challenging and typical ILFD cores such as Darlington [30], Armstrong [31], Collpits

[32], and cross-coupled pair [33–35]. This work has the highest figure of merit (FOM) compared to other ILFDs presented in the table 2.

Table 3 summarizes the performance comparison of the mm-Wave ILFDs [36–41]. ILFDs with division ratio greater than two are also included such as four [37,38] and six [41], but still have the highest FOM<sub>1</sub> values.

## 5. Conclusions

This paper presents the wide locking range and low power divide-by-two CR-ILFD. The fourth-order resonator is applied to extend the narrow operating range of the ILFD. In addition, the CR core decreases the power consumption. The input frequency locking range is from 18.8 to 33.8 GHz (57%) at an injection power of 0 dBm. The full-span spectrums at the maximum or minimum frequency are presented. The power difference between the output and harmonic signals is approximately 10 dB or more over the entire locking range. The proposed CR-ILFD dissipates 2.26 mW from a 1-V supply voltage and the die size is 0.75 mm × 0.45 mm. This CR-ILFD is implemented in a 65-nm CMOS technology.

**Author Contributions:** Conceptualization, K.-I.O. and D.B.; methodology, K.-I.O.; software, K.-I.O.; validation, K.-I.O., G.-H.K., and D.B.; formal analysis, K.-I.O.; investigation, K.-I.O. and G.-H.K.; resources, K.-I.O.; data curation, K.-I.O.; writing—original draft preparation, K.-I.O., J.-G.K., and D.B.; writing—review and editing, K.-I.O. and D.B.; visualization, K.-I.O. and D.B.; supervision, K.-I.O. and D.B.; project administration, K.-I.O., J.-G.K., and D.B.; funding acquisition, D.B. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Institute for Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (No.2019-0-00138, Development of Intelligent Radar Platform Technology for Smart Environments) and the Chung-Ang University Graduate Research Scholarship in 2020.

**Institutional Review Board Statement:** Not applicable.

**Informed Consent Statement:** Not applicable.

**Data Availability Statement:** No new data were created in this study. Data sharing is not applicable to this article.

**Acknowledgments:** The authors would like to thank all authors of previous papers for approving the use of their published research results in this paper.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

1. Kim, K.-R.; Kim, J.-H. Wideband Waveform Generation Using MDDS and Phase Compensation for X-Band SAR. *Sensors* **2020**, *12*, 1431.

2. Song, J.-H.; Lee, K.-W.; Lee, W.-K.; Jung, C.-H. High Resolution Full-Aperture ISAR Processing through Modified Doppler History Based Motion Compensation. *Sensors* **2017**, *12*, 1234.

3. Park, J.; Ryu, H.; Ha, K.-W.; Kim, J.-G.; Baek, D. 76–81-GHz CMOS Transmitter With a Phase-Locked-Loop-Based Multichirp Modulator for Automotive Radar. *IEEE Trans. Microw. Theory Techn.* **2015**, *63*, 1399–1408.

4. Ek, S. et al. A 28-nm FD-SOI 115-fs Jitter PLL-Based LO System for 24–30-GHz Sliding-IF 5G Transceivers. *IEEE J. Solid-State Circuits* **2018**, *53*, 1988–2000.

5. Wang, H.-N.; Huang, Y.-W.; Chung, S.-J. Spatial Diversity 24-GHz FMCW Radar With Ground Effect Compensation for Automotive Applications. *IEEE Trans. Veh. Technol.* **2017**, *66*, 965–973.

6. Lee, J.-Y.; Kim, G. S.; Ko, G.-H.; Oh, K.-I.; Park, J. G.; Baek, D. Low Phase Noise and Wide-Range Class-C VCO Using Auto-Adaptive Bias Technique. *Electronics* **2020**, *9*, 1290.

7. Kang, C.-W.; Moon, H.; Yang, J.-R. Switched-Biasing Techniques for CMOS Voltage-Controlled Oscillator. *Sensors* **2021**, *21*, 316.

8. Oh, K.-I.; Kim, G. S.; Park, J. -G.; Ko, G. -H.; Baek, D.; Fourth-order Resonator based Current Reuse Injection-Locking Frequency Divider with Peaking Inductor. In Proceedings of the 2019 Asia-Pacific Microw. Conf. (APMC), Singapore, Singapore, 10–13 Dec. 2019; pp. 1421–1423.

9. Zhao, X.; Chen, Y.; Mak, P.-I.; Martins, R.; A 0.0018-mm<sup>2</sup> 153% Locking-Range CML-Based Divider-by-2 With Tunable Self-Resonant Frequency Using an Auxiliary Negative-gm Cell. *IEEE Trans. Circuits Syst. I, Reg. Papers* **2019**, *66*, 3330–3339.

10. Chen, Y.; Yang, Z.; Zhao, X.; Huang, Y.; Mak, P. -I.; Martins, R. P. A  $6.5 \times 7 \mu\text{m}^2$  0.98-to-1.5 mW Nonself-Oscillation-Mode Frequency Divider-by-2 Achieving a Single-Band Untuned Locking Range of 166.6% (4–44 GHz). *IEEE J. Solid-State Circuits Lett.* **2019**, *2*, 37–40.

11. Ghilioni, A.; Mazzanti, A.; Svelto, F. Analysis and design of mm-Wave frequency dividers based on dynamic latches with load modulation. *IEEE J. Solid-State Circuits* **2013**, *48*, 1842–1850.

12. Hussein, A. I.; Paramesh, J. Design and Self-Calibration Techniques for Inductor-Less Millimeter-Wave Frequency Dividers. *IEEE J. Solid-State Circuits* **2017**, *52*, 1521–1541.

13. Lin, Y.-H.; Wang, H.; A 35.7–64.2 GHz low power Miller Divider with Weak Inversion Mixer in 65 nm CMOS. *IEEE Microw. Wireless Compon. Lett.* **2016**, *26*, 948–950.

14. Lin, Y.-S.; Huang, W.-H.; Lu, C.-L.; Wang, Y.-H.; Wide-Locking-Range Multi-Phase-Outputs Regenerative Frequency Dividers Using Even-Harmonic Mixers and CML Loop Dividers. *IEEE Trans. Microw. Theory Techn.* **2014**, *62*, 3065–3075.

15. Kuo, Y.-H.; Tsai, J.-H.; Huang, T.-W.; Wang, H. Design and Analysis of Digital-Assisted Bandwidth-Enhanced Miller Divider in 0.18- m CMOS Process. *IEEE Trans. Microw. Theory Techn.* **2012**, *60*, 3769–3777.

16. Chen, Y.-T.; Li, S.-W.; Huang, T.-H.; Chuang, H.-R. V-Band CMOS Direct Injection-Locked Frequency Divider Using Forward Body Bias Technology. *IEEE Microw. Wireless Compon. Lett.* **2010**, *20*, 396–398.

17. Cheng, Y.-H.; Tsai, J.-H.; Huang, T.-H. Design of a 90.9% Locking Range Injection-Locked Frequency Divider With Device Ratio Optimization in 90-nm CMOS. *IEEE Trans. Microw. Theory Techn.* **2017**, *65*, 187–197.

18. Jang, S.-L.; Lai, W.-C.; Ciou, Y.-L.; Hou, J. C. Divide-by-2 Injection-Locked Frequency Dividers Using the Electric-Field Coupling Dual-Resonance Resonator. *IEEE Trans. Microw. Theory Techn.* **2020**, *68*, 844–853.

19. Zou, Q.; Ma, K.; Yeo, K. S.; A V-Band Wide Locking Range Divide-by-4 Injection-Locked Frequency Divider. *IEEE Microw. Wireless Compon. Lett.* **2018**, *28*, 1020–1022.

20. Kim, J.; Lee, S.; Choi, D.-H.; Injection-Locked Frequency Divider Topology and Design Techniques for Wide Locking-Range and High-Order Division. *IEEE ACCESS* **2016**, *5*, 4410–4417.

21. Zhang, J.; Cheng, Y.; Zhao, C.; Wu, Y.; Kang, K.; Analysis and Design of Ultra-Wideband mm-Wave Injection-Locked Frequency Dividers Using Transformer-Based High-Order Resonators. *IEEE J. Solid-State Circuits* **2018**, *53*, 2177–2189.

22. Chao, Y.; Luong, H.; Analysis and Design of Wide-Band Millimeter-Wave Transformer-Based VCO and ILFDs. *IEEE Trans. Circuits Syst. I, Reg. Papers* **2016**, *63*, 1416–1425.

23. Ha, K.-W.; Ryu, H.; Lee, J.-H.; K, J.-G; Baek, D. Gm-Boosted Complementary Current-Reuse Colpitts VCO With Low Power and Low Phase Noise. *IEEE Microw. Wireless Compon. Lett.* **2014**, *24*, 418–420.

24. Ha, K.-W.; Ryu, H.; Park, J.; K, J.-G.; Baek, D.; Transformer-Based Current-Reuse Armstrong and Armstrong-Colpitts VCOs. *IEEE Trans. Circuits Syst. II, Exp. Briefs* **2014**, *61*, 676–680.

25. Ryu, H.; Ha, K. W.; Baek, D.; Low-power quadrature voltage-controlled oscillator using current-reuse and transformer-based Armstrong topologies. *Electron. Lett.* **2016**, *52*, 462–464.

26. Yun, S. J.; Shin, S.-B.; Choi, H.-C.; Lee, S.-G.; A 1mW Current-Reuse CMOS Differential LC-VCO with Low Phase Noise. In Proceedings of the 2005 IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, 11–15 Feb. 2005; pp. 540–541.

27. Ha, K.-W.; Sung, E.-T.; Baek, D. Low-power transformer-based current-reuse injection-locked frequency divider. *Electron. Lett.* **2015**, *51*, 161–162.

28. Lee, I.-T.; Tsai, K.-H.; Liu, S.-I.; A 104- to 112.8-GHz CMOS Injection-Locked Frequency Divider. *IEEE Trans. Circuits Syst. II, Exp. Briefs* **2009**, *56*, 555–559.

29. Lin, B.-Y.; Liu, S.-I. Analysis and Design of D-Band Injection-Locked Frequency Dividers. *IEEE J. Solid-State Circuits* **2011**, *46*, 1250–1264.

30. Chine, K.-H.; Chen, J.-Y.; Chiou, H.-K. Designs of K-Band Divide-by-2 and Divide-by-3 Injection-Locked Frequency Divider With Darlington Topology. *IEEE Trans. Microw. Theory Techn.* **2015**, *63*, 2877–2888.

31. Jang, S.-L.; Luo, J.-C.; Chang, C.-W.; Lee, C.-F.; Huang, J.-F. LC-Tank Colpitts Injection-Locked Frequency Divider With Even and Odd Modulo. *IEEE Microw. Wireless Compon. Lett.* **2009**, *19*, 113–115.

32. Jang, S.-L.; Huang, S.-H.; Lee, C.-F.; Juang, M.-H. LC-Tank Colpitts Injection-Locked Frequency Divider With Record Locking Range. *IEEE Microw. Wireless Compon. Lett.* **2008**, *18*, 560–562.

33. Mahalingam, N.; Ma, K.; Yeo, K.-S.; Lim, W.-M. Coupled Dual LC Tanks Based ILFD With Low Injection Power and Compact Size. *IEEE Microw. Wireless Compon. Lett.* **2014**, *24*, 105–107.

34. Wu J.-W. et al. Low Power Consumption and Wide Locking Range Triple-Injection-Locked Frequency Divider By Two. In Proceedings of the 2015 Asia-Pacific Microw. Conf. (APMC), Nanjing, China, 6–9 Dec. 2015; pp. 1–3.

35. Jang, S.-L.; Jina, S.-J.; Hsue, C.-W. Wideband Divide-by-4 Injection-Locked Frequency Divider Using Harmonic Mixer. *IEEE Microw. Wireless Compon. Lett.* **2017**, *27*, 924–926.

36. Mahalingam, N.; Ma, K.; Yeo, K. S.; Lim, W. M.; Modified Inductive Peaking Direct Injection ILFD With Multi-Coupled Coils. *IEEE Microw. Wireless Compon. Lett.* **2015**, *25*, 379–381.

37. Wu, L.; Luong, H. Analysis and Design of a 0.6 V 2.2 mW 58.5-to-72.9 GHz Divide-by-4 Injection-Locked Frequency Divider With Harmonic Boosting. *IEEE Trans. Circuits Syst. I, Reg. Papers* **2013**, *60*, 2001–2008.

38. Kuo, Y. -H.; Tsai, J. -H.; Chang, H. -Y.; Tsai, T. -W. Design and Analysis of a 77.3% Locking-Range Divide-by-4 Frequency Divider. *IEEE Trans. Microw. Theory Techn.* **2011**, *59*, 2477–2485.

---

39. Imani, A.; Hashemi, H. Distributed Injection-Locked Frequency Dividers. *IEEE J. Solid-State Circuits* **2017**, *52*, 2083–2093.

40. Chen H.-K. et al. A mm-Wave CMOS Multimode Frequency Divider. In Proceedings of the 2009 IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, 8–12 Feb. 2009, pp. 280–282.

41. Chang, H.-Y.; Chen, W.-C.; Yeh, H.-N.; Shen, I.Y.-E. A V-Band CMOS Low-DC-Power Wide-Locking-Range Divide-by-6 Injection-Locked Frequency Divider Using Transformer Coupling. *IEEE Microw. Wireless Compon. Lett.* **2020**, *30*, 593–596.