Type of the Paper (Article)

# **Exploring Energy-Efficient Ternary Inexact Multipliers Using CNT Transistors**

Sepehr Tabrizchi<sup>1</sup>, Atiyeh Panahi<sup>1</sup>, Fazel Sharifi<sup>2\*</sup>, Hamid Mahmoodi<sup>3</sup>, Abdel-Hameed A. Badawy<sup>4</sup>

- <sup>1</sup> Faculty of Computer Science and Engineering, Shahid Beheshti University G. C., Tehran, Iran.

- <sup>2</sup> Department of Electrical and Computer Engineering, Graduate University of Advanced Technology, Kerman, Iran

- <sup>3</sup> Department of Electrical and Computer Engineering, San Francisco State University, CA, USA

- <sup>4</sup> Klipsch School of Electrical and Computer Engineering, New Mexico State University, Las Cruces, NM, USA,

- \* Correspondence: badawy@nmsu.edu

Abstract: In recent decades, power consumption has become an essential factor in attracting the attention of integrated circuit (IC) designers. Multiple-valued logic (MVL) and approximate computing are some techniques that could be applied to integrated circuits to make power-efficient systems. By utilizing MVL-based circuits instead of binary logic, the information conveyed by digital signals increases, and this reduces the required interconnections and power consumption. On the other hand, approximate computing is a class of arithmetic computing used in systems where the accuracy of the computation can be traded-off for lower energy consumption. In this paper, we propose novel designs for exact and inexact ternary multipliers based on carbonnanotube field-effect transistors (CNFETs). The unique characteristics of CNFETs make them a desirable alternative to MOSFETs. The simulations are conducted using Synopsys HSPICE. The proposed design is compared against existing ternary multipliers. The results show that the proposed exact multiplier reduces energy consumption by up to 6X. At the same time, the best inexact design improves energy efficiency by up to 35X compared to the latest state-of-the-art methods. Using the imprecise multipliers for image processing provides evidence that these proposed designs are a low-power system with an acceptable error.

Keywords: CNFETs; Approximate Computing; Multiple-Valued Logic

#### 1. Introduction

The rapid evolution of the semiconductor industry has increased the number of components and complexity per unit area of a chip. Moore's law has set a growth roadmap for the IC industry to double the number of transistors per unit area in every new generation of devices and technology. Consequently, the feature size of transistors shrunk by 0.7X every two years following Moore's law [1]. The natural consequences of a decrease in the size of MOS transistors lead to challenges such as the increase of leakage current, quantum physical effects, and major complications as the results of thermal fluctuations, to name a few [1]. Researchers have been exploring emerging material and devices to replace classic MOS transistors and silicon-based chips as the beyond Moore's law alternatives. Resonant tunneling diodes (RTD), single-electron transistors (SET), quantum-dot cellular automata (QCA), and finally, carbon nanotube field-effect transistors (CNFET) are the most outstanding alternatives for MOSFET [2-5].

Among all the emerging nano-devices, carbon nanotubes are the most promising candidates for channel material in the future generation of transistors because of their ballistic transportation and their thin bodies and for other reasons [6]. Carbon nanotube field-effect transistors operate faster, with less energy consumption compared to their silicon counterparts [7]. There are many similarities in the inherent characteristics of CNFETs and MOSFETs. Such similarities make CNFETs the

appropriate replacement for MOSFET-like circuits with just a minor change in the MOSFET platform [8]. Also, CNFETs benefit from their adjustable threshold voltage, which is as easy as setting the diameter of the nanotube. In other words, the threshold voltage of CNFETs only depends on the diameter of the under-gate nanotubes. This unique characteristic of CNFETs makes them appropriate for designing MVL circuits [9].

MVL designs use more than two logic levels for representing their values. Compared to binary logic, each digit in MVL represents more data; therefore, the bandwidth and the number of lines for data transmission are less. On the other hand, for conceptual and implementation issues, choosing the optimal radix is of great importance [10]. For radix selection, We need a performance measurement metric. The product value of the radix by the required number of digits, which expresses a fixed range of numbers, is the performance measurement metric of choice.

Regarding the metric above, e-based (e = 2.718) operations are the optimum case. Ternary logic is superior to binary logic if we use the above metric since three is the closest integer to e [11]. Ternary logic provides the most efficiency with its lower energy consumption as a result of the reduction in the number of interconnection wires and the cost of data carriage [11].

Energy consumption is a primary concern in current and future systems [12]. Using MVL and low-power technologies such as CNFETs can reduce the power dissipation of arithmetic and logic circuits. Another low power technique that researchers have explored is approximate or inexact computing [13]. In approximate arithmetic circuits, for some input combinations, the output of the design is inexact. Such designs can reach minimum power consumption by using less hardware. Hence, the designs have a lower area while sacrificing computation accuracy but meeting an acceptable accuracy [13]. Approximate computing has its applications in digital signal processing, including voice and image processing [13]. In these applications, exact computing is not as important as in other arithmetic applications. Humans cannot distinguish minute imperfection in audio and video [13]. An approximation can be applied at different levels of design abstraction from algorithms to circuit design. Imprecise circuits such as approximate logical gates, adders, and multipliers could be useful in media processing without significant degradation in the output quality. Multipliers are one of the basic blocks used in different DSP applications, such as image filtering or image multiplication [13]. Therefore, an inexact multiplier with a reasonable error can improve energy efficiency in signal processing applications significantly.

In this paper, we propose a novel CNFET-based ternary one-trit multiplier. This exact design has less power and energy consumption compared to the other state-of-the-art designs. To reap the benefits of approximate computing, we propose to convert exact designs into inexact designs with a minor change in the original exact methodology. In this work, we have applied approximate designs in image processing applications, and the results show a balanced design trade-off between the accuracy and the energy consumption of the proposed designs.

The rest of the paper is organized as follows: The next section describes in detail the structure, merits, and demerits of CNFETs. Section 3 illustrates the detailed structure of the proposed designs. Section 4 contains the simulation results of the proposed exact and inexact designs and compares them to existing methods. Section 5 presents the results of utilizing the proposed methods in image processing applications, and finally, Section 6 concludes the paper.

## 2. Carbon Nanotube Field-Effect Transistor (CNFET)

A carbon nanotube (CNT) is a sheet of graphene rolled up like a tube with a diameter in nanometers [14]. These graphene tubes are used as the gate channels in CNFETs. A CNT can be a single-walled CNT (SWCNT), which is composed of a single tube, or it can be a multi-walled CNT (MWCNT), which has several tubes that have been rolled up inside each other [15]. Some favorable characteristics of single-walled CNFETs include lower short channel effects in short channel lengths, higher gain, larger Ion/Ioff ratio, reduced power consumption as a result of ballistic transport in a transistor body with one-dimensional structure. These advantages are why many researchers feel that carbon nanotubes are a suitable candidate for future transistors [16,17].

Carbon nanotube transistors are grouped into three different types, which have been named Schottky-Barrier (SB), partially gated (PG), and doped S/D CNFET. The first group has robust

ambipolar characteristics and a small Ion/Ioff ratio. In this type of CNFETs, gate bias determines the transistor functionality. Hence, it is not suitable for conventional CMOS logic families. The second group is uniformly doped and works in depletion mode. Doped S/D transistors, the third group, work in enhancement or depletion mode. They have a unipolar characteristic and reduced OFF leakage current and are suitable for MOSFET-like circuits [18].

The atomic structure of CNFETs is determined by the chiral vector (n, m). To be more specific, n and m indices determine the chirality, and chirality affects conductance. For instance, a nanotube is metallic if the difference of these vector indices is divisible by three; otherwise, the nanotube is a semiconductor. As described in [19], (n, m) indices determine the perimeter vector, as defined in Eqn. (1).

$$\vec{A} = (n, m) = n\vec{a}_1 + m\vec{a}_2$$

(1)

In this case,  $\vec{a}_1$  and  $\vec{a}_2$  are the basis vectors of graphene lattice. They separated by an inter-angle of 60° with ( $a_1 = a_2 = a_0 = 0.246 \ nm$ ). The magnitude value of the vector  $\vec{A}$  is calculated as in Eqn. (2). Eqn (3) calculate the diameter of the nanotube. (3) [19].

$$A = a_0 \sqrt{n^2 + m^2 + nm}$$

(2)

$$D_{CNT} = \frac{A}{\pi} = \frac{a_0}{\pi} \sqrt{n^2 + m^2 + nm}$$

(3)

In the above equations,  $a_0$  is the basis vector of graphene lattice, and n and m are chiral vector indices. The following Eqn determines the threshold voltage of CNFETs [20].

$$V_{th} \cong \frac{E_g}{2e} = \frac{\sqrt{2}}{2} \times \frac{aV_{\pi}}{eD_{CNT}} \cong \frac{0.43}{D_{CNT}(nm)}$$

(4)

where, a is the carbon-to-carbon atom distance,  $V_{\pi}$  is the carbon  $\pi - \pi$  band energy in the tight bonding model, e is the unit electron charge, and  $D_{CNT}$  is the diameter of CNTs, as calculated in Eqn. (3). By considering (1) through (4), we can conclude that the threshold voltage of CNFETs depends on the diameter of the under-gate tubes; and, consequently, by changing the chiral vector indices, nanotube diameter and the threshold voltage are set quickly. This important unique characteristic of CNFETs makes them suitable for use in MVL logic circuits.

Due to the properties mentioned above for carbon nanotube-based transistors, we utilize single-walled S/D CNFETs for designing ternary exact and inexact multipliers.

#### 3. Proposed work

This section describes the proposed ternary multipliers in detail. It is essential to mention that in ternary logic, the output is equal to "0", "1", or "2" logic levels with equivalent voltages of "0", " $V_{dd}/2$ ", and " $V_{dd}$ ". As mentioned previously, we propose an exact multiplier which has two ternary input digits and a ternary product and carry digits as outputs. Table 1 shows the truth table. Then, we relaxed the exact output's result of the cell for an input combination to reach better performance in specific applications like DSP. The approximate designs are different from the exact ones because of the elimination of some parts of the exact circuit.

#### 3.1 The Proposed Exact Design

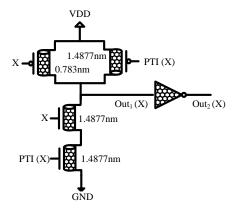

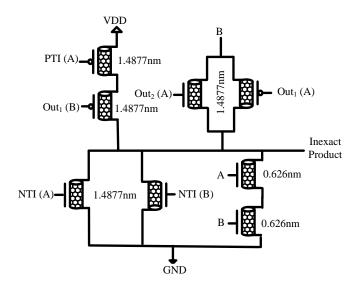

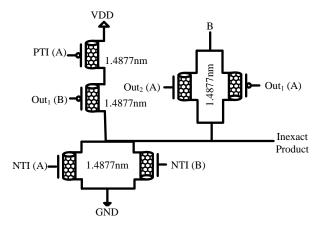

In this section, the proposed exact design of the ternary one-trit multiplier is described. First of all, it is essential to mention that in the schematic design of all the proposed methods,  $Out_1(X)$  is the output of the circuit, as shown in Fig. 1. This circuit gets a ternary digit of X as its input and produces  $Out_1(X)$  and  $Out_2(X)$  as binary outputs.  $Out_2(X)$  is the negated of the  $Out_1(X)$  that is utilized in the proposed methods. The truth table of these two outputs is illustrated in Table 2. Also, in the

schematic of circuits, the NTI and PTI are negative ternary inverter and positive ternary invert, respectively, which their functions are detailed in Table 2.

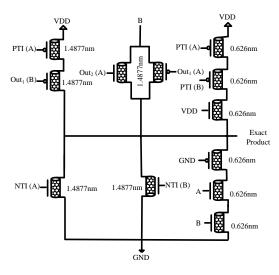

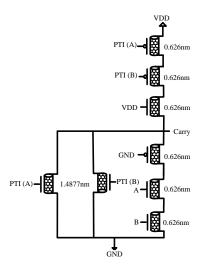

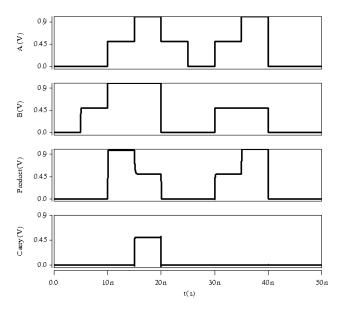

The schematic design of the exact product digit is shown in Fig. 2. We can conclude from Fig. 2, and the truth table of a one-trit multiplier shown in Table 1, for the first three input combinations, only the leftmost NFET of the pull-down network will be ON since NTI (A) would be logically equal to "2". For the input conditions that the first input is equivalent to "1", the middle transmission gate of the pull-up network turns on, and the second input reaches to the output node. If the input digits would be equal to "20" or "21", the middle NFET of pull-down network and the two leftmost PFETs of the pull-up network will be activated, respectively. For the last input combination wherein both of the inputs are equal to "2", the rightmost transistors turn on. In other words, for this condition, the product digit should be equal to "1"; hence, both of the pull-up and pull-down networks are active, and by a resistive division, the output becomes logically equal to "1". The proposed design for the carry out digit has been illustrated in Fig. 3 and its output is "0" for all input conditions except for the last input combination of Table 1. In this situation, the pull-up network and the rightmost NFET transistors of the pull-down network go ON, and the result would be equal to " $V_{dd}/2$ " at the carry output node. The method for voltage dividing to produce " $V_{dd}/2$ " at the output can be found in more detail in [21]. The transient responses of the proposed exact multiplier are shown in Fig. 4, which confirms its correct operation.

Table 1 Truth Table of One-Trit Ternary Multiplier

| A   | В   | Product | Carry |

|-----|-----|---------|-------|

| 0   | 0   | 0       | 0     |

| 0   | 1   | 0       | 0     |

| 0   | 2   | 0       | 0     |

| 1   | 0   | 0       | 0     |

| 1   | 1   | 1       | 0     |

| 1   | 2   | 2       | 0     |

| 2 2 | 0 1 | 0 2     | 0 0   |

Table 2 Truth Table of Ternary NTI, PTI, Out1, and Out2

| X | NTI(X) | PTI(X) | $Out_1(X)$ | $Out_2(X)$ |

|---|--------|--------|------------|------------|

| 0 | 2      | 2      | 2          | 0          |

| 1 | 0      | 2      | 0          | 2          |

| 2 | 0      | 0      | 2          | 0          |

Fig. 1. Schematic design of the Out1 and Out2 output.

Fig. 2. Schematic design of the proposed exact multiplication digit.

Fig. 3. Schematic design of the proposed exact carry output digit.

Fig. 4. Transient responses of the proposed exact multiplier.

#### 3.2 The Proposed Inexact Designs

In this section, the proposed inexact designs are discussed further. Generally, these inexact designs relax the product or carry output digit for only the last inputs combination of Table 1, which is encircled. The reason for allowing this input combination to be imprecise is that this is the only combination in which the value of its output is equal to "1," while none of the inputs are "1". Thus, the design of outputs is more expensive since the outputs can not be reached by using any of the inputs directly. This relaxation occurs by removing some parts of the exact design and consequently having an inexact result at the output.

#### 3.2.1 First inexact design

In this design, the product digit of the ternary multiplier would equal "0" for the last input condition of Table 1. Also, in this design, the carry output digit is equal to "0" for all input combinations. In other words, we have the output of "00" for the input combination of "22". Figure 5 shows the schematic at the transistor level of the first design method, which is a modified version of the exact design we discussed previously.

Fig. 5. Schematic design of the first proposed inexact design.

#### 3.2.2 Second inexact design

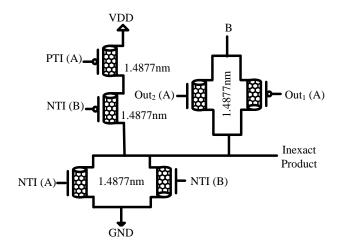

As we know, the product digit for the input digits of "22" is equal to "1" in the exact methods. Nevertheless, just like the first inexact method, the last part of the exact design is eliminated, which causes the product digit to be logically equal to "2" for this input combination. The schematic design of the second inexact method has been shown in Fig. 6. The second method also considers the inexact carry output. In this design, the carry output digit would be equal to zero for all of the inputs. Hence, the circuit which generates the carry output is eliminated, and the carry output node is connected to the ground voltage to be equal to "0".

Fig. 6. Schematic design of the second proposed inexact design.

#### 3.2.3 Third inexact design

The main idea of designing this circuit is to have an exact carry output digit to have a more precise design. The product digit of this method is the same as the first inexact design. Therefore, we have "1" and "0" at the carry and product outputs respectively for the "22" input pattern.

#### 3.2.4 Fourth inexact design

The significant difference between the second and fourth designs is that the output carry is exact in this design. But its product digit would be equal to "2" for the "22" input combination, just like the second method.

#### 3.2.5 Fifth inexact design

Finally, this design keeps the previous value of the product digit for the "22" input pattern. Fig. 7 represents the schematic design of this circuit. If the two input trits were logically equal to "2", none of the paths will be active, and the output capacitor holds the previous product value. This design is exact for some input chains and inexact for some others. If the previous value of the product digit is equal to "1" and both of the next inputs would be equal to "2", the product digit is "1," and hence, it would be an exact result. The probability of an exact product result is more than the other proposed inexact designs. It should be mentioned that the carry output is exact in this design. It seems that this is a sufficient accuracy for most DSP applications. We discuss this further in the next sections of this paper. Table 3 shows the truth table of all proposed inexact ternary multipliers.

Fig. 7. Schematic design of the fifth proposed inexact design.

Inexact 1 Inexact 3 Inexact 4 Inexact 5 Inexact 2 В Α Product Carry Product CarryProduct Carry Product CarryProductCarry1

Χ

Table 3 Truth Table of inexact ternary multipliers

#### Simulation Results

This section presents the simulation results of all the proposed designs in detail. Simulations are conducted in Synopsys HSPICE with the compact SPICE model for CNFET devices presented in [22-24]. Table 4 shows some critical parameters of this model. For fairness, for all designs in our simulations, the number of nanotubes under the gates for any transistor is fixed to five. The delay, power, and energy consumption of the proposed designs are compared with the previous exact designs in Table 5 for 200 MHz operational frequency and a 2fF load capacitor at the output nodes. It is clear-cut that all of the proposed exact and inexact designs reduce the delay, power, and energy consumption compared to the previous methods. Among the proposed inexact designs, the first two methods that have inexact carry output digit have the least energy consumption; but their error value is higher than the others. The third and fourth methods increase the accuracy besides the degradation of the performance of the multiplier by increasing the energy consumption. It seems that the fifth method has the optimum trade-off between the error distance and energy consumption among all the proposed inexact designs.

Table 4 Some CNFET Model Parameters

| Parameter  | Description                       | Value |

|------------|-----------------------------------|-------|

| $L_{ch}$   | Dhysical shannel Length           | 32    |

|            | Physical channel Length           | nm    |

| I          | The mean free path in the         | 100   |

| $L_{geff}$ | intrinsic CNT channel             | nm    |

| ī          | The length of doped CNT drain-    | 32    |

| $L_{dd}$   | side extension region             | nm    |

| $L_{ss}$   | The length of doped CNT source-   | 32    |

|            | side extension region             | nm    |

| au         | The thickness of the high-k top   | 1     |

| $T_{ox}$   | gate dielectric material          | nm    |

| V          | The dielectric constant of high-k | 16    |

| $K_{gate}$ | top gate dielectric material      | 10    |

| $E_{fi}$   | The Fermi level's depend S/D tube | 6     |

|            | The Femi level's doped S/D tube   | eV    |

| $C_{sub}$  | The coupling capacitor of the     | 20    |

|            | channel region and the substrate  | pF/m  |

Table 5 Simulation Results

|                       | Delay<br>(e-11 s) | Power<br>(e-7 W) | Energy<br>(e-17 J) |

|-----------------------|-------------------|------------------|--------------------|

| Proposed exact design | 4.23              | 4.16             | 1.76               |

| 1st inexact design    | 4.14              | 0.92             | 0.38               |

| 2nd inexact design    | 4.15              | 0.81             | 0.33               |

| 3rd inexact design    | 4.17              | 3.60             | 1.50               |

| 4th inexact design    | 4.12              | 2.03             | 0.83               |

| 5th inexact design    | 4.15              | 1.97             | 0.82               |

| Design of [26]        | 9.01              | 12.90            | 11.63              |

| Design of [27]        | 8.37              | 18.87            | 15.81              |

Table 6 Area and Energy Results

|                       | transistors | Width  | Width×Energy |

|-----------------------|-------------|--------|--------------|

|                       |             | (e-9m) | (e-25mJ)     |

| Proposed exact design | 26          | 2600   | 442          |

| 1st inexact<br>design | 16          | 1600   | 60.8         |

| 2nd inexact<br>design | 14          | 1400   | 46.2         |

| 3rd inexact<br>design | 22          | 2200   | 330          |

| 4th inexact<br>design | 20          | 2000   | 166          |

| 5th inexact<br>design | 20          | 2000   | 164          |

| Design of [26]        | 80          | 8000   | 9304         |

| Design of [27]        | 94          | 9400   | 148614       |

To compare the area of the proposed designs with existing designs in the literature, the number of transistors and the total width of transistors for each design are compared as metrics of the area [25]. Table 6 shows that the exact proposed method reduces the transistor count to 3X and 3.6X compared to the designs of [26] and [27], respectively. Moreover, total width  $\times$  energy is a parameter, which is written in this table to show a trade-off between area and energy consumption of designs [28].

The rest of this section investigates the operation of circuits in various operational situations. This includes the different operational temperatures, different supply voltages, and also the reliability of the proposed methods in the presence of process variation conditions (e.g., in situations that the number of tubes and nanotube diameter fluctuates by up to  $\mp 15\%$ ). All of the results are

compared with the existing exact designs of [26, 27] since there are no other inexact CNFET-based ternary multipliers.

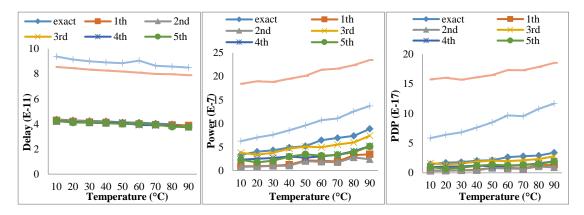

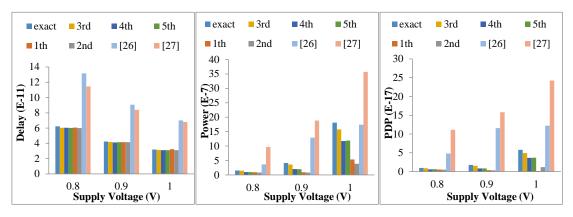

To asses the correct operation of the proposed methods and in comparison with previous state-of-the-art designs, all the methods are simulated for operational temperatures ranging from 0  $^{\circ}$ C to 90  $^{\circ}$ C at 200 MHz operational frequency and a 2fF capacitor at output nodes. As Fig. 8 shows, all of the proposed methods benefit from lower delay and lower power consumption when compared to the previous exact multipliers.

Our designs are also more resilient to temperature variation, especially in their power and energy consumption. In contrast, the designs of [26, 27] show increased power and energy consumption by increasing the temperature, which is because of their large number of transistors, which can be affected by temperature variation.

Fig. 9 evaluates the correct operation of all circuits under various supply voltages. This figure represents the results at 200 MHz input frequency and a load capacitor of 2fF. As it is anticipated, more supply voltages result in more power consumption for all designs. The fifth proposed inexact design has almost 6X and 9X lower power consumption compared with designs of [26] and [27] at 0.9V supply voltages, respectively.

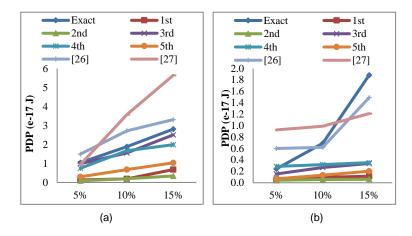

As we know, CNFETs have a large margin for process variations compared to MOSFETs. However, due to lithographic techniques and fabrication processes, they are prone to parametric variations such as variation in pitch value, number of tubes, or nanotube's diameter [29]. Hence, designing a process-variation aware circuit is very important. The Monte Carlo simulation is conducted to identify the sensitivity of the proposed methods against diameter variation and density variation (pitch and number of tubes). The simulation of the proposed designs is conducted with up to  $\mp 15\%$  under Gaussian distribution at  $\mp 3\sigma$ . Figure 10 shows that the proposed methods are almost constant in PDP values by increasing the percentage of parameter variation compared to the existing designs. This is especially true for inexact designs. Present systems are more intricate and susceptible to failure, and therefore, designs that work correctly under process, voltage, and temperature variations are preferred.

Fig. 8. Operation of the proposed methods under temperature variation

Fig. 9. Operation of the proposed methods under supply voltage variations

**Fig. 10.** PDP variations vs. process variation of designs. (a) CNT diameter variation. (b) CNT density variation.

## 5. Applications

Approximate computing is applied in cases when the exact result is hard to find, it does not exist, or the imprecise results are sufficient for the users [30]. For example, the perceptual limitation of human vision capabilities persuades designers to use approximate computing in this class of applications. In this section, we discuss the results of using exact and inexact multipliers in image processing applications. A multiplier can be used for sharpening, smoothing, and image multiplication in image processing applications. Two images are blended into a single output image by multiplying two images pixel by pixel [31,32]. Each RGB value of a pixel is an integer in the range of [0, 255], which can be represented with a six-digits ternary number. Inexact one-trit multipliers were utilized to multiply two ternary numbers digit by digit. The results are imprecise, but these inexact circuits might not cause that much degradation in the quality. The rest of this section compares the proposed inexact methods in different image processing applications such as image multiplication or image filtering, to find the most desirable method among all the proposed designs. C++ codes in Microsoft Visual Studio implement the following image applications.

To have a perspective on the error of the proposed approximate multipliers, we calculate the inaccuracy of the designs under normalized error distance (NED) metric. NED is independent of the multiplier size, which is useful for assessing the reliability of designs, as is discussed further in [33]. NED is calculated based on equation 5 [33].

$$NED = \frac{1}{2^{2N}} \sum_{i=1}^{2^{2N}} \frac{|ED_i|}{D}$$

(5)

where, ED<sub>i</sub> is the difference between the output of precise block and the output of its imprecise version for i-th input vector, and D denotes the maximum possible of ED in an imprecise multiplier.

Table 7 shows NED values for the proposed inexact multipliers for a  $6 \times 6$  ternary multiplication. As anticipated, the first and the second methods that have inexact carry outputs have the most error value, while the fifth method that is exact for more input conditions has the least NED value. For the exact proposed method and designs of [26, 27], NED is zero since all of the multiplication results are equal to the exact result. To find a balance point between the error value and the power consumption of the designs, the metric of NED  $\times$  Power is defined and calculated for the imprecise designs in Table 7. The power value that is reported in this table is calculated for a  $6 \times 6$  multiplication (excluding the reduction steps). By taking into account the NED  $\times$  Power values, it is concluded that the fifth method is the optimum design considering this metric.

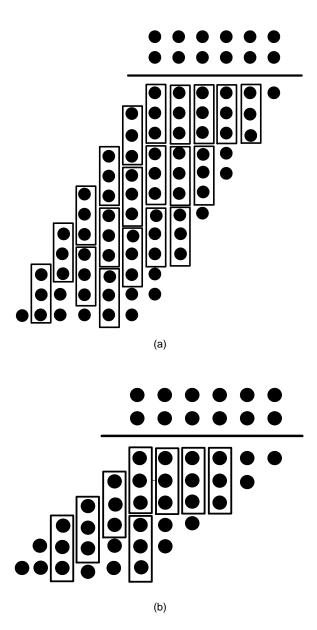

Figure 11 shows a 6×6 ternary multiplication steps that include six partial products with each one consisting of a product digit and a carry output digit. By ignoring the carry output, as it occurs in the first and the second inexact designs, the partial product digits decrease by half. Consequently, the number of adder cells for the reduction steps reduce from 53 to 20. This is shown in Fig. 11 for the first reduction step. But this is only one metric. The designs should be compared with other metrics, such as precision in various applications. The rest of the paper is dedicated to this subject.

One of the essential applications in image processing cases is the multiplication of two images. In this case, the peer-to-peer image pixels are multiplied into each other. The multiplication is a basic block, and therefore, its performance affects the overall performance of each application.

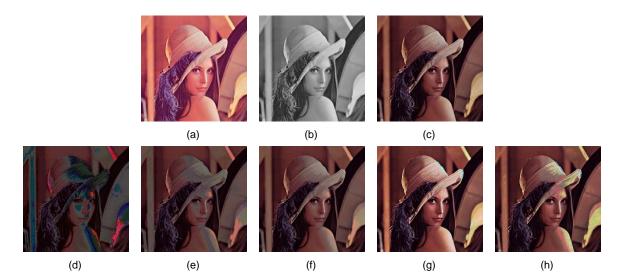

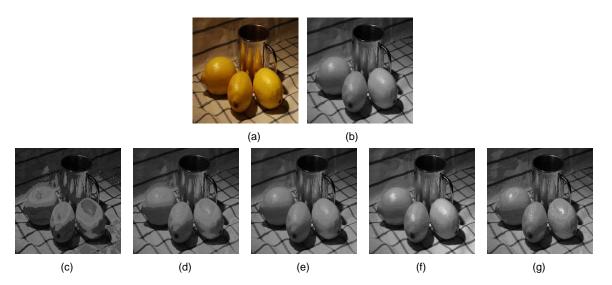

The proposed designs are utilized to examine the evaluation metrics with the intent to find a design that has the best operation that balances the error value and energy consumption. The results of an example of image multiplication have been shown in Fig. 12. The inexact designs (except the first design) have an acceptable error value when compared to the exact ones which have a high energy consumption.

To evaluate the exactness of the image output results, we use PSNR (peak signal-to-noise ratio) is used as a quality measurement. This metric compares the degraded output image with the original image, which is the result of the exact multiplication. A higher PSNR value shows a more exact output. Table 7 shows the results of this example. As the PSNR values authenticate, the first inexact method, which has the most distance from the exact results, has the worst results. The fifth method is the best since, in this design, the probability of the exact output value is more than the other inexact proposed methods.

Another application that could be examined is the conversion of a color image to grayscale. By converting an image to grayscale, all of the RGB elements have the same value. This common value is calculated from a weighted average of the original RGB values of the input colored image [34]. The formula that is used to convert colored pixels to black and white is shown in (5) [34].

Table 7 NED and Power Comparison

|                                | NED   | Power   | NED ×        |

|--------------------------------|-------|---------|--------------|

|                                | (e-4) | (e-6 W) | Power (e-10) |

| 1st inexact design             | 4.55  | 3.312   | 15.06        |

| 2 <sup>nd</sup> inexact design | 2.27  | 2.916   | 6.619        |

| 3 <sup>rd</sup> inexact design | 1.13  | 12.96   | 14.64        |

| 4 <sup>th</sup> inexact design | 0.63  | 7.308   | 4.604        |

| 5 <sup>th</sup> inexact design | 0.25  | 7.092   | 1.773        |

**Fig. 11.** First Reduction step of a 6×6 ternary multiplication. (a) with exact carry. (b) with inexact carry

$$R' = G' = B' = 0.333 \times R + 0.5 \times G + 0.1666 \times B \tag{6}$$

In this equation, R, G, and B are red, green and blue indices of the input image that construct the pixel's color and R', G' and B' are those of the grayscale output image.

The proposed exact and approximate multipliers have been used in the multiplication of these values. As Fig. 13 shows, all of the design's results (except the first inexact design) have acceptable outputs, especially the fifth method, because its NED value is less than the others. PSNR values of this example are also shown in Table 8. In this example, the inexact designs do not have significant differences when compared to the exact design except the first design, which has lower PSNR value. PSNR metric shows this fact. Hence, imprecise designs are outstanding candidates that could be used instead of exact methods that have high power and delay. As Table 8 represents, the PSNR values of all inexact multipliers (except the first design) are acceptable for most of the application as it is mentioned in [35] that a typical PSNR value ranges between 20 dB to 40 dB.

These image processing applications are some of the thousands of applications in which an approximate multiplier could be utilized. Image and voice filtering, FFT algorithms, watermarking, and image reconstruction with NMF algorithms are some of those applications.

Table 8 PSNR Values

| Dociona                | PSNR (dB)             |                       |  |

|------------------------|-----------------------|-----------------------|--|

| Designs                | Image multiplication  | RGB to Grayscale      |  |

| 1st design             | (16.43, 19.85, 21.86) | (19.21, 19.21, 19.21) |  |

| 2 <sup>nd</sup> design | (22.44, 25.85, 27.81) | (25.19, 25.19, 25.19) |  |

| 3 <sup>rd</sup> design | (28.42, 31.78, 33.63) | (31.04, 31.04, 31.04) |  |

| 4 <sup>th</sup> design | (28.04, 31.58, 33.31) | (31.17, 31.17, 31.17) |  |

| 5 <sup>th</sup> design | (31.07, 32.29, 33.50) | (31.81, 31.81, 31.81) |  |

#### 6. Conclusion

This paper proposed a new CNFET-based exact ternary one-digit multiplier, which improved the best previous design in terms of delay and energy consumption by up to 2X and 6X, respectively. By considering the usefulness of a multiplier cell in image processing applications, inexact multipliers were proposed in this paper and have been utilized in some image processing applications. As the results show, the suggested approximate cells can be employed in DSP applications to have an energy-efficient design with an acceptable error value. We simulated all the proposed designs under different operational conditions. We compared the results of our designs with the previous methods. The results confirm the improvement of the proposed designs over the state-of-the-art designs in terms of energy efficiency.

**Fig. 12.** Image multiplication results. (a) first input. (b) second input. (c) exact design. (d) 1st design. (e) 2nd design. (f) 3rd design. (g) 4th design. (h) 5th design.

Fig. 13. RGB to grayscale results. (a) input image. (b) exact output. (c)  $1^{st}$  design. (d)  $2^{nd}$  design. (e)  $3^{rd}$  design. (f)  $4^{th}$  design. (g)  $5^{th}$  design.

## References

- 1. L. B. Kish, "End of Moor's law: thermal noise death of integration in micro and nanoelectronics," in Physics Letters A 305, pp. 144-149, 2002.

- 2. J. K. Chen, T. Akeyoshi, and K. Maezawa. "Monostable-bistable transition logic elements (MOBILEs) based on monolithic integration of resonant tunneling diodes and FETs," in Japanese Journal of Applied Physics 34, no. 2S, p. 1199, 1995.

- 3. P. Hadley, G. Lientschnig, and M-Ji. Lai, "Single-electron transistors," in Conference Series-Institute of Physics, vol. 174. pp. 125-132, Philadelphia, Institute of Physics, 1999.

- 4. M. B. Tahoori, J. Huang, M. Momenzadeh, F. Lombardi, "Testing of quantum cellular automata," in IEEE Trans. Nanotechnology., vol. 3, no. 4, pp. 432-442, 2004.

- 5. E. Shahrom and S. A. Hosseini, "A new low power multiplexer based ternary multiplier using CNTFETs," *AEU-International Journal of Electronics and Communications*, vol. 93, pp. 191-207, 2018.

- 6. L. Ding, Z. Zhang, S. Liang, T. Pei, S. Wang, Y. Li, W. Zhou, J. Liu, and L. M. Peng, "CMOS-based carbon nanotube pass transistor logic integrated circuits," in Nature Communications, vol. 3, no. 677, 2012.

- 7. S. Tabrizchi, F. Sharifi, A.-H. Badawy, and Z. Saifullah, "Enabling energy-efficient ternary logic gates using CNFETs," in 2017 IEEE 17th International Conference on Nanotechnology (IEEE-NANO), 2017, pp. 542-547.

- 8. S. Lin, Y. Kim and F. Lombardi, "CNTFET-based design of ternary logic gates and arithmetic circuits," in IEEE Trans. Nanotechnology., vol. 10, no. 2, pp. 217-225, 2011.

- 9. K. C. Smith, "A multiple valued logic: a tutorial and appreciation," in Computer, vol. 4, pp. 17-27, 1988.

- 10. S. L. Hurst, "Multiple-valued logic its status and future," in IEEE Trans. Computer., vol. 33, no. 12, pp. 1160–1179, 1984.

- 11. B. Hayes, "Third base," in American Scientist, vol. 89, no. 6, pp. 490-494, 2001.

- 12. F. Sharifi, Z. Saifullah, and A.-H. Badawy, "Design of adiabatic MTJ-CMOS hybrid circuits," in 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), 2017, pp. 715-718

- 13. J. Han and M. Orshansky, "Approximate computing: an emerging paradigm for energy-efficient design," in 18th IEEE European Test Symposium (ETS), pp. 1-6, 2013.

- 14. M. C. Lemme, T. J. Echtermeyer, M. Baus and H. Kurz, "A graphene field effect device," in IEEE Electron Device Letters, vol. 28, no. 4, 2007.

- 15. R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris, "Single-and multi-wall carbon nanotube field-effect transistors," in Applied Physics Letters, vol. 73, no. 7, pp. 2447-2449, 1998.

- 16. A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, "Logic circuits with carbon nanotube transistors," in Science, vol. 294, no. 5545, pp. 1317-1320, 2001.

- 17. F. Sharifi, M. H. Moaiyeri, K. Navi and N. Bagherzadeh, "Robust and energy-efficient carbon nanotube FET-based MVL gates: a novel design approach," in Microelectronics Journal, vol. 46, no. 12, pp. 133-1342, 2015.

- 18. I. O'Connor, J. Liu, F. Gaffiot, F. Prégaldiny, C. Lallement, C. Maneux, J. Goguet, S. Frégonèse, T. Zimmer, L. Anghel, and T. T. Dang, "CNTFET modeling and reconfigurable logic-circuit design," in Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 54, no. 11, pp. 2365-237, 2007.

- 19. L-C. Qin, "Determination of the chiral indices (n, m) of carbon nanotubes by electron diffraction," in Physical Chemistry Chemical Physics, vol. 9, no.1, pp. 31-48, 2007.

- K. Y. Bok, Y. B. Kim, F. Lombardi, "Novel design methodology to optimize the speed and power of the CNTFET circuits" in Proc. IEEE Int. Midwest Symp on Circuits and Systems, Cancun, Mexico, pp. 1130– 1133, 2009.

- 21. S. Tabrizchi, M. Taheri, K. Navi, and N. Bagherzadeh, "Novel CNFET ternary circuit techniques for high-performance and energy-efficient design," IET Circuits, Devices & Systems, 2018.

- 22. J. Deng, "Device modeling and circuit performance evaluation for nanoscale devices: silicon technology beyond 45 nm node and carbon nanotube field-effect transistors," Doctoral Dissertation. Stanford University, 2007.

- 23. J. Deng and H.-S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application-part I: model of the intrinsic channel region," in IEEE Trans. Electron Devices., vol. 54, no. 12, pp. 3186-3194, 2007.

- 24. J. Deng and H.-S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application-part II: full device model and circuit performance benchmarking," in IEEE Trans. Electron Devices., vol. 54, no. 12, pp. 3195-3205, 2007.

- 25. A. Daraei and S. A. Hosseini, "Novel Energy-Efficient and High-Noise Margin Quaternary Circuits in Nanoelectronics," AEU-International Journal of Electronics and Communications, 2019.

- 26. M. H. Moaiyeri, A. Dosstaregan, and K. Navi, "Design of energy-efficient and robust ternary circuits for nanotechnology," in IET Circuits, Devices & Systems, vol. 5, no. 4, pp. 1-12, 2011.

- 27. S. Lin, Y-B. Kim, and F. Lombardi, "CNTFET-based design of ternary logic gates and arithmetic circuits," in IEEE Trans. Nanotechnology., vol. 10, no. 2, pp. 217-225, 2011.

- 28. Y. S. Mehrabani, R. F. Mirzaee, Z. Zareei, and S. M. Daryabari, "A novel high-speed, low-power CNTFET-based inexact full adder cell for image processing application of motion detector," *Journal of Circuits, Systems and Computers*, vol. 26, p. 1750082, 2017.

- 29. B. C Paul, S. Fujita, M. Okajima, T. H. Lee, H. –S. Philip Wong, Y. Nishi, "Impact of a process variation on nanowire and nanotube device performance," in IEEE Trans. Electron Devices., vol. 54, no. 9, pp. 2369-2376, 2007.

- 30. R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: modeling and analysis of circuits for approximate computing," in Proceedings of the International Conference on Computer-Aided Design. IEEE Press, pp. 667-673, 2011.

- 31. A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication," *IEEE Transactions on Computers*, vol. 64, pp. 984-994, 2015.

- 32. O. Akbari, M. Kamal, A. Afzali-Kusha, and M. Pedram, "Dual-quality 4: 2 compressors for utilizing in dynamic accuracy configurable multipliers," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 25, pp. 1352-1361, 2017.

- 33. J. Liang, J. Han, and F. Lombardi, "New metrics for the reliability of approximate and probabilistic adders," in IEEE Trans. Computers., vol. 62, no. 9, pp. 1760-1771, 2013.

- 34. T. Kumar and K. Verma, "A theory based on conversion of RGB image to gray image," in International Journal of Computer Applications, vol. 7, no. 2, pp. 7-10, 2010.

- 35. D. Aggarwal and K. Singh Dhindsa, "Effect of embedding watermark on compression of the digital images," in Journal of Computing, vol. 2, no. 2, pp. 5-8, 2010.