1 Article

# 2 Electrical Characteristics and Reliability of Nitrogen-

# 3 Stuffed Porous Low-k SiOCH/ Mn<sub>2</sub>O<sub>3-x</sub>N/Cu

# 4 Integration

- 5 Yi-Lung Cheng<sup>1\*</sup>, Yu-Lu Lin<sup>1</sup>, Chih-Yen Lee<sup>1</sup>, Giin-Shan Chen<sup>2</sup>, and Jau-Shiung Fang<sup>3</sup>

- 6 Department of Electrical Engineering, National Chi-Nan University, Nan-Tou, 54561, Taiwan, R.O.C.

- <sup>2</sup> Department of Materials Science and Engineering, Feng Chia University, Taichung, 40724, Taiwan, R.O.C.

- 8 <sup>3</sup> Department of Materials Science and Engineering, National Formosa University, Huwei, 63201, Taiwan, R.O.C.

- \* Correspondence: yjcheng@ncnu.edu.tw; TEL.: +886 49 2910960 4987; Fax: +886 49 2917810.

Abstract: In our previous study, a novel barrier processing on a porous low-dielectric constant (low-*k*) film was developed: an ultrathin Mn oxide on a nitrogen-stuffed porous carbon-doped organosilica film (p-SiOCH(N)) as a barrier of the Cu film was fabricated. To form a better barrier Mn<sub>2</sub>O<sub>3-x</sub>N film, an additional annealing at 450°C was implemented. In this study, the electrical characteristics and reliability of this integrated Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si structure is investigated. The proposed Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si capacitors exhibited poor dielectric breakdown characteristics in the as-fabricted stage, although, less degradation was found after thermal stress. Moreover, its time-dependence-dielectric-breakdown electric-field acceleration factor slightly increased after thermal stress, leading to a larger dielectric lifetime in a low electric-field as compared to other MIS capacitors. Furthermore, its Cu barrier ability under electrical or thermal stress was improved. As a consequent, the proposed Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiCOH(N) scheme is a promising integrity for back-end-of-line interconnects.

**Keywords:** Porous low-dielectric-constant; Barrier; MnO<sub>x</sub>; Electrical characteristics; Reliability; Electric-field acceleration factor; TDDB.

### 1. Introduction

Copper (Cu) conductor and porous low-dielectric-constant (low-*k*) dielectric insulator have been used as back-end-of-line (BEOL) interconnect materials, accelerating the high-speed requirement for advanced microelectronic devices by the reduction of resistance-capacitance (RC) time delay [1-3]. However, due to the intrinsically structural and bonding weakness of porous dielectric materials, their integration with Cu is a challenging topic.

Poor adhesion and high diffusivity of Cu are the critical issues, causing integration difficulty of Cu and porous low-*k* dielectric materials [4,5]. Hence, a liner/barrier is interposed between Cu line and porous dielectric insulator. Currently, a dual layer of Ta/TaN liner/barrier is used by industry communities [6-8]. With the progress of advanced technological nodes, the dimensions of BEOL interconnects are continuously scaling down, and the associated thickness-thinning for Ta/TaN dual layer results in its failure to maintain effective barrier performance against Cu diffusion. Under such a scenario, Ta/TaN dual layer typically deposited by sputtering deposition, occupies a larger portion of Cu line volume, leading to a huge increase in overall resistivity of lines and vias, as well as a poor step coverage of trenches and vias [9].

Therefore, an alternative to replace the currently used Ta/TaN barrier materials and process for the aggressively scaled-down interconnects is required to overcome the above mentioned issues, among which self-forming barrier process, chemical vapor deposition (CVD), and atomic layer deposition (ALD) technologies have been proposed [10-12]. Moreover, manganese (Mn), ruthenium

(Ru), and cobalt (Co), along with their derivatives, are considered as potential alternative barrier materials to substitute Ta/TaN dual layer [13-15].

In light of the aforementioned studies of metal-based barriers, we have recently proposed a novel barrier process for Cu metallization [16] by firstly performing high-pressure nitrogen stuffing of a porous low-*k* SiOCH dielectric. Then, a 2-nm-thick Mn oxide film was deposited in a controlled (oxygen-containing) sputtering gas. Subsequently, an Ar/H<sub>2</sub> forming-gas treatment was performed on the MnO<sub>x</sub>/porous SiOCH stacked layer to enhance its thermal stability. Such a thermal stabilization treatment results in the transformation of Mn<sub>2</sub>O<sub>3</sub> and its reaction with stuffed gaseous, ultimately forming an effective ultrathin barrier denoted as Mn<sub>2</sub>O<sub>3-x</sub>N.

This proposed barrier process is an effective barrier against Cu diffusion under thermal stress. However, its impact on the electrical characteristics and reliability of the porous low-*k* SiOCH dielectric remains unclear. Therefore, the purpose of this study is to investigate this topic in details. The barrier capacities under thermal and electrical stresses for the proposed barrier process are also evaluated.

# 2. Experiments

The low dielectric-constant (k) material used in this study was porous SiOCH (abbreviated hereafter as p-SiOCH), which was deposited on a p-type (100) Si wafer by an Applied Materials plasma-enhanced chemical vapor deposition system using diethoxymethylsilane (DEMS), oxygen (O<sub>2</sub>), and alpha-terpinene (ATRP) porogen as precursors [17]. The thickness and k value of p-SiOCH dielectric films were ~100 nm and 2.560, respectively.

First, a p-SiOCH sample was placed into a vacuum furnace evacuated by a scroll pump to background pressure of approximately 1 Pa. The p-SiOCH film was then stuffed at 450°C for 5 min under 4 atm of surrounding nitrogen, hereafter denoted as p-SiOCH(N). Subsequently, a 2-nm-thick layer of Mn<sub>2</sub>O<sub>3</sub> was deposited onto p-SiOCH(N) through a shadow mask by sputtering a Mn target under a controlled Ar/O<sub>2</sub> oxidative atmosphere. The resultant sample, denoted as Mn<sub>2</sub>O<sub>3</sub>/p-SiOCH(N)/Si, was subjected to stabilization annealing at 450°C in an Ar/H<sub>2</sub> (5%) forming gas for 60 min, converting the Mn<sub>2</sub>O<sub>3</sub> to Mn<sub>2</sub>O<sub>3-x</sub>N [16]. Finally, a 50-nm-thick Cu film was thermally evaporated onto the stacked sample also through a shadow mask. The area of the formation Cu electrode was 9.0 x  $10^{-4}$  cm<sup>2</sup>. Based on this process flow, metal-insulator-silicon (MIS) capacitors with a Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si stacked structure were fabricated for electrical characteristics and reliability measurements. Other MIS capacitors with Cu/p-SiOCH/Si and Cu/Mn<sub>2</sub>O<sub>3</sub>/p-SiOCH/Si stacked structures were also fabricated for a reference.

*C-V* plots of dielectric films were measured by a semiconductor parameter analyzer (HP4280A), using applied voltages in the range from -40 V to 40 V and -40 V and an operation frequency of 1 MHz. The k value of each dielectric film was derived from the measured accumulation capacitance value (C) of the associated C-V plots, along with the values of Cu electrode area (A) and thickness (d) of the dielectric film, using the equation: C=&kA/d, where &k0 is absolute capacitivity in vacuum (8.85 x 10-12 F/m). Furthermore, leakage currents of a dielectric film were measured versus applied voltages by a ramped-voltage-stress (RVS) method with a ramping rate of 0.1 V/s, from which a breakdown field was derived. Dielectric breakdown time was detected from time-dependent-dielectric-breakdown (TDDB) measurements by applying a constant electric voltage (field). RVS and TDDB tests were performed by an electrometer (Keithley, 6517A). All measurements were performed at room temperature (25°C). Electrical aspect of diffusion barrier properties for Cu/Mn2O3-xN/p-SiOCH(N)/Si structure was evaluated by thermal stress at 450°C for 2 h and electrical stress at 1.5-3.0 MV/cm

#### 3. Results and Discussion

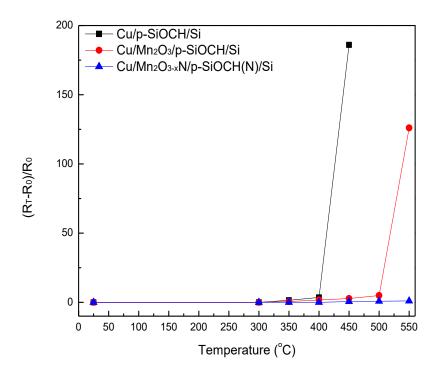

By recording the plots of relative changes of sheet resistance  $[(R_T-R_0)/R_0)]$  versus annealing temperatures (250-650°C) for three representative samples, as shown in Figure 1, the effectiveness of Mn<sub>2</sub>O<sub>3</sub> and Mn<sub>2</sub>O<sub>3-x</sub>N layers as barriers of Cu can be evaluated from comparing the values of temperature corresponding to the onsets of abrupt rise in relative resistance. Notably,  $R_0$  is the sheet

3 of 12

resistance of a pristine stacked samples covered by a continuous Cu film, which is thus equalent to the sheet resistance of the Cu conducting film, while R<sub>T</sub> is the sheet resistance of the same sample after annealing. Thermal annealing tends to cause Cu to agglomerate and/or penetrate the manganese oxide barrier into the underlying p-SiOCH films [18], leading to failure of the metallized layers. Therefore, the values of (R<sub>T</sub>-R<sub>0</sub>)/R<sub>0</sub> reflect the integration of the Cu layers, and thus the magnitude of threshold temperatures serves to provide capacity of barrier layers. According to Fig. 1, the threshold temperatures for Cu/p-SiOCH (barrier-free) samples and identical samples interposed with a Mn<sub>2</sub>O<sub>3</sub> or Mn<sub>2</sub>O<sub>3-x</sub>N barriers are 450°C, 550°C, >550°C, respectively. Notably, the limit of temperature for BEOL interconnect processing is around 400°C. Therefore, the slight increase in (R<sub>T</sub>-R<sub>0</sub>)/R<sub>0</sub> at the threshold temperature (400 °C) for Cu/p-SiOCH indicates the necessity of a barrier. Comparing the magnitudes of threshold temperature in Fig. 1 also suggests that Mn<sub>2</sub>O<sub>3-x</sub>N outperforms Mn<sub>2</sub>O<sub>3</sub>; it exhibits an outstanding barrier capacity with a significantly higher threshold temperature (650°C versus 550 °C), even with a thickness of only 2 nm.

**Figure 1.** Variation of relative electrical resistivity as a function of annealing temperature for various Cu-gate MIS capacitors.

Table 1 lists the results of tape testing of the as-deposited and annealed (450 °C for 2 h) samples, including Cu/p-SiOCH/Si, Cu/Mn<sub>2</sub>O<sub>3</sub>/p-SiOCH(N)/Si, and Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si. The size of the tested sample films was 6 x 6 square regions. For the pristine and annealed (barrier-free) Cu/p-SiOCH/Si samples, no square or only a few square regions were left after tape testing, indicating delamination of Cu films due to poor adhesion. For the pristine Cu/Mn<sub>2</sub>O<sub>3</sub>/p-SiOCH(N)/Si samples, about 20 % square regions were delaminated. After annealing, the delamination percentage was slightly increased to approximately 35%, indicating that thermal annealing degrades the interfacial adhesion. On the contrary, all the 36 square regions in the Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si samples remained intact before and after annealing, indicating that, apart from acting as a barrier, the 2 nm-thick Mn<sub>2</sub>O<sub>3-x</sub>N layer serves as adhesion promoter, thus markedly increasing adhesion of Cu films. The significant enhancement of interfacial adhesion by Mn<sub>2</sub>O<sub>3-x</sub>N is attributed to a chemical interaction between contacted layers and the resulting nitrogen-related bonding between Cu metal electrode and p-SiOCH substrate. The obtained result is similar to the reported finding by Selvaraju

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

4 of 12

et al., indicating that a noticeable improvement in adhesion of Cu to the underlying SiO<sub>2</sub> was observed by the use of Mn-nitride with a nitrogen content of just 5% [19].

## Table I: Tape test results of various MIS capacitors before and after annealing.

|           | Cu/p-SiOCH/Si | Cu/Mn <sub>2</sub> O <sub>3</sub> /p-SiOCH/Si | Cu/Mn <sub>2</sub> O <sub>3-x</sub> N/p-SiOCH(N)/Si |

|-----------|---------------|-----------------------------------------------|-----------------------------------------------------|

| As dep.   | Fail          | ~ 20 % Fail                                   | Pass                                                |

| 450°C/2 h | N/A           | ~ 35 % Fail                                   | Pass                                                |

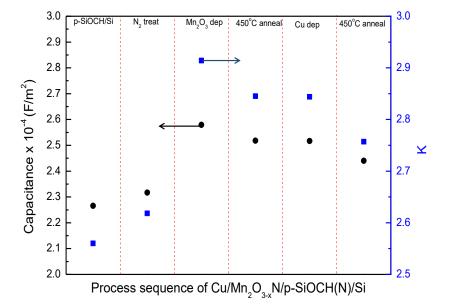

It is important for the underlying p-SiOCH layers to keep a low-k feature after completing the fabrication of the Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si structure, involving nitrogen stuffing, Mn<sub>2</sub>O<sub>3</sub> deposition, stabilization annealing [converting Mn<sub>2</sub>O<sub>3</sub> to Mn<sub>2</sub>O<sub>3-x</sub>N], Cu deposition. Therefore, the variations of the accumulation capacitances (C) and corresponding k values of the p-SiOCH layers after the aforementioned treatment sequence were determined using C-V measurements, as plotted in Figure 2. For the pristine p-SiOCH film, the accumulation capacitance per area was 2.266 X 10-4 F/m<sup>2</sup>, corresponding to a k value of 2.560. After a nitrogen-stuffing treatment at 450°C/4 atmosphere for 5 min, the accumulation capacitance slightly increased to 2.317 X 10<sup>-4</sup> F/m<sup>2</sup>, leading to an increase of k value to 2.618. Notably, the high-pressure nitrogen treatment results in the stuffing of the pores within the p-SiOCH film [denoted as p-SiOCH(N)] with physisorbed nitrogen atoms (or molecules) [16], thus rendering only a 2.26 % increase in k value. After sputter deposition of a 2-nm-thick Mn<sub>2</sub>O<sub>3</sub> barrier, a large increase in accumulation capacitance of the p-SiOCH(N) film was measured, associated with a marked increase of k value to 2.914 (11.30 %). This increase is attributed to two mechanisms: one is plasma-induced damage on the p-SiOCH(N) film during the deposition of Mn<sub>2</sub>O<sub>3</sub> barrier [20]; another is the relative high k value of 5.10 of the coated Mn<sub>2</sub>O<sub>3</sub> [21,22]. After annealing with Ar/H<sub>2</sub> forming gas at 450°C for 1 h, Mn<sub>2</sub>O<sub>3</sub> film became more stabilized. Moreover, the nitrogen stuffed into the pores in the p-SiOCH(N) film was released and react with Mn<sub>2</sub>O<sub>3</sub> film to form Mn<sub>2</sub>O<sub>3</sub>xN layer. This transformation reduced the capacitance, resulting in a reduction of the *k* value to 2.845. The capacitance and k value slightly decreased as Cu gate was formed. Further annealing (450°C/2 h) of the Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si capacitor in an N<sub>2</sub> environment made the k value slightly decrease to 2.757. In is worth mentioning that the k value of Cu/p-SiOCH/Si (without a barrier) capacitors decreased upon annealing with a decreasing magnitude of 0.214, which could be caused by Cu diffusion [23]. As a result, a lower decrease in the k value for Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si capacitor upon annealing is indicative of greater Cu barrier capacity of the Mn<sub>2</sub>O<sub>3-x</sub>N layer.

153154

155

**Figure 2.** Variations in capacitance and dielectric constant during Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si integration.

172

173

174

175

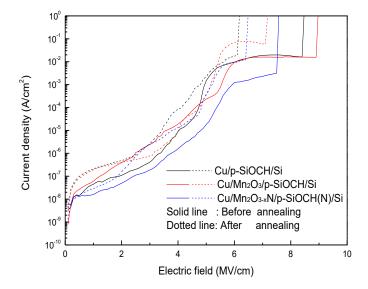

Figure 3 plots the I-E curves of various Cu-gate capacitors before and after annealing. The negative-polarity voltage was applied and transformed to the electric field (E) by dividing it by the thickness of the p-SiOCH films. For all Cu-gate capacitors, the leakage currents increased with the electric fields, typically followed by a plateau, and then suddenly jumped. The applied field on the threshold of this jump is defined as a breakdown field of the p-SiOCH films. Prior to annealing and before breakdown of the p-SiOCH films, leakage currents of the capacitor samples without and with a Mn<sub>2</sub>O<sub>3</sub> barrier layer were comparable, while those of the Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si capacitors were substantially reduced by 1-2 orders. This finding indicates that the Mn<sub>2</sub>O<sub>3-x</sub>N layer has a better barrier performance than the Mn<sub>2</sub>O<sub>3</sub> layer, thus significantly improving electrical properties of p-SiOCH films. Furthermore, the conduction of leakage currents in dielectric materials is mainly through bulk transportation and surface migration of Cu atoms and ions. Therefore, leakage currents are ascribed to various factors, such as chemical structures of dielectrics, incorporated impurities, and metal-dielectric interfaces [24]. Since the Cu-gate capacitors studied here had the identical p-SiOCH film, the decrease in leakage current for the Cu-gate capacitor with a Mn<sub>2</sub>O<sub>3-x</sub>N barrier layer is attributed to the improvement of metal-dielectric interfaces, thereby retarding surface migration of Cu atoms. After annealing, the leakage currents of all Cu-gate capacitors increased over the whole range of applied fields. The increase was most pronounced for the barrier-free samples, while the capacitor samples with a Mn<sub>2</sub>O<sub>3-x</sub>N barrier layer exhibited the least increase in leakage currents. This implies that the conduction via metal-dielectric interface is the dominant mechanism for leakage current.

176177

**Figure 3.** *J-E* plots of various Cu-gate MIS capacitors before and after annealing at 450°C for 2 h.

194

195

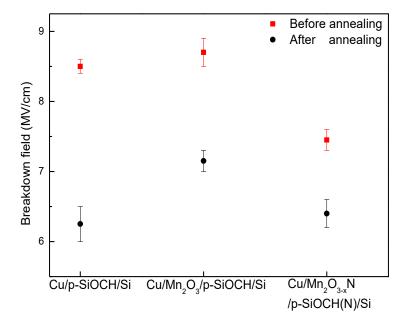

Figure 4 compares the breakdown fields of p-SiOCH films in various Cu-gate capacitors before and after annealing. Ten samples were measured for each condition. Before annealing, the magnitudes of breakdown fields follow the order of: Mn<sub>2</sub>O<sub>3</sub> capped sample (8.74 MV/cm) > barrierfree sample (8.46 MV/cm) > Mn<sub>2</sub>O<sub>3-x</sub>N capped sample (7.48 MV/cm). This trend is different from the result of leakage currents, suggesting that leakage current is not the necessary condition to trigger the breakdown of a dielectric film, which yields a reduced value of breakdown field as its molecular bonds are break up. For the p-SiOCH film in the Cu-gate capacitor with Mn2O3-xN barrier layer, an additional annealing at 450°C for 1 h was performed on it before Cu gate deposition. The broken bonds were expected, thereby reducing the breakdown strength. Additionally, the barrier-free sample had a lower breakdown filed than the Mn<sub>2</sub>O<sub>3</sub> capped sample due to the migration of Cu atoms/ions into the p-SiOCH film during Cu gate deposition. This suggests that a barrier is required for Cu/p-SiOCH integrity. After annealing, the breakdown fields of p-SiOCH films in all the capacitor samples were reduced. The largest magnitude of decreasing occurred in the barrier-free capacitor sample due to by bond breakage of p-SiOCH and Cu migration under thermal stress. With a Mn<sub>2</sub>O<sub>3</sub> or Mn<sub>2</sub>O<sub>3-x</sub>N barrier, Cu migration was inhibited. As a result, the reduction in the breakdown field was not as large as that obtained from the barrier-free sample. In the case of Mn<sub>2</sub>O<sub>3-x</sub>N barrier, its magnitude of decreasing was the lowest, but the breakdown field variation was the smallest, suggesting that the Mn<sub>2</sub>O<sub>3-x</sub>N layer is the best barrier against Cu thermal diffusion.

Figure 4. Comparison of breakdown fields of various Cu-gate MIS capacitors before and after annealing.

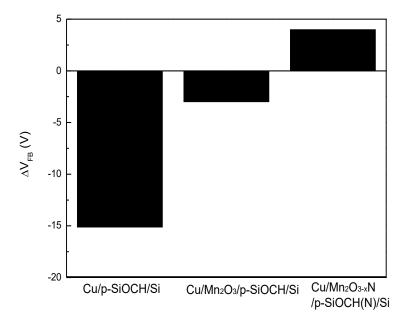

After thermal stress, *C-V* characteristics were measured again. Normalized *C-V* curves for the barrier-free and barrier capped capacitor samples before and after thermal stress (450°C/2 h) were compared and the shifts of their flat-band voltages (V<sub>fb</sub>) were determined, as presented in Figure 5. The data presented here are the average values from 3 measurements for different capacitor samples. After thermal stress, the barrier-free capacitor sample exhibited a larger V<sub>fb</sub> shift with negative direction. Additionally, its accumulation capacitance obviously decreased. These features represent the diffusion of Cu ions into the p-SiOCH film during thermal stressing [25]. For the Mn<sub>2</sub>O<sub>3</sub> capped capacitor sample, V<sub>fb</sub> still shifted toward negative voltage, but the shifting magnitude was obviously reduced. This result indicates that the diffusion of Cu ions into the p-SiOCH film is blocked by the Mn<sub>2</sub>O<sub>3</sub> barrier, although, its blocking efficiency cannot reach 100 %. On the other hand, for the Mn<sub>2</sub>O<sub>3-x</sub>N capped capacitor sample, a small V<sub>fb</sub> shift was seen, but the direction was toward positive voltage. This positive shift of V<sub>fb</sub> indicates the presence of negative charges, but not Cu diffusion into the p-SiOCH film, which in turn suggests that the retardation of Cu diffusion under thermal stress is ascribed to Mn<sub>2</sub>O<sub>3-x</sub>N barrier and nitrogen-stuffed p-SiOCH film.

213214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

**Figure 5.** Shift of flatband voltage (V<sub>FB</sub>) of various Cu-gate MIS capacitors after being subjected to thermal stress.

In sum, Cu/Mn2O<sub>3-x</sub>N/p-SiOCH(N) integration has been demonstrated to possess the best capacity against Cu thermal diffusion. However, under an electrical stress, Cu ions would drift into the p-SiOCH(N) (porous) dielectric film. Indeed, such phenomena is more pronounced for a porous film [26,27]. As Cu gate is stressed with a positive bias, Cu ions are generated and then drift into a dielectric film under the external electric field. After electrical stress, *I-V* characteristics with sweep at negative voltage were measured. The measured current is the response of both injection carriers and ionic currents.

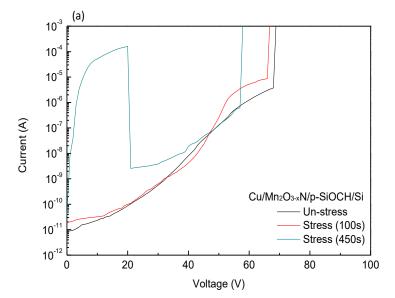

Figure 6 (a) plots I-V curves of Mn<sub>2</sub>O<sub>3-x</sub>N capped capacitor samples before and after electrical stress (2.0 MV/cm) for various times. After electrical stress, the leakage current increased. Moreover, as the stressing time reached a certain value, a hump appeared at the voltage range from 0 to -20 V. The increase in the leakage currents is ascribed to the stress-induced trapping of within the p-SiOCH films. The appearing hump is mainly caused by ionic currents due to the migration of Cu ions. Under positive-polarity electrical stresses, Cu ions were generated, subsequently drifting into the p-SiOCH films following an assistance of the external electric fields. Then, during the application of negativepolarity voltages, the drifted Cu ions reversed back to the metal gate. Therefore, the presence of such a hump can be an indicator of Cu barrier capacity under an electrical stress. In this study, "Cu diffusion time" is defined as the stressing time of the positive-polarity stress required to produce this hump. A longer Cu diffusion time means a better Cu barrier capacity. Figure 6 (b) compares the Cu diffusion times of the three capacitor sample types as a function of electric field. The Cu diffusion times decrease with increases of the electric field for all the samples, indicating that a high electric field generates more Cu ions with faster drift rates. As expected, Cu-gate capacitors without a Mn<sub>2</sub>O<sub>3</sub> barrier layer have the lowest Cu diffusion time. Cu-gate capacitors with Mn₂O₃ and Mn₂O₃-xN barrier layers have a longer and comparable Cu diffusion time, indicating that both barrier layers (Mn<sub>2</sub>O<sub>3</sub> and Mn<sub>2</sub>O<sub>3-x</sub>N) have similar capacity in retarding Cu migration against electrical stress.

**Figure 6.** (a) *I-V* curves of Cu-gate MIS capacitor with Mn<sub>2</sub>O<sub>3-x</sub>N barrier before and after electrical stress (2.0 MV/cm) for various times; (b) Cu diffusion time of various Cu-gate MIS capacitors under electrical stress as function of electric-field.

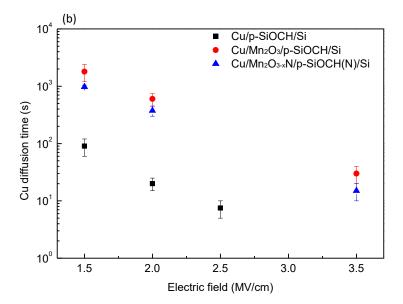

The long-term reliability of p-SiOCH films in the Cu-gate MIS capacitors with various barriers was evaluated by comparing the results of TDDB tests with those of barrier-free samples. During a TDDB test (at 25°C), the samples were stressed by a constant electric field and the leakage current was monitored until dielectric breakdown. The time-to-fail (TTF) was recorded as a leap in leakage current by at least 3 orders of magnitude. Herein, At least three values of electric fields were used for stressing and twelve MIS capacitors were measured for each condition, and the data of median TTFs for various samples (before and after annealing) are presented in Figure 7. Similar to the results of the breakdown fields measured from *I-V* measurements (Fig. 4), the measured TTFs display the same order. That is, the p-SiOCH film in the Mn2O3 capped MIS capacitor exhibited the largest TTFs as compared to those in other MIS capacitors. On the contrary, the Cu/Mn2O3-xN/p-SiOCH(N)/Si capacitor had the shortest TTFs. After annealing, the TTFs of the p-SiOCH films in all the Cu-gate MIS capacitors were reduced. Similarly, the p-SiOCH film in the Mn2O3 capped capacitor had the

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

10 of 12

largest TTFs. On the other hand, thermal annealing caused the lowest reduction in TTFs for the  $Cu/Mn_2O_{3-x}N/p$ -SiOCH(N)/Si capacitor. As a result, its TTFs were slightly larger than those obtained from the barrier-free samples. The result reveals that a barrier is required to ensure reliability for Cu and p-SiOCH integrity.

**Figure 7.** TTFs of p-SiOCH film in various Cu-gate MIS capacitors as function of applied electric-field before and after annealing.

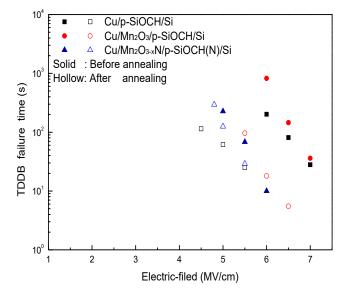

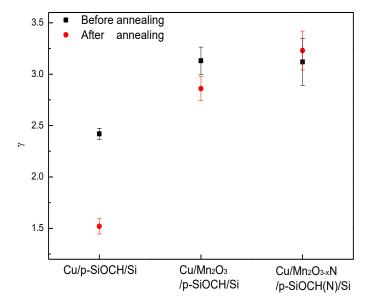

Annealing results in a reduction of TTFs; it also causes a change of slopes in the plots of TTF versus the stressing filed, representing that the annealing causes an alteration of electric-field acceleration factors. In this study, the E model [TTF = A exp  $(-\gamma E)$ ], which is the key to bond-breakage mechanism, was used to describe the dielectric breakdown behavior [28,29]. In the equation, yis the electric-field acceleration factor, representing the extent to which TTF (derived from TDDB tests) is affected by electric fields. A largerγvalue means that TTF has a stronger dependence on electric fields. Moreover, it provides a longer lifetime in lower operation fields. The yvalues extracted from the plots in Fig. 7 for the three different capacitor types before and after annealing are plotted in Figure 8. The barrier-free capacitor sample before annealing had a loweryvalue (2.42), which was significantly reduced to 1.62 (the lowest). The decrease of yvalue is believed to be caused by the drifting of Cu ions [25]. Both capacitor samples with Mn<sub>2</sub>O<sub>3</sub> and Mn<sub>2</sub>O<sub>3-x</sub>N barriers had the similary value of 3.12~3.13. Upon annealing, a decrease in γvalue to 2.86 was found in the Mn<sub>2</sub>O<sub>3</sub> capped capacitor, whereas a slight increase to 3.23 occurred for the Mn<sub>2</sub>O<sub>3-x</sub>N capped capacitor, indicating better Cu barrier efficiency of the Mn<sub>2</sub>O<sub>3-x</sub>N layer. The largeyvalue for the Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si capacitor has a dramatic benefit to promote a dielectric lifetime in a low operation field. As a result, the lifetimes of the Cu-gate MIS capacitor with the Mn<sub>2</sub>O<sub>3-x</sub>N barrier layer surpass that obtained from the Cu MIS capacitors with the MnOx barrier layer when the operation field is lower than 4.06 MV/cm.

281282

283

284

285

286

287

288

289

290

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

Figure 8. Electric-field acceleration factor of various Cu-gate MIS capacitors before and after annealing.

#### 5. Conclusion

The electrical characteristics and reliability of the integrated Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si structure have been investigated in this study. In the as-fabricated stage, Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N)/Si structure exhibited poor dielectric breakdown characteristics, although, less degradation was observed after thermal stress. Moreover, its Cu barrier efficiency and TDDB electric-field acceleration factor were improved. Consequently, the proposed Cu/Mn<sub>2</sub>O<sub>3-x</sub>N/p-SiOCH(N) is a promising integration processing for Cu/porous low-*k* interconnects.

- Acknowledgments: The author would like to thank the National Science Council of the Republic of China, Taiwan, for financially supporting this research under Contract No. MOST-107-2221-E-260-010-MY2.

- 293 **Conflicts of Interest:** The authors declare no conflict of interest.

### References

- [1] A. Grill, Annu. Rev. Mater. Res. 39 (2009) 49.

- [2] K. Maex, M.R. Baklanov, D. Shamiryan, F. Iacopi, S.H. Brongersma, and Z.S. Yanovitskaya, J. Appl. Phys. 93 (2003) 8793.

- [3] A. Grill, S.M. Gates, T.E. Ryan, S.V. Nguyen, D. Priyadarshini, Appl. Phys. Rev. 1 (2014) 011306.

- [4] S. Tsukimoto, T. Morita, M. Moriyama, K. Ito, M. Murakami, Formation of Ti diffusion barrier layers in Thin Cu(Ti) alloy films, *J. Electron. Mater.* **34** (5) (2005) 592.

- [5] I. Fisher, M. Eizenberg, Copper ion diffusion in porous and nonporous SiO<sub>2</sub>-based dielectrics using bias thermal stress and thermal stress tests, *Thin Solid Films* **516** (12) (2008) 4111.

- [6] T. Oku, E. Kawakami, M. Uekubo, K. Takahiro, S. Yamaguchi, M. Murakami, Diffusion barrier property of TaN between Si and Cu, *Appl. Surf. Sci.* **99** (4) (1996) 265.

- [7] M.T. Wang, Y.C. Lin, M.C. Chen, Barrier properties of very thin Ta and TaN layers against copper diffusion, *J. Electrochem. Soc.* **145** (7) (1998) 2538.

- [8] Q. Xie, X.-P. Qu, J.-J. Tan, Y.-L. Jiang, M. Zhou, T. Chen, G.-P. Ru, Superior thermal stability of Ta/TaN bilayer structure for copper metallization, *Appl. Surf. Sci.* **253** (3) (2006) 1666.

- [9] V.K. Dixit, K. Neishi, N. Akao, J. Koike, Structural and electronic properties of a Mn oxide diffusion barrier layer formed by chemical vapor deposition, *IEEE Trans. Device Mater. Reliab.* **11** (2) (2011) 295.

- 311 [10] J. Koike, M. Wada, Self-forming diffusion barrier layer in Cu-Mn alloy metallization,

- 312 Appl. Phys. Lett. 87 (2005) 041911.

- [11] H. Shimizu, K. Sakoda, T. Momose, Y. Shimogaki, Atomic layer deposited Co(W) film as a single-layered barrier/liner for next-generation Cu-interconnects, *Jpn. J. Appl. Phys.* 51 (2012) 05EB02.

[12] K. Matsumoto, K. Maekawa, H. Nagai, J. Koike, Deposition behavior and substrate dependency of ALD

- [12] K. Matsumoto, K. Maekawa, H. Nagai, J. Koike, Deposition behavior and substrate dependency of ALD MnOx diffusion barrier layer, 2013 IEEE International Interconnect Technology Conference, 2013, pp. 1-3.

- [13] M.P. Nguyen, Y. Sutou, J. Koike, Diffusion barrier property of MnSixOy layer formed by chemical vapor deposition for Cu advanced interconnect application, *Thin Solid Films* **580** (2015) 56.

- [14] H. Wojcik, C. Krien, U. Merkel, J.W. Bartha, M. Knaut, M. Geidel, B. Adolphi, V. Neumann, C. Wnzel, M. Bendlin, K. Richter, D. Makarov, Characterization of Ru-Mn composites for ULSI interconnects, *Microelectron. Eng.* **112** (2013) 0103.

- [15] M. He, X. Zhang, T. Nogami, X. Lin, J. Kelly, H. Kim, T. Spooner, D. Edelstein, L. Zhao, Mechanism of Co liner as enhancement layer for Cu interconnect gapfill, *J. Electrochem Soc.* **160** (12) (2013) D3040.

- [16] Y.L. Cheng, C.Y. Lee, J.W. Huang, G.S. Chen, J.S. Fang, Comparison of Various Low Dielectric Constant Materials, *Thin Solid Films* **660** (2018) 871.

- [17] J.S. Fang, K.Y. Yu, G.S. Chen, Y.S. Wang, Y.L. Cheng, A 2-nm-Thick Mn Oxide on a Nitrogen-Stuffed Porous Carbon-Doped Organosilica as a Barrier of Cu Films, ECS J. Solid State Sci. Technol. 7(11) (2018) N137.

- [18] F. Braud, J. Torres, J. Palleeau, J. L. Mermet, C. Marcadal, and E. Richard, Microelectron. Eng. 33 (1997) 293.

- [19] V. Selvaraju, A. Brady-Boyd, R. O'Connor, G. Hughes, J. Bogan, Investigation of nitrogen incorporation into manganese based copper diffusion barrier layers for future interconnect applications, *Surf. Interf.* **13** (2018) 133.

- [20] L. Zhao, H. Volders, M. Baklanov, Z. Tokei, M. Pantouvaki, C.J. Wilson, E. V. Besien, G.P. Beyer, C. Claeys, Study of metal barrier deposition-induced damage to porous low-k materials, *Microelectron. Eng.* **88** (2011) 3030.

- [21] S.-M. Chung, J. Koike, Analysis of dielectric constant of a self-forming barrier layer

- with Cu-Mn alloy on TEOS-SiO<sub>2</sub>, J. Vac. Sci. Technol. B 27(5) (2009) L28.

- [22] J. Koike, M. Haneda, J. Iijima, Y. Otsuka, H. Sako, K. Neishi, Growth kinetics and thermal stability of a self-formed barrier layer at Cu-Mn/SiO<sub>2</sub> interface. *J. Appl. Phys.* 102(4), (2007) 043527.

[23] M. Hosseini, J. Koike, Amorphous CoTi<sub>x</sub> as a liner/diffusion barrier material for advanced copper

- [23] M. Hosseini, J. Koike, Amorphous CoTi<sub>x</sub> as a liner/diffusion barrier material for advanced copper metallization, *J. Alloys Compounds* **721** (2017) 134

- [24] M. He, T.-M. Lu, Metal-dielectric interfaces in gigascale electronics, Springer series in materials science, volume 157.

- [25] I. Fisher, M. Eizenberg, Copper ion diffusion in porous and nonporous SiO<sub>2</sub>-based dielectrics using bias thermal stress and thermal stress tests, *Thin Solid Films* **516 (12)** (2008) 4111.

- [26] N. Dalili, Q. Liu, D.G. Ivey, Thermal and electrical stability of TaNx diffusion barriers for Cu metallization, *J. Mater. Sci.* 48 (1) (2013) 489.

- [27] Y.L. Cheng, C.Y. Lee, W.J. Hung, G.S. Chen, J.S. Fang, Electrical and Reliability Characteristics of Dielectric Stack with Low Dielectric Constant SiCOH and Capping SiCNH Films, *Surf. Coatings Technol.* **350** (2018) 57.

- [28] F. Chen, M.A. Shinosky, Electron fluence driven, Cu catalyzed, interface breakdown mechanism for BEOL low-*k* time dependent dielectric breakdown, *Microelectron*. *Reliab*. **54(3)** (2014) 529

- 352 [29] F. Chen, M.A. Shinosky, Addressing Cu/low-k dielectric TDDB-reliability challenges for advanced CMOS technologies, *IEEE Tran. Electron Devices*, **56(1)** (2009) 2

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

340

341

342

343

344

345

346

347

348

349

350

351