1 Article

2

# Novel Dead-time Compensation Strategy for wide

3 current range in a three-phase inverter

4 Jeong-Woo Lim <sup>1</sup>, Hanyoung Bu <sup>1</sup>, Younghoon Cho <sup>1\*</sup>5 <sup>1</sup> Department of Electrical Engineering, Konkuk University, Seoul 05029, Korea; wjddn1@konkuk.ac.kr

6 \* Correspondence: yhcho98@konkuk.ac.kr; Tel.: +82-10-6207-0431

7

8

9 **Abstract:** This paper proposes a novel three - phase voltage source inverter dead-time compensation

10 strategy for accurate compensation in wide current regions of the inverter. In particular, an analysis

11 of the output voltage distortion of the inverter, which appears as parasitic components of the

12 switches, has been conducted for proper voltage compensation in the low current region, and an

13 on-line compensation voltage controller has been proposed. Also, a new trapezoidal compensation

14 voltage implementation method using the current phase is proposed to simplify realizing the

15 trapezoidal shape of the three-phase compensation voltages. Finally, when the proposed dead-time

16 compensation strategy is applied, the maximum phase voltage magnitude in the linear modulation

17 voltage regions is defined to achieve smooth operation even at high modulation index. Simulations

18 and experiments were conducted to verify the performance of the proposed dead-time

19 compensation scheme.20 **Keywords:** DTCS; dead-time compensation; trapezoidal compensation voltage; dead-time effects;

21 three-phase VSI compensation

22

23

## 1. Introduction

24 The dead-time is an efficient strategy which is adding blank time within complementary

25 switching signals to prevent arm-short. The series two switches circuit sharing a DC-link such a half-

26 bridge, is activated complementarily to keep arm-short condition. However, in the actual switch, a

27 delay occurs within on/off operating due to the parasitic components, the series switches appear to

28 be shorted with a DC-link. The short circuit allows excessive current through the series switches,

29 causing serious system failure. Therefore, the reliability of the system can be guaranteed by injecting

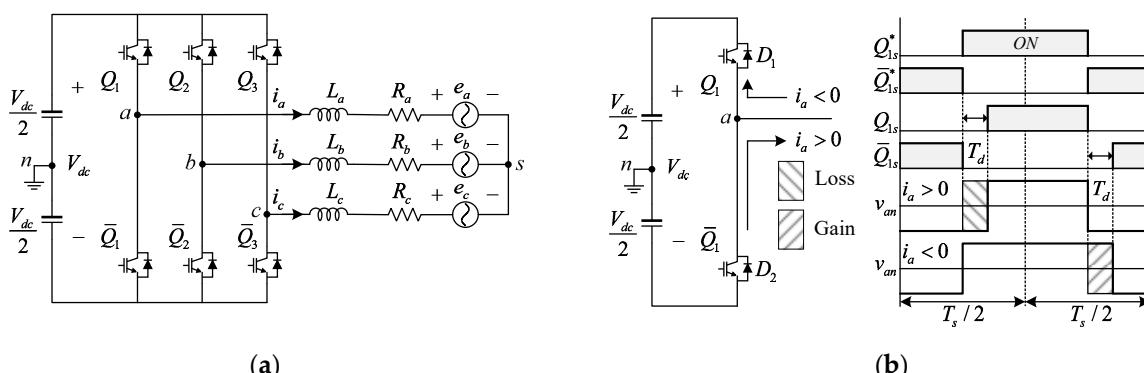

30 enough dead-time  $T_d$  until the switch reaches a steady state [1-2], [5-17].31 **Figure 1.** three-phase VSI and dead-time switching patterns in a-phase: (a) typical three-phase VSI

32 configuration; (b) switching patterns and output voltages of the half-bridge during the dead-time.

33 **Figure 2.** Effects of the dead-time in three-phase VSI ( $f_{sw}=20$ kHz,  $V_{dc}=100$ V,  $L_s=0.01$ mH,  $R_s=10\Omega$ );

34 (a) an a-phase pole voltage reference with SVPWM; (b) comparing dead-time effects with equal

35 voltage reference at Figure 2 (a).

36 Especially, as shown in Figure 1 (a), a circuit structure such as a typical three-phase VSI in which

37 three legs share a DC-link must ensure a reliability of the system by applying dead-time. Figure 1 (b)

38 shows the process of the leg in a-phase according to time during the single switching period.  $Q_{ls}^*, \bar{Q}_{ls}^*$

39 are ideal complementary switches on/off signals and  $Q_{ls}, \bar{Q}_{ls}$  are real switch on/off signals adapted

40 the dead-time  $T_d$ . Since the dead-time can't control actively, it causes not only serious voltage

41 distortions in inverter output voltage as shown Figure 1 (b) but also adverse effects on the all

42 algorithms using a voltage reference, thereby generating an error voltage between the real inverter

43 output voltage and the voltage reference [3-4]. The Figure 2 (a) demonstrates a pole voltage reference

44 and (b) illustrates current waveforms with Figure 2 (a) to confirm the current distortions by dead-

45 time. Here, when the dead-time is applied, it can be recognized that the critical current distortion

46 occurs near the zero crossing points and peak area.

47 Various types of dead-time compensation strategies have been published to analyze and

48 compensate for the dead-time defects. In [1-2], [5], the dead-time and the switch on/off delay are

49 analyzed and suggest dead-time compensation method via theoretical parameters. However, since the

50 switch parameters are fluctuated with external factors, it is difficult to compensate accurately in all

51 inverter operating areas by using fixed variables. In some papers [6-8], the distortions of inverter

52 output voltage by switch's output capacitors studied and suggested compensation strategies with the

53 look-up table containing the switch-off times according to the magnitude of the current. Although, it

54 has a disadvantage that is difficult to compensate the precise dead-time in various environments

55 since the table is limited to the experimental environment. The papers [9-10] proposed on-line dead-

56 time compensation voltage (DTCV) modification methods that feeds back current distortions.

57 However, the strategies extracting of the current errors are complicate and it has the drawbacks near

58 the zero-crossing points. In [11], the dead-time compensation algorithm using filter has been

59 suggested. Nevertheless, due to the lowpass-filter characteristics, the bandwidth of the current

60 controller can be limited. The paper [12], it submits scheme which is compensates the sixth-order

61 harmonic in d-q axis currents on the synchronous reference frame using bandpass filter. But, the

62 performance of the dead-time compensation scheme is limited by the current controller performance

63 because of the distortion errors input to the current reference. The [13-14] offer compensation

64 strategies using observer which is feeding back d-q axis currents on synchronous reference frame.

65 However, the observer regards not only the dead-time distortions but also various parasitic

66 components as dead-time errors, since it is utilizing an ideal-model. Thus, it is impossible to

67 accurately estimate the real output voltage of inverter. In [15-16], the on-line dead-time compensation

68 algorithms having the trapezoidal shape compensation voltage and the modulator for slope have

69 been proposed. However, it is difficult to completely compensate for the non-linearities of the switch

70 especially low current region.

71 In this paper, a novel DTCS is proposed for correct dead-time compensation and for normal

72 operating in wide-current region. In section 2, the inverter output voltage error is analyzed by the

73 dead-time and the switch's non-linearities. In section 3, it presents the proposed novel DTCV

74 implementation strategy to revise the shape of the TCV and the on-line TCV controller. In section 4,

75 the three-phase VSI distorted output voltage due to the dead-time is analyzed on the space vector

76 and the maximum linear-modulation phase voltage (MMPV) is also done when the proposed DTCS

77 is applied. Finally, in section 5, the simulation and the experiment are implemented to verify the

78 proposed DTCS. And the performance of the DTCS is evaluated with phase current total harmonic

79 distortion (THD).

80 **2. Analysis of dead-time effects**

81 In this paper, the dead-time  $T_d$  of (2) is including the ON/OFF propagation delay in order to

82 simply express as  $V_d$ . And the conduction voltage drops across the diode and switch are excluded

83 from the effect of dead-time because they are negligible compared to the dc-link voltage level.

84 *2.1. The three-phase VSI output voltage errors by the dead-time*

85 In figure 1 (b), the inverter output voltage  $v_{an}$  is varied according to the phase current  $i_a$

86 direction during the dead-time. When the current direction is in the positive, the current flows

87 through the body diode  $D_2$  in the lower switch  $\bar{Q}_1$ , so that the  $v_{an}$  come to be  $-V_{dc}/2$ . On the

88 other hand, when the current direction is in the negative direction, the current flows though the body

89 diode  $D_1$  in the upper switch  $Q_1$ , thus the output  $v_{an}$  becomes  $V_{dc}/2$ . Therefore, the a-phase pole

90 voltage errors due to the dead-time can be expressed as

$$\Delta v_{an}^{err} = \begin{cases} -V_d & (i_a > 0) \\ V_d & (i_a < 0) \end{cases} \quad (1)$$

$$V_d = \frac{T_{on} + T_d - T_{off}}{T_s} V_{dc} \quad (2)$$

91 In equation (2), the  $V_d$  is average pole voltage error (APVE) that occurs during single switching

92 period, and it contains switch turn on/off delays  $T_{on}, T_{off}$  as well as dead-time  $T_d$  [2]. The a-phase

93 APVE can be expressed according to the direction of current as shown equation (1), also the other

94 phases b, c can be expressed in the same approach via each current polarity [1]. The APVEs of three-

95 phase are represented by the voltage errors on the synchronous reference frame d-q axis as follows.

$$\begin{bmatrix} \Delta v_{as}^{err} \\ \Delta v_{bs}^{err} \\ \Delta v_{cs}^{err} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} \Delta v_{an}^{err} \\ \Delta v_{bn}^{err} \\ \Delta v_{cn}^{err} \end{bmatrix} \quad (3)$$

$$\begin{bmatrix} \Delta v_d^{err} \\ \Delta v_q^{err} \end{bmatrix} = \begin{bmatrix} \cos \theta_e & \sin \theta_e \\ -\sin \theta_e & \cos \theta_e \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 \\ 0 & \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} \Delta v_{as}^{err} \\ \Delta v_{bs}^{err} \\ \Delta v_{cs}^{err} \end{bmatrix} \\ = -\frac{4V_d}{\pi} \begin{bmatrix} -\sin \delta - \sum_{n=1}^{\infty} \left\{ \frac{\sin(6n\omega_e t - \delta)}{(6n-1)} + \frac{\sin(6n\omega_e t + \delta)}{(6n+1)} \right\} \\ \cos \delta - \sum_{n=1}^{\infty} \left\{ \frac{\cos(6n\omega_e t - \delta)}{(6n-1)} - \frac{\cos(6n\omega_e t + \delta)}{(6n+1)} \right\} \end{bmatrix} \quad (4)$$

96 The equation (3) indicates average phase voltage errors by transferring the three-phase APVEs

97 and equation (4) denotes the average d-q axis voltage errors on synchronous reference frame by the

98 Fourier series expansion [5] [11]. Where the  $\delta$  is the phase angle between the q-axis and the three-

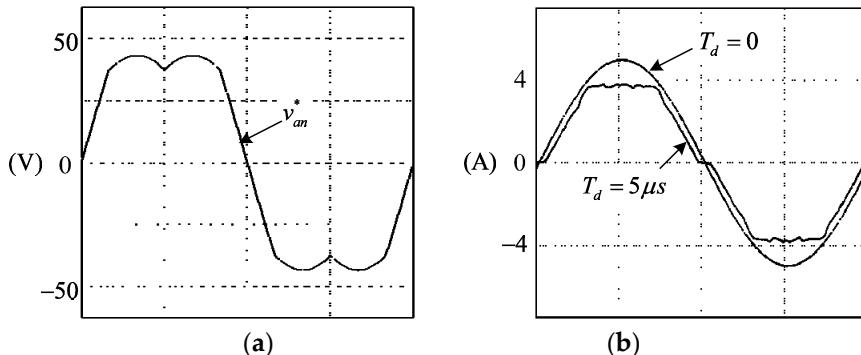

99 phase current vector  $I_s$  as shown Figure 3.

100

101 **Figure 3.** Stationary reference frame  $\alpha - \beta$  axis and synchronous reference frame  $d - q$  axis with  $\delta$ .

102 The d-q axis voltage error contains both the fundamental and  $6n^{\text{th}}$  harmonics distortion as

103 equation (4). Theses voltage errors cause discordance between the real output voltage of three-phase

104 VSI and the voltage references. Furthermore, the distortion components causing harmonic currents

105 which degrades the performance of the VSI. Therefore, in order to compensate the voltage distortions

106 due to the dead-time, the opposite voltage of the error voltage can be applied through the equation

107 (1). The average compensation pole voltage (ACPV) can be expressed as follows.

$$\Delta v_{an} = V_d \text{sign}(i_a) \quad (5)$$

$$\text{sign}(i_a) = \begin{cases} 1 & (i_a > 0) \\ -1 & (i_a < 0) \end{cases} \quad (6)$$

108 The ACPVs of b, c -phases can be describe in similar way as equations (5), (6) which is a-phase

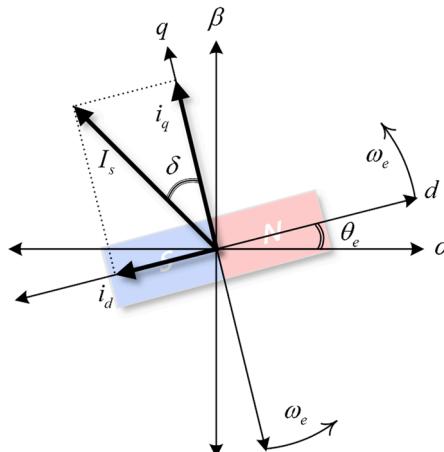

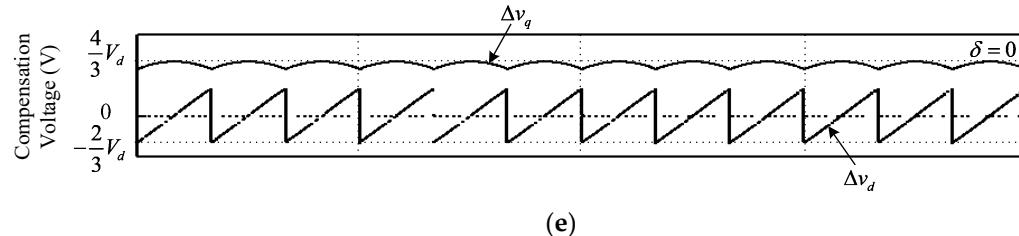

109 AVPC [1-2]. Using the ACPVs of three-phase with synchronous reference frame transformer in

110 equation (5), (6), the d-q axis compensation voltage waveforms can be illustrated as Figure 4.

111 **Figure 4.** Dead-time compensation voltage waveforms; (a) a-phase current;

112 (b) ACPV of a-phase; (c) the average compensation phase voltage of a-phase;

113 (d) compensation voltages on stationary reference frame  $\alpha - \beta$  axis; (e) compensation voltages on synchronous reference frame  $d - q$  axis;

114 **2.2. The effects of switch's parasitic components**

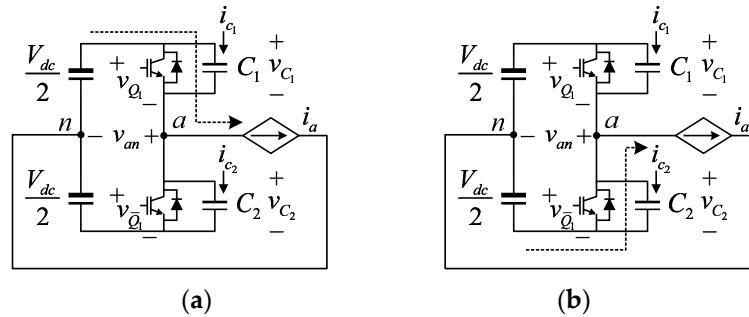

115 The switch contains diverse parasitic components and the output capacitor of the switch is

116 critical factor in compensating the distorted output voltage of three-phase VSI because of it seriously

117 affects the switch off delay time  $T_{off}$  depending on the magnitude of the phase current [6]. Figure 5

118 shows the output capacitors  $C_1, C_2$  connected in parallel with the switches and the charging and

119 discharging process when the phase current  $i_a$  flows in the positive direction.

120 **Figure 5.** Charging and discharging process of the output capacitors ( $i_a > 0$ ).

121 In Figure 5 (a), the voltage ( $v_{C_1} = V_{dc}$ ) charged in capacitor  $C_1$  is discharged while the upper

122 switch is turn on. At the moment, the discharging current  $-i_{C_1}$  flows to the node 'a' due to the

123 potential difference and charges the capacitor  $C_2$  of the lower switch. Since the impedance between

124 the capacitor  $C_1$  and  $C_2$  is very small than the load, most of the current  $-i_{C_1}$  flows to the capacitor

125  $C_2$ , so that the voltage  $v_{C_2}$  of the lower switch parasitic capacitor  $C_2$  is rapidly charged to  $V_{dc}$ .

126 Consequently, when the upper switch is turned on, the output pole voltage  $v_{an}$  of the inverter is

127 hardly affected. On the contrary, when the both upper and lower switches are turned off as shown

128 in Figure 5 (b), the capacitor  $C_2$  of the lower switch is discharged and the voltage of  $v_{C_2}$  arrives at

129 zero. At this time, the phase current  $i_a$  can be expressed by the sum of the charge current  $i_{C_1}$  of the

130 upper switch and the discharge current  $i_{C_2}$  of the lower switch.

$$i_a = -i_{C_2} + i_{C_1} \quad (7)$$

131 Assuming that the capacitances  $C_1, C_2$  and the charging/discharging potentials are equal, the

132 time  $T_{off}$  required for discharging  $v_{C_2}$  can be formulated as follows.

$$C_1 = C_2 = C_{12} \quad (8)$$

$$|i_{C_2}| = |i_{C_1}| = \frac{|i_a|}{2} \quad (9)$$

$$v_{C_2}(T_{off}) = \frac{1}{C_{12}} \int_0^{T_{off}} -i_{C_2}(t) dt + v_{C_2}(0) \quad (10)$$

133 From the equation (11), if the initial value is  $V_{dc}$ , the following equations (11), (12) can be

134 obtained.

$$-V_{dc} = \frac{1}{C_{12}} \int_0^{T_{off}} -\frac{|i_a|}{2} dt \quad (11)$$

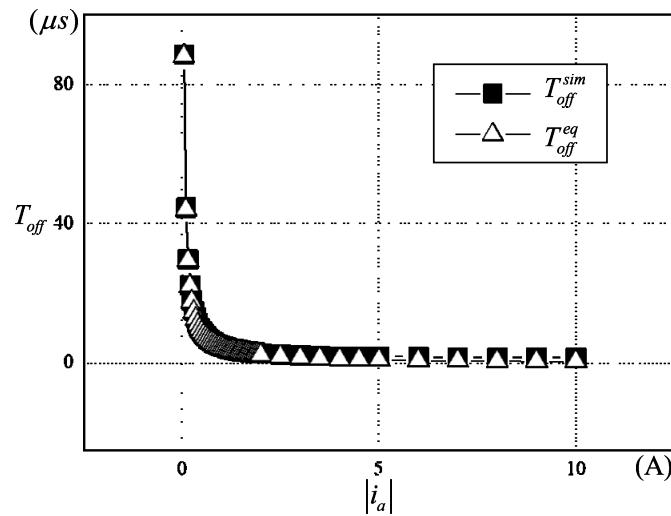

$$\therefore T_{off} = \frac{2C_{12}V_{dc}}{|i_a|} \quad (12)$$

135 If the phase current  $i_a$  flows in the opposite direction, the switch delay occurs in the upper

136 switch in a similar way when the current flowing in the positive direction as shown Figure 5. Thus,

137 the upper switch turns off delay time is the same as in equation (12) [17]. The Figure 6 shows a graph

138 comparing the time  $T_{off}^{eq}$  calculated by equation (12) and the time  $T_{off}^{sim}$  measured by simulation

139 result in Figure 5. It can be confirmed that the switch turns off delay time changes non-linearly along

140 with the magnitude of the phase current. Therefore, to accurately compensate the distorted three-

141 phase VSI output voltage, it is necessary to compensate for the appropriate switch delay according

142 to the current magnitude because the influence of  $T_{off}$  is remarkable in the low current region.

143

144 **Figure 6.** Comparing with  $T_{off}^{eq}$  and  $T_{off}^{sim}$ .

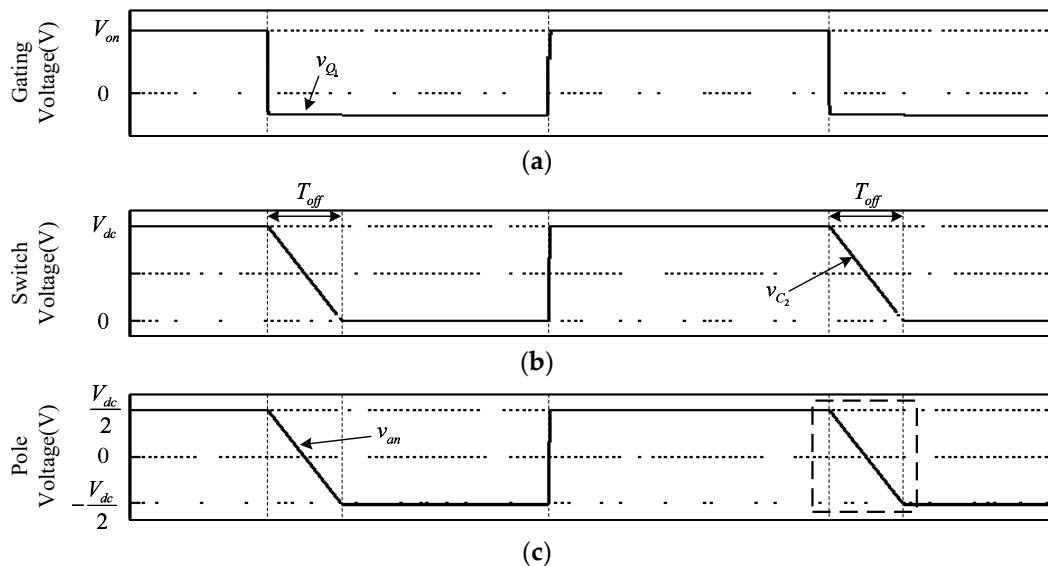

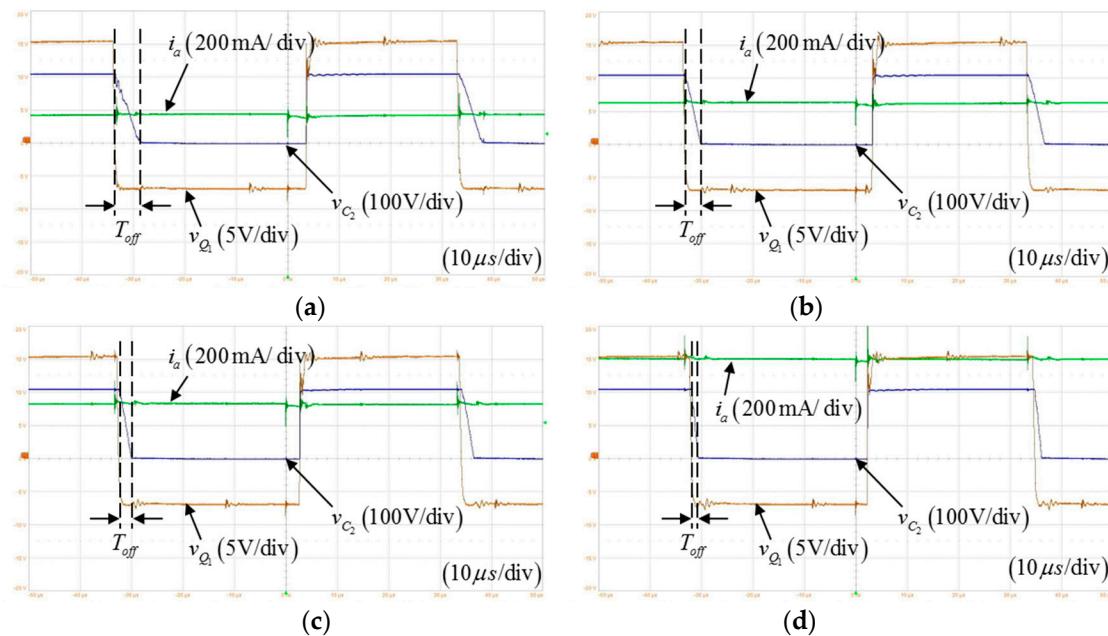

145 The Figure 7 shows the simulation results of the circuit Figure 5. the symbols  $v_{Q_1}$ ,  $v_{C_2}$  are

146 meaning the gate voltage of the upper switch, the voltage of the lower switch respectively and the

147  $v_{an}$  is output pole voltage. When the phase current  $i_a$  is positive direction, the output pole voltage

148 of the VSI represented as

$$v_{an} = -\frac{V_{dc}}{2} + v_{C_2} \quad (13)$$

149 In here, the  $v_{C_2}$  affects the output of the VSI since it is discharged with a slope depending on

150 the amplitude of  $|i_a|$  as shown in Figure 7. Therefore, the  $v_{C_2}$  should be properly compensated

151 because of it can't be actively controlled.

Figure 7. Simulation results of Figure 5 ( $T_{off} < T_d$ ) ; (a) gate voltage  $v_{Q_1}$ ; (b) capacitor voltage  $v_{C_2}$  of the lower switch; (c) inverter pole voltage  $v_{an}$ .

The Figure 8 shows the waveforms of real switch and the phase currents to compare with Figure 7 which is simulation results.

Figure 8. Variation of the  $T_{off}$  according to the phase current magnitude; (a)  $i_a = 170\text{mA}$ ; (b)  $i_a = 250\text{mA}$ ; (c)  $i_a = 330\text{mA}$ ; (d)  $i_a = 600\text{mA}$ .

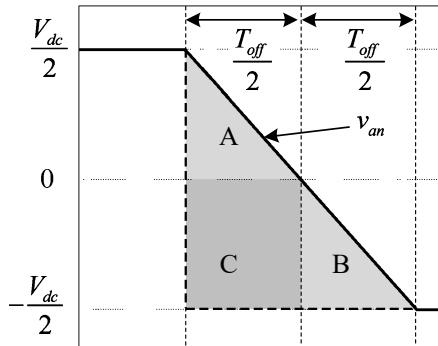

The equation (2) is applicable when the current level is enough to saturate the  $T_{off}$  and the voltage of the capacitor is rapidly falling or rising. Therefore, the output pole voltage changes the polarity with substantially constant slope as Figure 9, since the low current region where the effects of the turn off delay is maximized as Figure 7, 8. Consequently, it is necessary to redefine the compensation voltage considering the slop of the output capacitor voltage.

163

164

**Figure 9.** Detail of the dashed box in Figure 5 (c).

165 The regions A, B and C are non-controllable voltages caused by the output capacitors in Figure

166 9 and it requires appropriate voltage compensation for the ideal inverter output. The voltage region

167  $\Delta v_{C_2}$  made by the output capacitor can be described as

$$\Delta v_{C_2} = A - (B + C) \quad (14)$$

168 If each area is defined as equation (15), (16) and (17), the parasitic voltage region  $\Delta v_{C_2}$

169 represented as equation (18)

$$A = \frac{1}{2} \left( \frac{V_{dc}}{2} \frac{T_{off}}{2T_s} \right) \quad (15)$$

$$B = \frac{1}{2} \left( -\frac{V_{dc}}{2} \frac{T_{off}}{2T_s} \right) \quad (16)$$

$$C = -\frac{V_{dc}}{2} \frac{T_{off}}{2T_s} \quad (17)$$

$$\Delta v_{C_2} = \frac{T_{off}}{2T_s} V_{dc} \quad (18)$$

170 Equation (2) can be redefined as equation (19), in order to properly compensate the output

171 capacitor in the low current region in which the switch turns off delay has the greatest effect on the

172 three-phase VSI.

$$\therefore V_d = \frac{T_{on} + T_d - \frac{T_{off}}{2}}{T_s} V_{dc} \quad (19)$$

### 173 3. The proposed DTCS

174 As mentioned above, the voltage error not only caused by dead-time distortion but also caused

175 by switch parasitic are should be compensated to obtain the ideal three-phase VSI output. In the

176 equation (19), the generally dead-time  $T_d$  is fixed value, but the delay time  $T_{off}$  is not. Hence, the

177 precise  $T_{off}$  has to be calculated according to the phase current levels in real-time for correct

178 compensation. In this paper, the TCV is used to simplify the variation of  $T_{off}$  [8], [15]. In addition,

179 the novel implementation strategy is proposed to simplify the realizing trapezoidal shape voltage,

180 also the novel on-line TCV controller is proposed to robust for variating parameters.

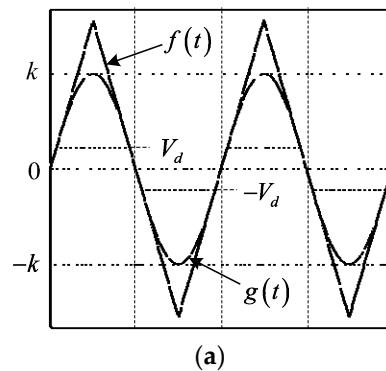

## 181 3.1. The implementaion of the TCV based on the current position

182 The proposed DTCS uses synchronous reference frame transformation matrix and limiter

183 function to simplify realizing the TCV. Figure 10 shows the triangle waveform function  $f(t)$ , the

184 sinusoidal waveform function  $g(t)$  with peak value  $k$  and the trapezoidal waveforms utilizing

185 them to comparing the outline. In Figure 3, the position of the three-phase current  $\theta_d$  can be

186 calculated as follows using the d-q axis currents.

$$\delta = \tan^{-1} \left( \frac{i_d}{i_q} \right) \quad (20)$$

$$\theta_d = (\theta_e - \delta) \quad (21)$$

187 The three-phase sinusoidal waveforms, which is in phase with the three-phase current vector

188  $I_s$ , can be defined as follows.  $\alpha-\beta$  axis voltage  $g(\Delta v_\alpha), g(\Delta v_\beta)$  with peak value  $k$  on the

189 stationary reference frame expressed as

$$\begin{aligned} g(\Delta v_\alpha) &= -k \sin \theta_d \\ g(\Delta v_\beta) &= k \cos \theta_d \end{aligned} \quad (22)$$

190  $g(\Delta v_\alpha), g(\Delta v_\beta)$  is transferred to a three-phase stationary coordinate and the amplitude is

191 limited to  $\pm V_d$  as equation (23) to generate the TCV as shown in Figure 10 (b).

$$\begin{cases} g(\Delta v_{an}) = g(\Delta v_\alpha) & (-V_d \leq g(\Delta v_{an}) \leq V_d) \\ g(\Delta v_{bn}) = -\frac{(g(\Delta v_\alpha) - \sqrt{3}g(\Delta v_\beta))}{2} & (-V_d \leq g(\Delta v_{bn}) \leq V_d) \\ g(\Delta v_{cn}) = -\frac{(g(\Delta v_\alpha) + \sqrt{3}g(\Delta v_\beta))}{2} & (-V_d \leq g(\Delta v_{cn}) \leq V_d) \end{cases} \quad (23)$$

(a)

(b)

192 **Figure 10.** Proposed implementation strategy for TCV; (a) triangle waveform function  $f(t)$  and

193 sinusoidal waveform function  $g(t)$  with peak  $k$  ; (b) TCV comparison made by  $f(t)$  with

194  $g(t)$ .

195 As can be seen in the Figure 10 (b), if the peak level  $k$  is large enough to approximate a linear

196 slope between  $V_d$  and  $-V_d$ , then the waveforms can be reckoned as  $f(\Delta v_{an}) \approx g(\Delta v_{an})$ . Next, as

197 illustrated in Figure 11, the peak value  $k$  for implementing the TCV having slopes of the width  $\phi$

198 can be defined as follows.

199

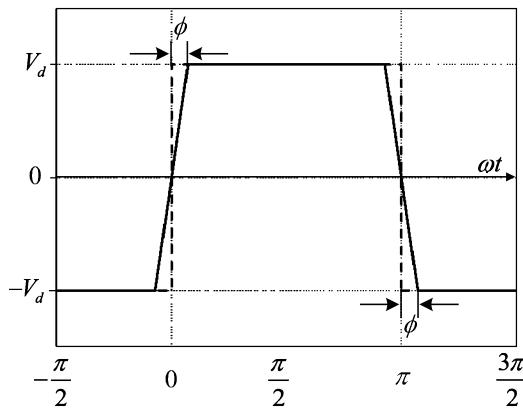

200 **Figure 11.** TCV with slopes of the width  $\phi$ .

201 The function  $g(t)$  can be express as  $g(t) = k \sin(\omega t)$ , and the time when  $g(t)$  has a slopes of

202 the width  $\phi$  defines as  $t_\phi$ , then the time  $t_\phi$  can be derived as

$$t_\phi = \frac{\phi}{\omega} \quad (24)$$

203 Assuming that the output of  $g(t)$  is  $|V_d|$  at the time  $t_\phi$ , the  $g(t)$  rewritten as

$$k \sin(\omega t_\phi) = |V_d| \quad (25)$$

204 Therefore, the peak value  $k$  of the function  $g(t)$  obtaining slope of the width  $\phi$  is defined

205 as equation (26)

$$\therefore k = \frac{|V_d|}{\sin(\phi)} \quad (26)$$

206 The adjustable TCV having a desired compensation voltage amplitude  $|V_d|$  and compensation

207 voltage slope of width  $\phi$  can be realized with equations (23) to (26).

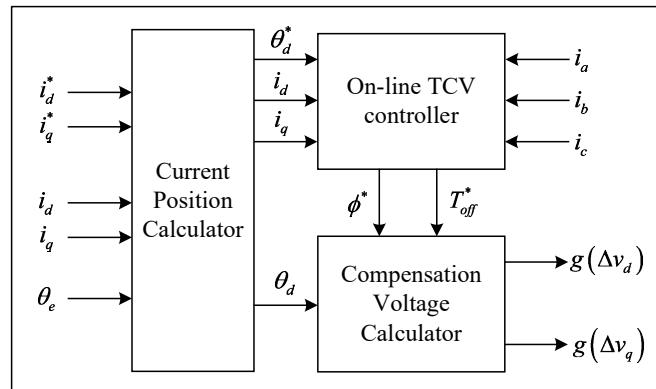

### 208 3.2. The on-line TCV controller

209 It can be seen from Figure 6 and equation (19) that the proportions of APVE must be varied

210 according to the amount of the current flowing in the phase. Especially, when the VSI operates in the

211 low current region, the magnitude of the APVE and the slopes of the TCV are decreased. For this

212 reason, for smooth dead-time compensation in wide current regions, both the scale of the APVE and

213 the slope of the TCV must be modulated to optimum value corresponding to the inverter operating

214 environment.

215 Using the previously defined equations (12), (19) and (26), it is possible to vary the amplitude of

216 APVE by responding to  $T_{off}$ . However, there is limitations to actively react changing conditions.

217 Therefore, a controller using the errors of the TCV is proposed to implement robust dead-time

218 compensation even unknown operating conditions.

219 While the influence of the dead-time appears  $6n^{\text{th}}$  harmonics in the synchronous reference

220 frame as equation (4), the TCV errors can be generated using them [16]. The extracting axis can be

221 selected as a d-axis although the  $6n^{\text{th}}$  harmonics appear on both d-q axis, since the d-axis has larger

222 voltage error than q-axis has. But if there is a d-axis current ( $\delta \neq 0$ ), the fundamental component of

223 the distortion voltage is shared with q-axis shown in equation (4). Thus, to obtain a constant value

224 regardless of amount of d-axis current, the synchronous reference frame based the three-phase

225 current vector  $I_s$  should be carried out. In this, if the d-axis current for TCV error attained from the

226 equation (20), (21), the harmonics do not emerge on d-axis since the harmonic components of the

227 current affects the phase  $\delta$ . For this reason, the ideal phase of three-phase current vector  $I_s$  can be

228 gotten by the d-q axis current references  $i_d^*, i_q^*$  as following equation (27), (28), assuming that the

229 actual currents do not deviate for the current commands.

$$\delta^* = \tan^{-1} \left( \frac{i_d^*}{i_q^*} \right) \quad (27)$$

$$\theta_d^* = (\theta_e - \delta^*) \quad (28)$$

230 The controller error  $i_{dd}$  is calculated from the d-q axis transfer matrix in equation (4) and the

231 phase of ideal three-phase current vector  $I_s$  (28).

232

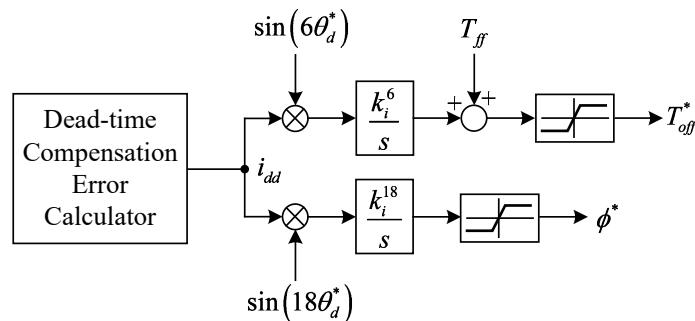

233 **Figure 12.** The proposed on-line TCV controller.

234 The d-axis current  $i_{dd}$  based on  $\theta_d^*$  includes the current distortion of the  $6n^{\text{th}}$  harmonics as per

235 influence of the TCV errors, and the polarity of them can be determined by multiplying each order

236 harmonic via  $\theta_d^*$  [16]. Figure 12 demonstrates the proposed on-line TCV controller. To adjust the

237 turn off delay time and slope of the TCV, the integrators are designed and for faster dynamics,  $T_{ff}$

238 from the equation (12) is feedforwarded. While the  $T_{off}^*$  is a factor controlling the maximum APVE,

239 the phase current  $i_s$  in equation (12) must be altered as the three-phsae currents amplitude  $I_s$ .

240      **Figure 13.** Analysis of DTCV error characteristics on the synchronous reference frame; (a) error

241      voltage of  $V_d$ ; (b) FFT result of Figure 13 (a); (c) error voltage of slop of DTCV; (d) FFT result of Figure

242      13 (c).

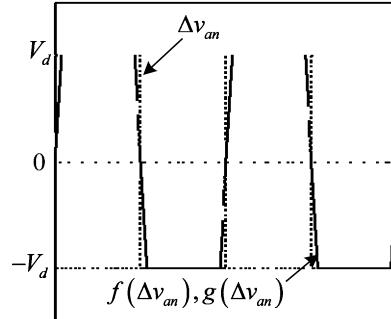

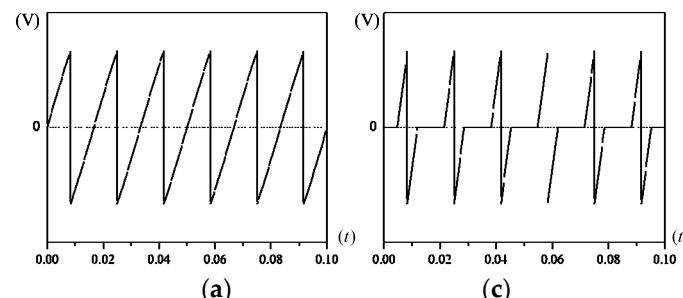

243      Figure 13 indicates the fast fourier transform (FFT) results for two types of the DTCV errors.

244      Figure 13 (a) shows the voltage waveform of the  $V_d$  error. And the FFT result of the  $V_d$  error has

245      prominent component in the 6<sup>th</sup> harmonic as Figure 13 (b). Figure 13 (c) demonstrates the voltage

246      waveform of the slope error. And the FFT result of the slope error has noticeable element in the 12<sup>th</sup>

247      and 18<sup>th</sup> harmonics as Figure 13 (d).

248      By utilizing the results of the Figure 13, the 6<sup>th</sup> harmonic and 18<sup>th</sup> harmonic can be selected as

249      error factors of the  $T_{off}$  and the  $\phi$  respectively such as Figure 12. The 18<sup>th</sup> harmonic is picked as a

250      slope error to minimize the influence of the 6<sup>th</sup> harmonic instead of the 12<sup>th</sup>.

#### 251      4. The analysis of the linear modulation region with proposed DTCS

252      The proposed DTCS the way feedforwarding the DTCV at the controller output which voltage

253      references. Thus, when the correct DTCV is applied, the dead-time effect does not come out at the

254      controller sides. However, if the controller outputs a voltage command exceeding the inverter output

255      limitation, the feedforwarding compensation voltage will not be able to suitable compensate due to

256      physical constraints of the hardware. Therefore, it is required to limit the voltage reference of the

257      controller by applying the proper physical voltage limit to the controller in order to perform normal

258      operating of the DTCS.

#### 259      4.1. The definition of the MMPV of the three-phase VSI

260      **Table 1.** The phase voltages and space voltage vectors of the three-phase VSI.

| Vector  | Phase voltage        |                      |                      | Space voltage vector            |

|---------|----------------------|----------------------|----------------------|---------------------------------|

|         | $v_{as}$             | $v_{bs}$             | $v_{cs}$             |                                 |

| $V_1^i$ | $\frac{2}{3}V_{dc}$  | $-\frac{1}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc} / 0^\circ$   |

| $V_2^i$ | $\frac{1}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$  | $-\frac{2}{3}V_{dc}$ | $\frac{2}{3}V_{dc} / 60^\circ$  |

| $V_3^i$ | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc}$  | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc} / 120^\circ$ |

| $V_4^i$ | $-\frac{2}{3}V_{dc}$ | $\frac{1}{3}V_{dc}$  | $\frac{1}{3}V_{dc}$  | $\frac{2}{3}V_{dc} / 180^\circ$ |

| $V_5^i$ | $-\frac{1}{3}V_{dc}$ | $-\frac{1}{3}V_{dc}$ | $\frac{2}{3}V_{dc}$  | $\frac{2}{3}V_{dc} / 240^\circ$ |

| $V_6^i$ | $\frac{1}{3}V_{dc}$  | $-\frac{2}{3}V_{dc}$ | $\frac{1}{3}V_{dc}$  | $\frac{2}{3}V_{dc} / 300^\circ$ |

261

0 0 0 0 / 0°

262

263

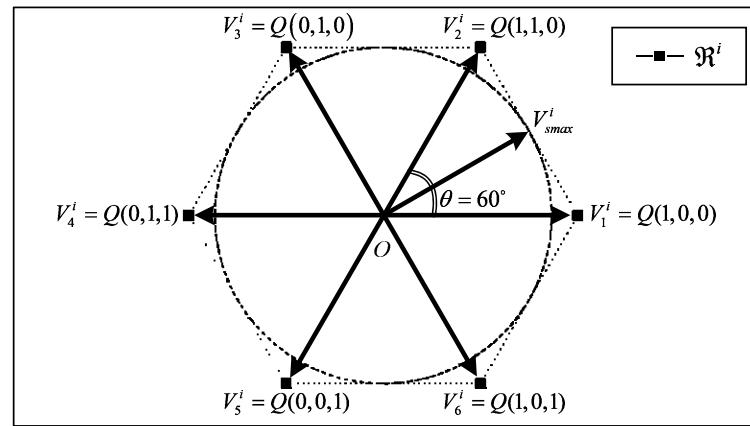

**Figure 14.** Six output voltage vectors of typical three-phase VSI.

264 Table 1 and Figure 14 are express the voltage vectors of the three-phase VSI in Figure 1. The

265 hexagonal region  $\mathfrak{R}^i$  using the six active voltage vectors is ideal voltage area. The switching

266 operation state function  $Q(Q_n, Q_n, Q_n)$  of each leg in Figure 14 is shown as

$$Q(Q_1, Q_2, Q_3) \begin{cases} Q_n = 1: & Q_n = on, \bar{Q}_n = off \\ Q_n = 0: & \bar{Q}_n = on, Q_n = off \end{cases} \quad (29)$$

267 In Figure 14,  $V_{smax}^i$  is the magnitude of the MMPV in the region  $\mathfrak{R}^i$ . When arbitrary voltage

268 reference  $V^*$  presents at  $0^\circ \leq \theta \leq 60^\circ$ , it can be configured during the switching period  $T_s$  with the

269 neighboring active voltage vector  $V_1^i, V_2^i$  and zero voltage vector  $O$ .

$$\int_0^{T_s} V^* dt = \int_0^{T_1} V_1^i dt + \int_{T_1}^{T_1+T_2} V_2^i dt + \int_{T_1+T_2}^{T_s} O dt \quad (30)$$

270 Where  $T_1, T_2$  represent the interval for which the vectors  $V_1^i, V_2^i$  is applied, respectively. The

271 maximum active voltage vector with  $V_1^i, V_2^i$  is

$$V^* T_s = V_1^i T_1 + V_2^i T_2 \quad (31)$$

272 The reference vector  $V^*$  projected on the  $V_1^i$  and  $V_2^i$  vectors, respectively, can be given as

$$V_1^i T_1 = V^* T_s \cos \theta - V_2^i T_2 \cos 60^\circ \quad (32)$$

$$V_2^i T_2 = V^* T_s \frac{\sin \theta}{\cos 30^\circ} \quad (33)$$

273 The periods of each voltage vector  $T_1, T_2$  can be obtained with equation (32), (33)

$$T_1 = \gamma T_s \cos \theta - \frac{\gamma T_s}{\sqrt{3}} \sin \theta \quad \left( \text{where } \gamma = \frac{3}{2} \frac{V^*}{V_{dc}} \right) \quad (34)$$

$$T_2 = \frac{2\gamma T_s}{\sqrt{3}} \sin \theta \quad (35)$$

274 Here, since  $T_1 + T_2 \leq T_s$ , equations (34), (35) can be derived as equation (36)

$$V^* \left( \cos \theta + \frac{1}{\sqrt{3}} \sin \theta \right) \leq \frac{2}{3} V_{dc} \quad (36)$$

$$V^* \leq \frac{V_{dc}}{\sqrt{3}} \frac{1}{\sin(\theta + 60^\circ)} \quad (37)$$

$$\therefore V_{smax}^i = \frac{V_{dc}}{\sqrt{3}} \quad (\text{where } \theta = 30^\circ) \quad (38)$$

275 Accordingly, the MMPV amplitude  $V_{smax}^i$  at  $\theta = 30^\circ$  in the ideal three-phase VSI can be defined

276 as equation (38)

277 *4.2. The analysis of the linear modulation region with dead-time and proposed DTCS*

278 The distortion voltage that occurs in dead-time can be derived by using equations (3) to (6) and

279 be demonstrated distorted voltage region with Figure 14. In this case, the affection of the distorted

280 voltage caused by the dead-time depends on the phase  $\psi$  of the current. Thus, the distortion voltage

281 can be defined as the function of  $\psi$  as  $\Delta v_\alpha^{err}(\psi), \Delta v_\beta^{err}(\psi)$  on the stationary reference frame  $\alpha-\beta$

282 axis. Where the maximum three-phase VSI output with six active voltage vectors is  $v_\alpha^i, v_\beta^i$ , the

283 distorted three-phase VSI output, the  $v_\alpha^r, v_\beta^r$  can be express as

$$\begin{bmatrix} v_\alpha^r \\ v_\beta^r \end{bmatrix} = \begin{bmatrix} v_\alpha^i \\ v_\beta^i \end{bmatrix} + \begin{bmatrix} \Delta v_\alpha^{err}(\psi) \\ \Delta v_\beta^{err}(\psi) \end{bmatrix} \quad (39)$$

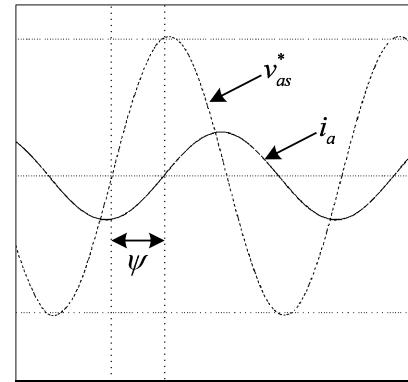

284 The Figure 15 defines the phase  $\psi$  between the voltage reference and phase current.

285

286 **Figure 15.** The current phase  $\psi$  with a-phase voltage reference  $v_{as}^*$  and a-phase current  $i_a$ .

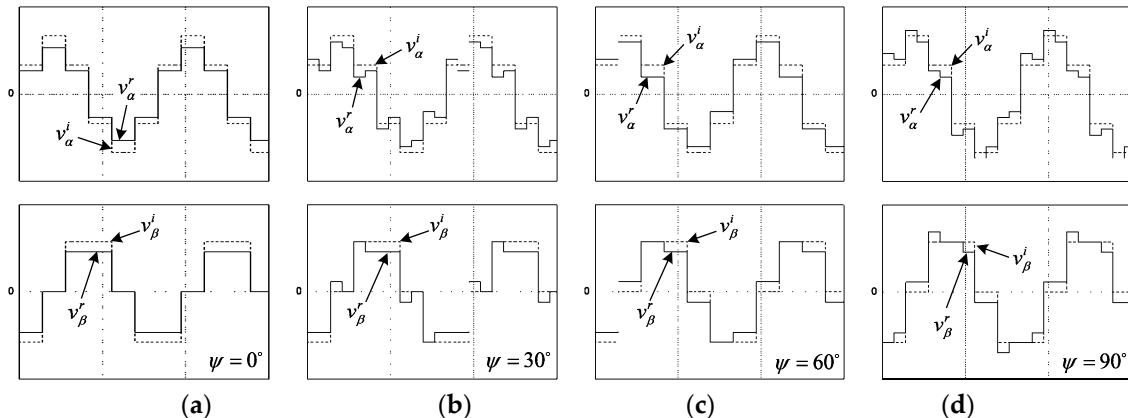

287 Figure 16 illustrates the distorted three-phase VSI output voltage waveforms  $v_\alpha^r, v_\beta^r$  on the

288 stationary reference frame  $\alpha-\beta$  axis according to the phase  $\psi$ . Figure 17 shows  $v_\alpha^r, v_\beta^r$  regions on

289 the x-y plot using the waveforms in Figure 16 and equation (39), and the right side of each voltage

290 region reveals the sector ① in detail for more accurate analysis.

**Figure 16.** Voltage waveforms  $v_{\alpha}^i, v_{\alpha}^r$  and  $v_{\beta}^i, v_{\beta}^r$  on the stationary reference frame according to the phase  $\psi$ ; (a)  $\psi = 0^\circ$ ; (b)  $\psi = 30^\circ$ ; (c)  $\psi = 60^\circ$ ; (d)  $\psi = 90^\circ$ .

291

292

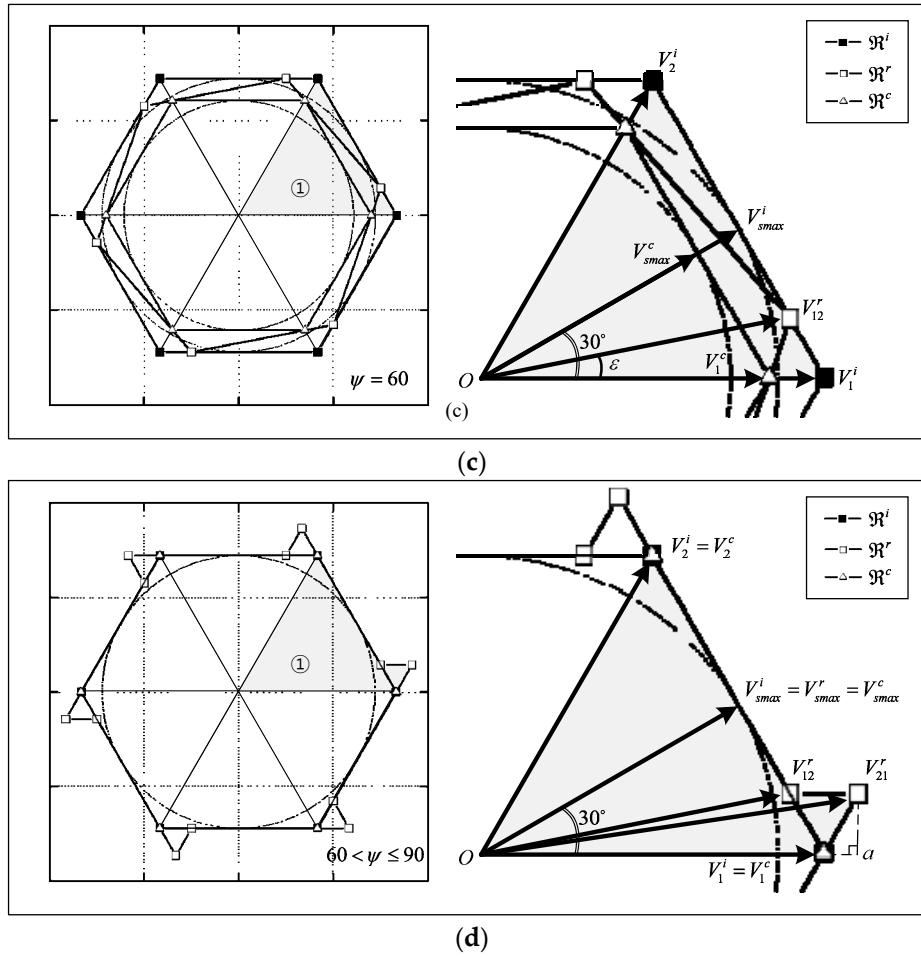

293 **Figure 17.** Distorted voltage regions according to the current phase  $\psi$ ; (a)  $\psi = 0^\circ$ ; (b)

294  $0^\circ < \psi < 60^\circ$ ; (c)  $\psi = 60^\circ$ ; (d)  $60^\circ < \psi \leq 90^\circ$ .

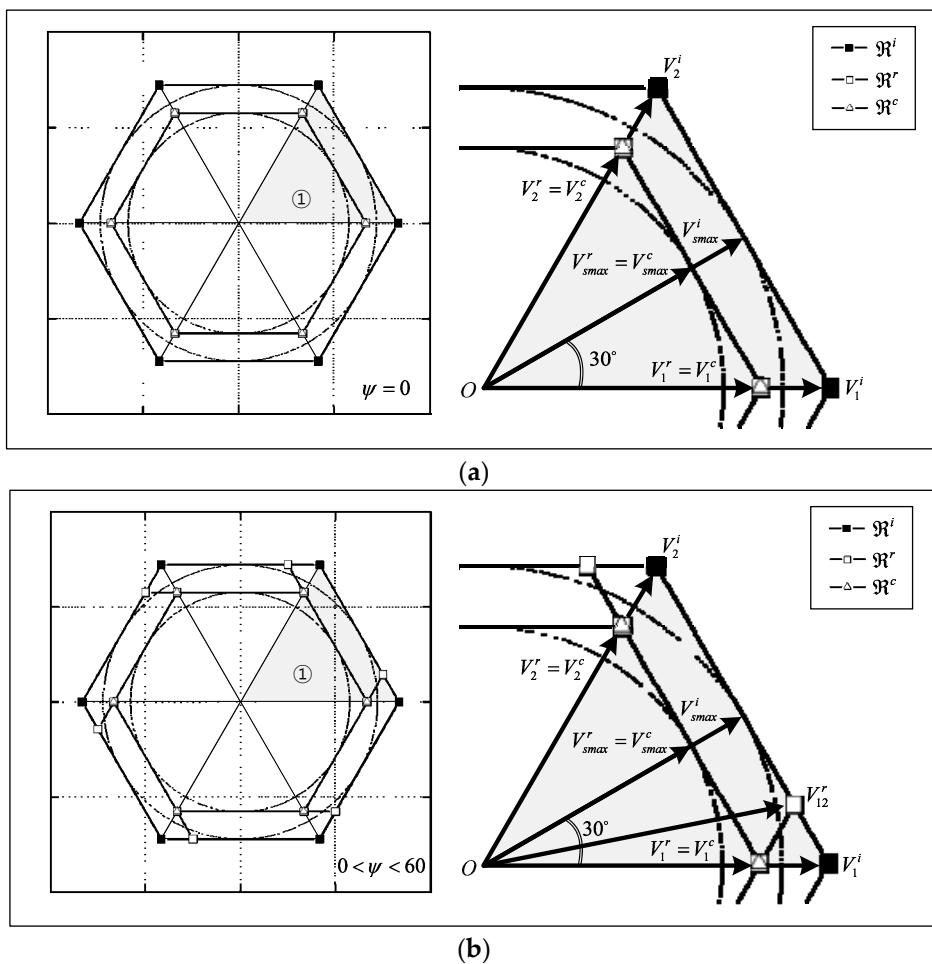

295 Figure 17 (a), (b), (c) and (d) are divided into four regions along the voltage region forms. In the

296 case of  $\psi$  being a negative phase value as a leading, it has a same form with a positive phase value

297 as Figure 17 since the distortion voltage from the dead-time is even function. Therefore, the MMPV

298 levels arrange in a Table 2 instead of illustrating the regions about negative phase value. Where  $\mathfrak{R}^i$ ,

299  $\mathfrak{R}^r$  and  $\mathfrak{R}^c$  are the output voltage region of the ideal three-phase VSI, the output voltage of the

300 three-phase VSI distorted by the dead-time and the output voltage region of the three-phase VSI

301 applied proposed DTCS. Because of the dead-time physically limits the period the turn on time of the

302 switch, even if the dead-time compensated, the physical limits of the inverter can not be

303 compensated. Consequently, when the proposed DTCS is applied, the compensated region  $\mathfrak{R}^c$  is

304 inscribed voltage region in the dead-time region  $\mathfrak{R}^r$ .

305 **Table 2.** The compensated MMPV  $V_{smax}^c$  when the proposed DTCS applied.

| Phase delay of current                                  | Phase voltage $V_{smax}^c$                 |

|---------------------------------------------------------|--------------------------------------------|

| $\psi = 0^\circ$                                        | from (42) $\frac{V_{dc} - 2V_d}{\sqrt{3}}$ |

| $0^\circ < \psi < 60^\circ, -60^\circ < \psi < 0^\circ$ | from (43) $\frac{V_{dc} - 2V_d}{\sqrt{3}}$ |

$$\psi = 60^\circ, \psi = -60^\circ \quad \text{from (46)} \quad \frac{\sqrt{3}}{2} |V_1^c|$$

$$60^\circ < \psi \leq 90^\circ, -90^\circ \leq \psi < -60^\circ \quad \text{from (50)} \quad \frac{V_{dc}}{\sqrt{3}}$$

---

306 4.2.1. where  $\psi = 0^\circ$

307 When the output voltage is in phase with phase current, the voltage distortion exactly coincides

308 with the six active voltage vectors as Figure 16 (a). Hence, by using the above equation (31) to (39),

309 the arbitrary voltage reference  $V^*$  in the sector ① can be expressed as follows using the

310 neighboring real voltage vectors  $V_1^r, V_2^r$ .

$$\begin{aligned} |V_1^r| &= |V_1^c| = |V_1^i| - \frac{4}{3} V_d \\ |V_2^r| &= |V_2^c| = |V_2^i| - \frac{4}{3} V_d \end{aligned} \quad (40)$$

311 The equation (36), (38) can be derived as

$$V^* \left( \cos \theta + \frac{1}{\sqrt{3}} \sin \theta \right) \leq \frac{2}{3} (V_{dc} - 2V_d) \quad (41)$$

$$\therefore V_{smax}^r = \frac{V_{dc} - 2V_d}{\sqrt{3}} \quad (\text{where } \theta = 30^\circ) \quad (42)$$

312 While the compensated region  $\mathfrak{R}^c$  is equal to the distorted real region  $\mathfrak{R}^r$ , the compensated

313 MMPV  $V_{smax}^c$  is defined as

$$\therefore V_{smax}^r = V_{smax}^c = \frac{V_{dc} - 2V_d}{\sqrt{3}} \quad (\text{where } \theta = 30^\circ) \quad (43)$$

314 4.2.2. where  $0^\circ < \psi < 60^\circ$

315 The proportions of the voltage vectors in Figure 17 (b) through Figure 16 (b) can be expressed as

$$V_{12}^r = \frac{2}{3} (V_{dc} - V_d) + j \frac{2}{3\sqrt{3}} V_d \quad (44)$$

$$|V_1^r| = |V_1^c| = \frac{2}{3} (V_{dc} - 2V_d) \quad (45)$$

316 Since the distorted real voltage vector  $V_{12}^r$  does not affect to the active voltage vector and output

317 voltage region in Figure 17 (b), the  $V_{smax}^c$  can be derived as

$$\therefore V_{smax}^r = V_{smax}^c = \frac{V_{dc} - 2V_d}{\sqrt{3}} \quad (\text{where } \theta = 30^\circ) \quad (46)$$

318 4.2.3. where  $\psi = 60^\circ$

319 In Figure 17 (c), the distorted voltage vector  $V_{12}^r$  affects the real output voltage region. It can be

320 expressed as following using Figure 16 (c).

$$V_{12}^r = \frac{2}{3}(V_{dc} - V_d) + j \frac{2}{\sqrt{3}}V_d \quad (47)$$

321 And the angle  $\varepsilon$  between the  $V_{12}^r$  and  $V_1^i$  is

$$\varepsilon = \tan^{-1} \left( \frac{\frac{2}{\sqrt{3}}V_d}{\frac{2}{3}(V_{dc} - V_d)} \right) \quad (48)$$

322 The maximum voltage vector magnitude  $|V_1^c|$  in the compensated voltage region  $\mathfrak{R}^c$

323 inscribed in the real voltage region  $\mathfrak{R}^r$  is derived as

$$|V_1^c| = \frac{2}{3}(V_{dc} - V_d) - \frac{2}{\sqrt{3}}V_d \frac{1}{\tan\left(\frac{\pi}{3} + \varepsilon\right)} \quad (49)$$

324 Therefore, the  $V_{smax}^c$  can be defined as equation (50) using the equation (36) to (38).

$$\therefore V_{smax}^c = \frac{\sqrt{3}}{2}|V_1^c| \quad (50)$$

325 4.2.4. where  $60^\circ < \psi \leq 90^\circ$

326 In Figure 17 (d), the voltage vectors  $V_{12}^r$ ,  $V_{21}^r$  that arisen in dead-time can be expressed as

327 follows in Figure 16 (d).

$$V_{12}^r = \frac{2}{3}(V_{dc} - V_d) + j \frac{2}{\sqrt{3}}V_d \quad (51)$$

$$V_{21}^r = \frac{2}{3}(V_{dc} + V_d) + j \frac{2}{\sqrt{3}}V_d \quad (52)$$

328 The degree  $\angle V_{21}^r V_1^c a$  is always  $60^\circ$  according to the equation (53)

$$\tan^{-1} \left( \frac{2/\sqrt{3}}{2/3} \right) = 60^\circ \quad (53)$$

329 As the line  $\overline{V_{12}^r V_{21}^r}$  is parallel to the voltage vector  $V_1^i$ , the additional voltage region  $\Delta V_{12}^r V_{21}^r V_1^i$

330 generated by the dead-time always forms a regular triangle so that the voltage vector  $V_{12}^r$  is adjoined

331 with ideal voltage region  $\mathfrak{R}^i$ . Therefore, the compensated MMPV  $V_{smax}^c$  has equal magnitude with

332 ideal modulation phase voltage  $V_{smax}^i$ .

$$\therefore V_{smax}^c = V_{smax}^i = \frac{V_{dc}}{\sqrt{3}} \quad (54)$$

### 333 5. The results of the simulation and experiment of the proposed DTCS

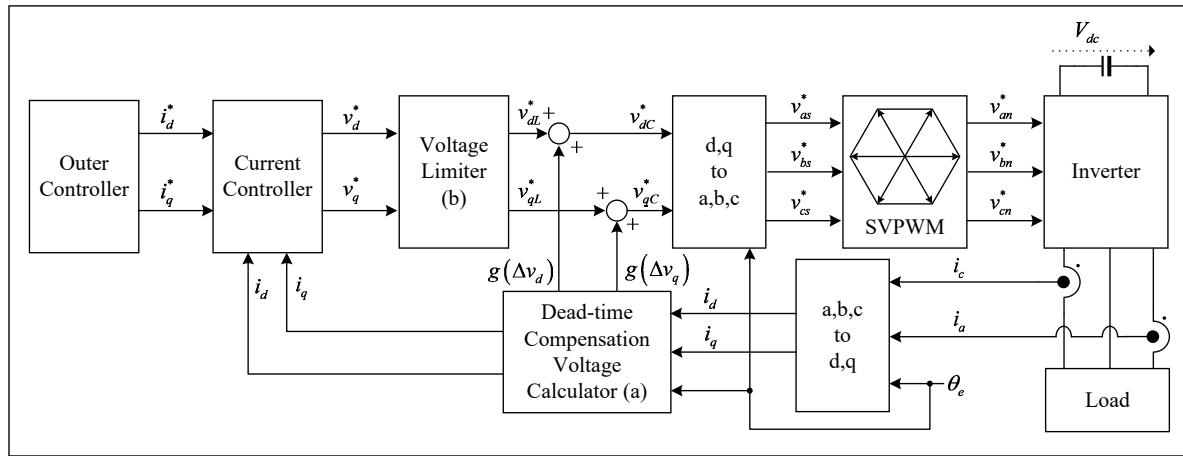

334 The Figure 18 is a simplified block diagram of three-phase VSI controller with the proposed

335 DTCS. Since the DTCV is feedforwarded at the controller output, there is no need to compensate for

336 the dead-time into the current controller state. Therefore, the error between the voltage reference of

337 the current controller and the output voltage of the three-phase VSI can be minimized, and it makes

338 easy to design the algorithms using the voltage reference  $v_{dl}^*, v_{ql}^*$ . As mentioned above, unless the

339 output of the current controller is appropriately limited, normal dead-time compensation is not

340 possible, so the current controller output  $v_d^*, v_q^*$  should be restricted as shown in block (b) in Figure

341 18. Here, the voltage limit can be defined according to the phase of the current through Table 2. Where

342 the outside of the current controller can be designed along the employed applications.

343

344 **Figure 18.** The control block diagram of three-phase VSI with proposed DTCS.

345 Figure 19 shows a block diagram of the proposed DTCS of Figure 18 (a). The TCV contains the

346 position calculate block which calculates and outputs current angles  $\theta_d$ ,  $\theta_d^*$  and the on-line TCV

347 controller block which regulates  $\phi$ ,  $T_{off}^*$  and outputs the references  $\phi^*$ ,  $T_{off}^*$  and compensation

348 voltage calculator block which implements TCV.

349

350 **Figure 19.** The specific block diagram of Figure 18 (a).

351 *5.1. The simulation results*

352 The proposed DTCS is verified using the simulation software Psim. The three-phase VSI and DTCS

353 design the same as in Figure 18, and the current controller is performed alone without outer control

354 loop. The circuit uses a three-phase VSI as shown in Figure 1. And in order to maximize the effect of

355 dead-time, the load is composed of only the inductors and the resistors without the back

356 electromotive force or the voltage sources. The switches modeled in SKM50GB063D manufactured

357 SEMIKRON are used to observe the effects of the output capacitors into the simulation result.

358 Detailed simulation specifications are shown in Table 3.

359 **Table 3.** The specifications of simulation.

| Parameters | Description | Value | Parameters | Description | Value |

|------------|-------------|-------|------------|-------------|-------|

|------------|-------------|-------|------------|-------------|-------|

|          |                       |              |              |                                                |               |

|----------|-----------------------|--------------|--------------|------------------------------------------------|---------------|

| $V_{dc}$ | Dc-link voltage level | 100 V        | $V_{ce}$     | Maximum collector - emitter voltage rating     | 600 V         |

| $R_s$    | Phase Resistance      | 0.5 $\Omega$ | $v_{G_{th}}$ | Gate Threshold voltage                         | 4.5 V         |

| $L_s$    | Phase inductance      | 10 mH        | $t_f$        | Fall time of the current when IGBT is turn off | 300 ns        |

| $f_{sw}$ | Switching Frequency   | 20 kHz       | $C_{ies}$    | Input capacitance                              | 2.2 nF        |

| $T_d$    | Dead-time             | 5.0 $\mu$ s  | $C_{oes}$    | Output capacitance                             | 2.2 nF        |

| $f_m$    | Fundamental frequency | 50 Hz        | $R_{ce\_on}$ | On resistance                                  | 28 m $\Omega$ |

360

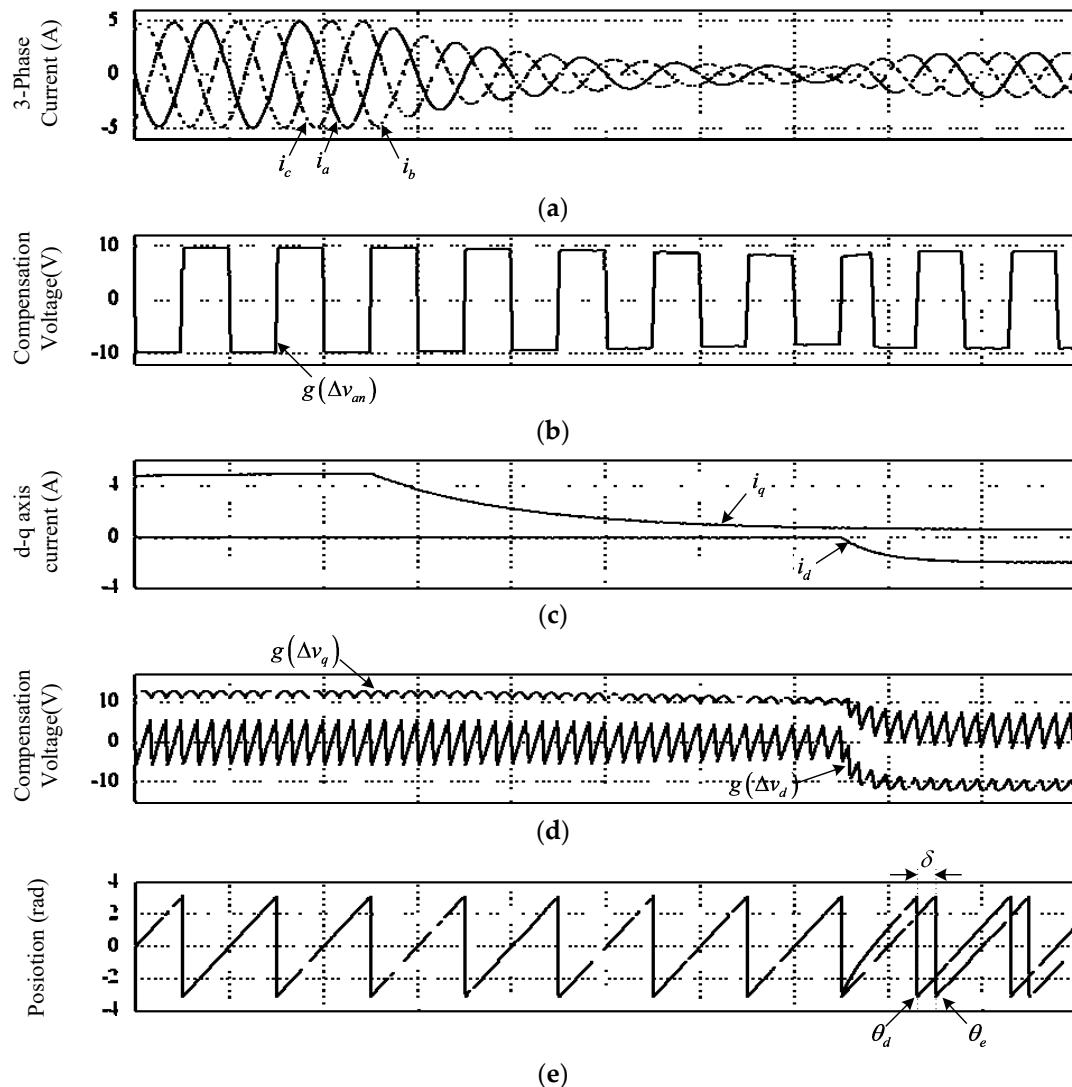

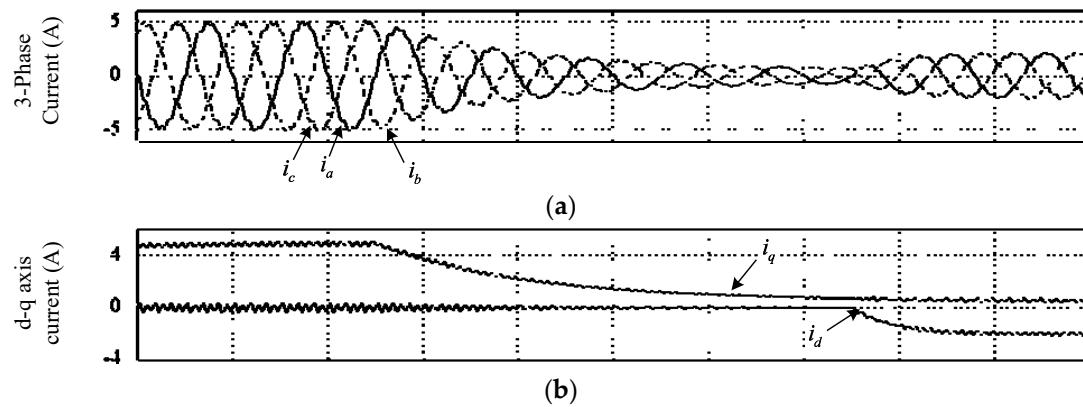

361 Figure 20 demonstrates the simulation results of the proposed DTCV with the above

362 specifications. Figure 20 (a) shows the compensated 3-phsae current waveforms and (d) is the

363 compensation voltage on the synchronous reference frame d-q axis. It can be confirmed that the

364 magnitudes of compensation voltages  $g(\Delta v_d)$ ,  $g(\Delta v_q)$  change according to the amplitude of the

365 current  $I_s$  and the fundamental component of the dead-time distortions shifts to the d-axis along

366 the d-axis current magnitude. Figure 20 (e) presents the position information of the three-phase

367 current vector  $I_s$  using the control position  $\theta_e$  and equation (21). It can validate that the position

368 of the  $I_s$  is changed along the d-q axis currents amounts.

369 Figure 20. Simulation results of the proposed DTCS; (a) 3-phsae currents; (b) TCV of a-phase; (c) d-q

370 axis currents on the synchronous reference frame; (d) DTCV on the synchronous reference frame d-q

371 axis; (e) positions.

372 Figure 21 indicates the simulation result to comparing the performance of the proposed DTCS

373 when any DTCS is not applied under the condition of Figure 20. Figure 21 (a) is the three-phase

374 currents and (b) is the d-q axis current on the synchronous reference frame. As the amount of the

375 current decreases, the harmonic distortions of the current become smaller. This is caused by the fact

376 that as the switch turn off delay  $T_{off}$  increases in the low current region. However, when  $T_{off}$  is in

377 the saturation region sufficiently, there is notable current distortions because of the current controller

378 can not compensate the voltage distortion of high orderth harmonic distortions. As a result, the

379 proposed DTCS applied three-phase currents has less than the 0.4% THD. Contrariwise, the three-

380 phase currents which is not applied DTCS have a 5.4% THD that is about 10 times larger than that.

381 **Figure 21.** Simulation results without DTCS; (a) three-phase currents; (b) d-q axis currents on the

382 synchronous reference frame.

### 383 5.2. The experimental results

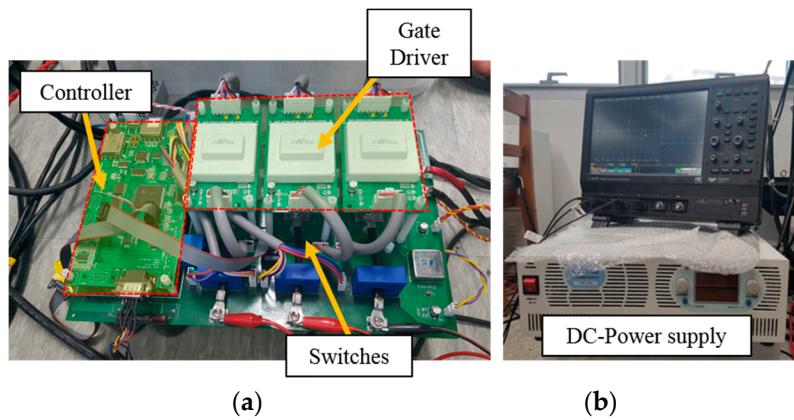

384 The experiment to verify the proposed DTCS is used three-phase VSI connected with DC-power

385 supply as shown Figure 22. And to maximize the effects of dead-time, it applied the only inductors

386 and resistances as a load. Detailed stipulations of the experiment are summarized in Table 4.

387 **Figure 22.** Experiment setting; (a) the three-phase VSI; (b) DC-power supply for the DC-link voltage

388 source.

389 **Table 4.** Experiment specifications.

| Parameters       | Description           | Value       |

|------------------|-----------------------|-------------|

| Switch ( $Q_n$ ) | three-phse VSI switch | SKM50GB063D |

|                 |                        |               |

|-----------------|------------------------|---------------|

| Gate driver     | Gate driver of VSI     | SKHI 22B      |

| MCU             | Micro controller unit  | DSP 320F28335 |

| DC Power supply | DC-link voltage source | TP5H-10D      |

| $V_{dc}$        | DC-link voltage level  | 310 V         |

| $R_s$           | Phase Resistance       | 5.5 $\Omega$  |

| $L_s$           | Phase inductance       | 20.5 mH       |

| $f_{sw}$        | Switching Frequency    | 15 kHz        |

| $T_d$           | Dead-time              | 5.0 $\mu$ s   |

390

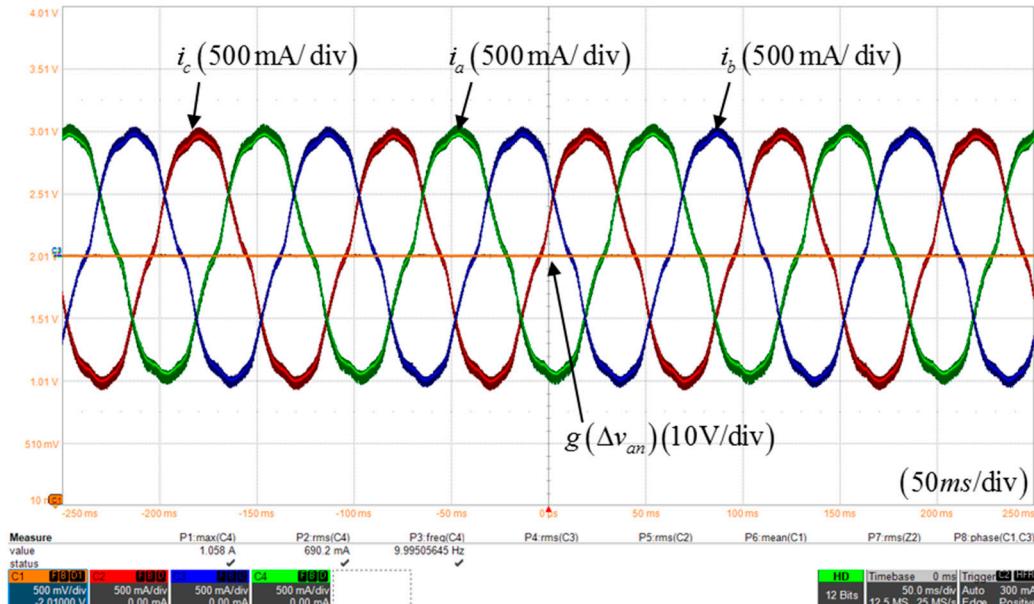

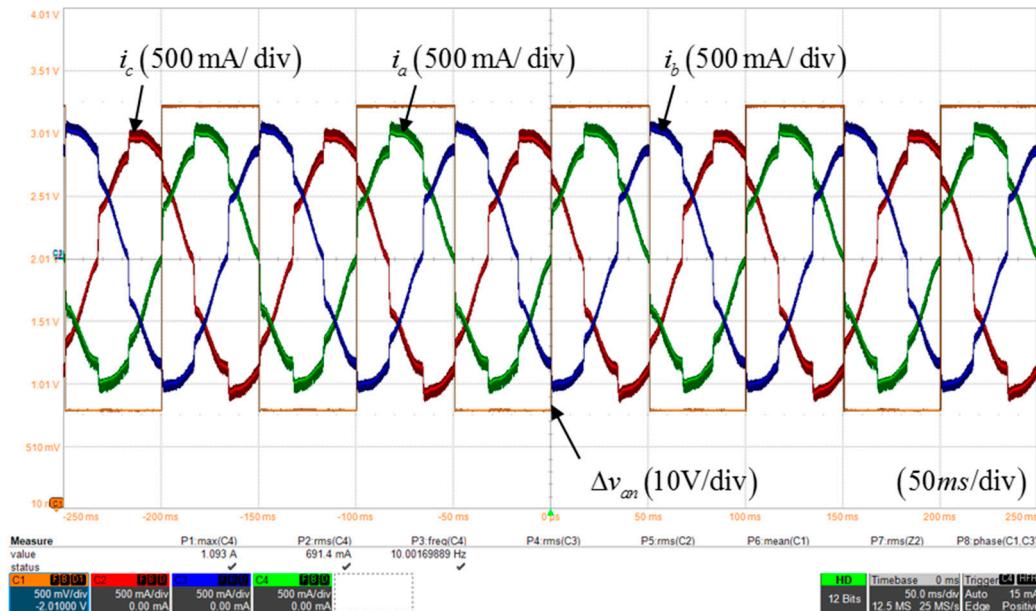

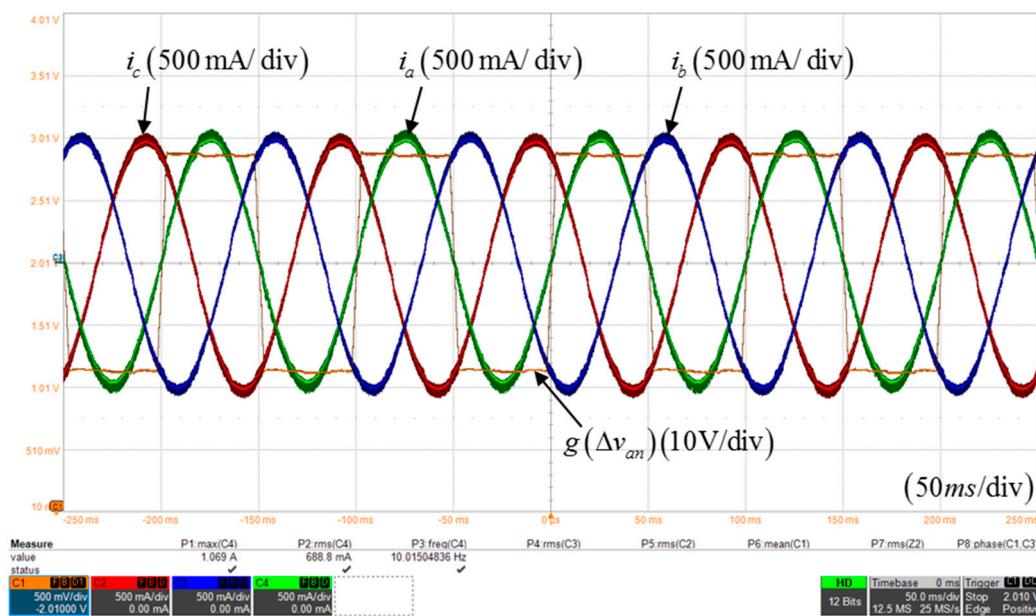

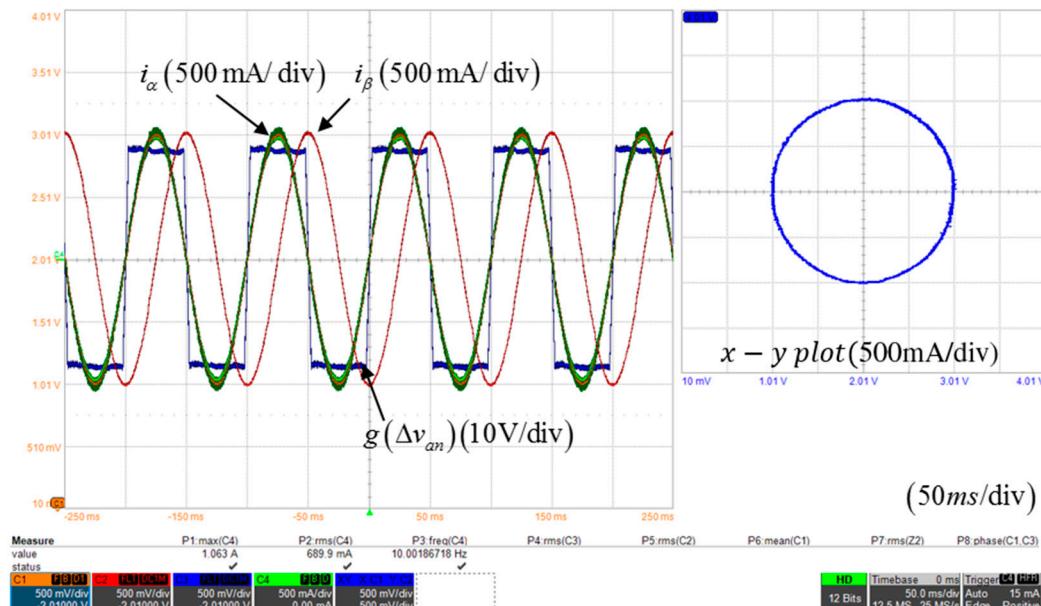

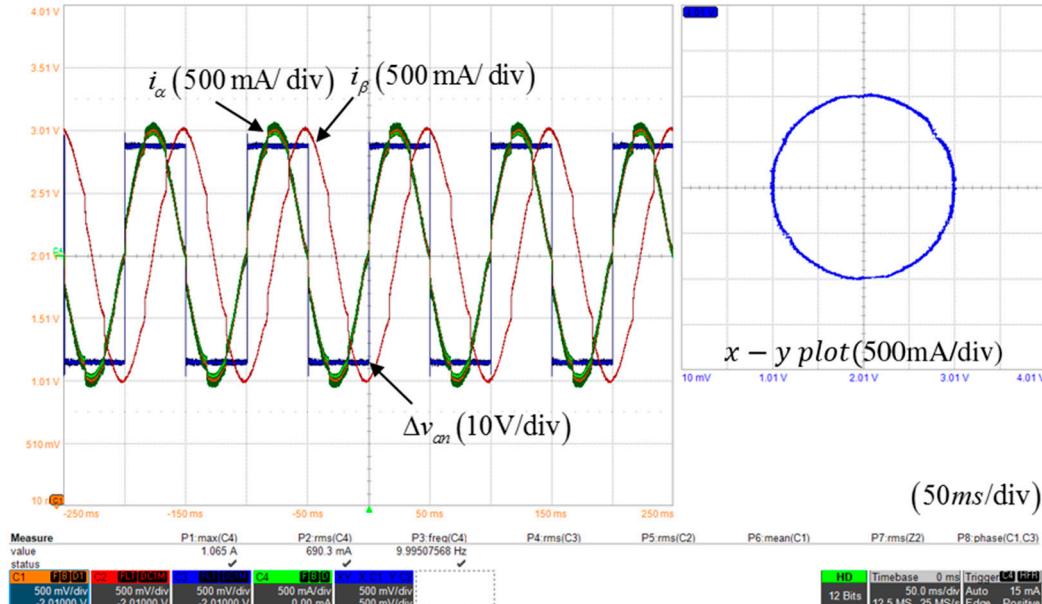

391 Figure 23, 24 and 25 shows the three-phase currents waveforms for comparing the performance

392 of the proposed DTCS with dead-time compensation pole voltage of the a-phase. The experimental

393 conditions of the phase current were keeping about 1.4% of the switch rate to perform in the region

394 where the effects of the switch's parasitic are present. Figure 23 is the three-phase current waveforms

395 without DTCS, and it can be seen that serious current distortions occurs near the zero crossing. Figure

396 24 illustrates the three-phase current waveforms when a conventional DTCS considering only dead-

397 time  $T_d$  is adapted. While the compensation voltage that does not reflect the variation of  $T_{off}$  is

398 larger than the actual voltage error. It can be confirmed that the current distortion due to the excessive

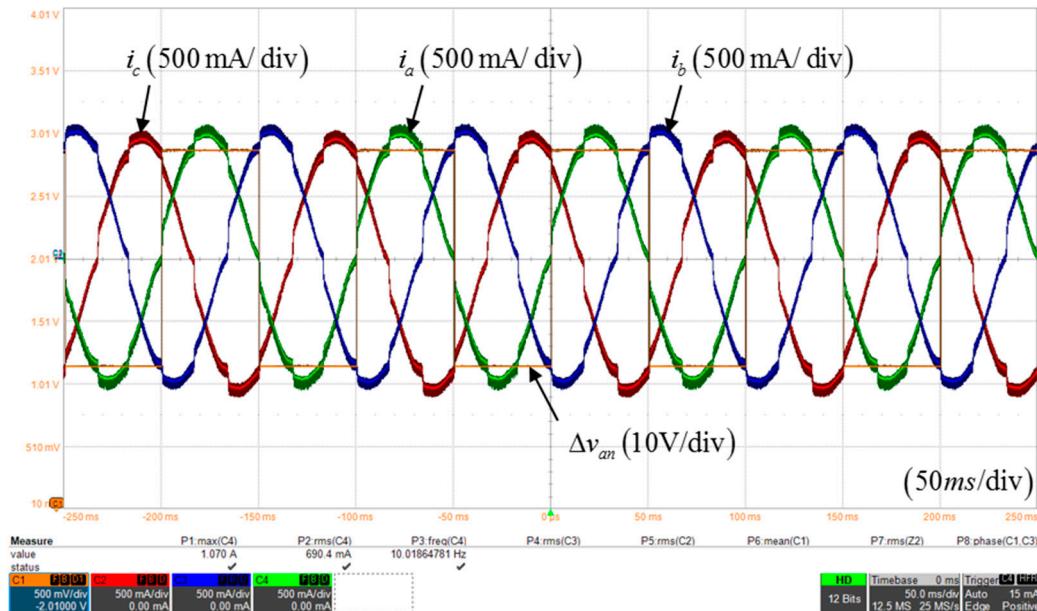

399 compensation voltage. Figure 25 reveals the currents waveforms of the proposed DTCS, which shows

400 very sinusoidal current waveform even in the low current region where affected by  $T_{off}$  variation.

401

402

403

Figure 23. three-phase current waveforms with a-phase dead-time compensation pole voltage adapting dead-time.

404

405

406

**Figure 24.** three-phase current waveforms with a-phase dead-time compensation pole voltage in case of adapting conventional DTCS.

407

408

409

**Figure 25.** three-phase current waveforms with a-phase dead-time compensation pole voltage in case of adapting proposed DTCS.

410

411

412

413

414

415

The Figure 26 displays waveforms for confirming the effects of the compensating pole voltage shape. The compensating pole voltage in the Figure 26 which shape is square whereas amplitude is equal with Figure 25. Even if it compensated with proper voltage level, the current distortions still exist near the zero-crossing points. Therefore, it can be proven that not only the amplitude of the compensation pole voltage but also the slope of it is a very important factor for correct dead-time compensation especially in low-current region.

416

417 **Figure 26.** three-phase current waveforms with a-phase dead-time compensation pole voltage with

418 equal amplitude with Figure 25.

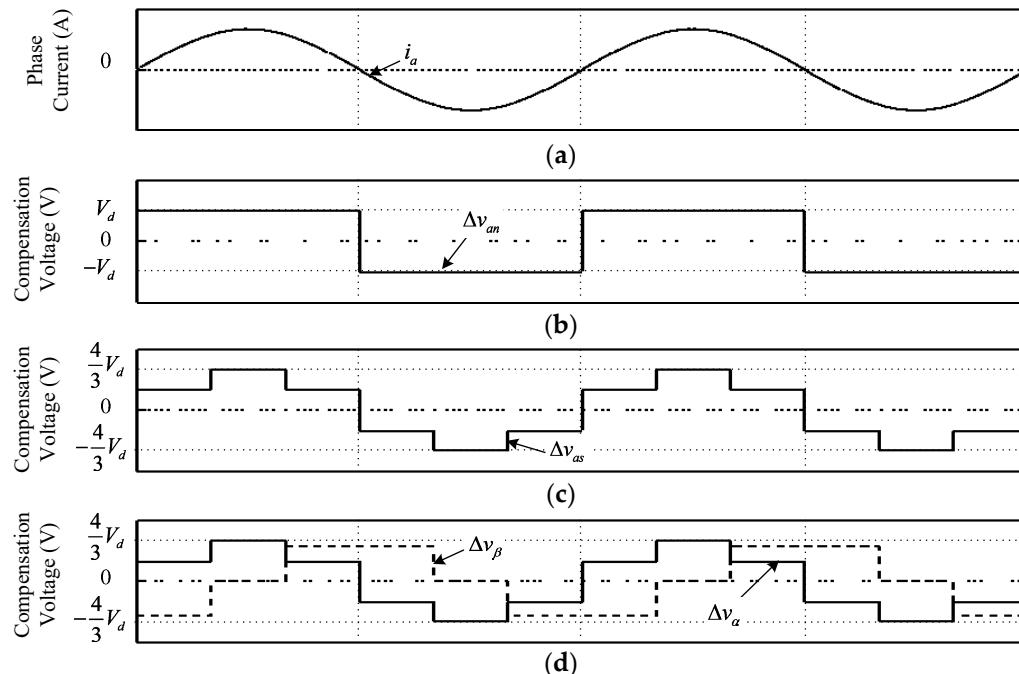

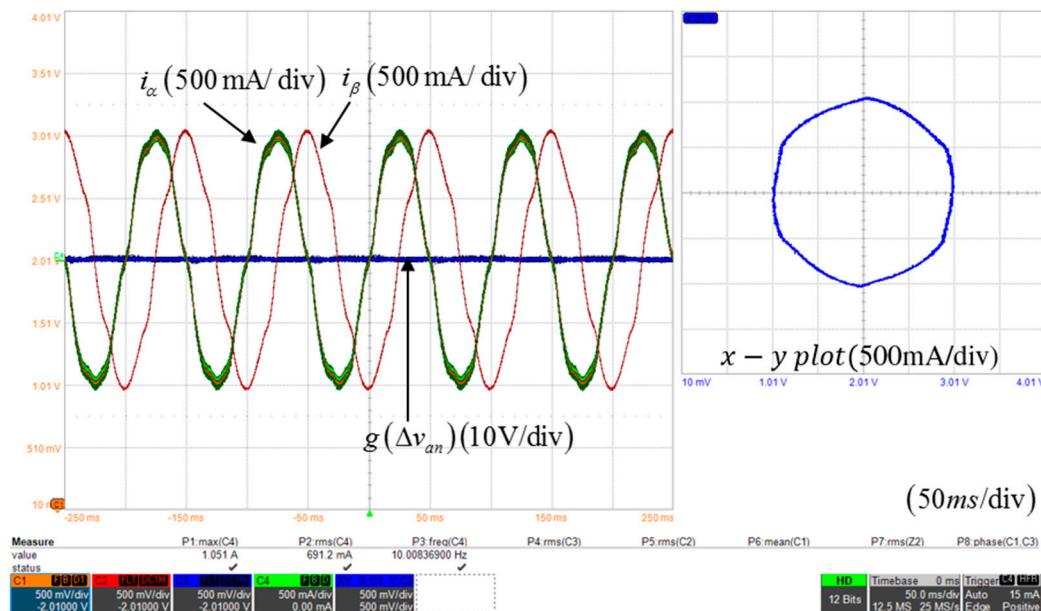

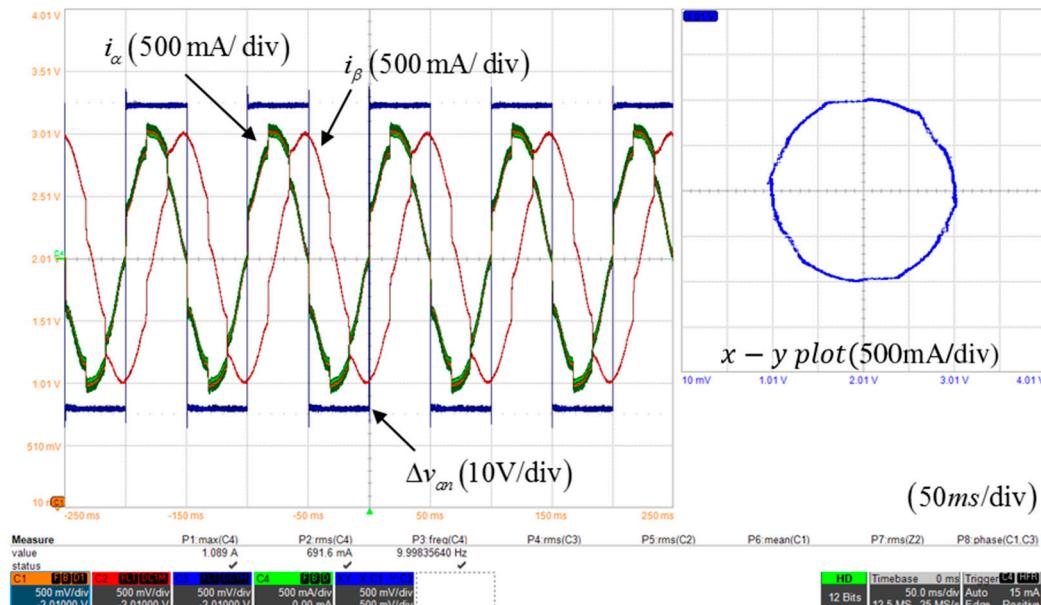

419 The Figure 27, 28, 29 and 30 show the  $\alpha - \beta$  axis currents on the stationary reference frame of

420 above three-phase current and also demonstrate the  $\alpha - \beta$  axis currents on the x-y plot that can

421 compare the distortion of the current more intuitively. The  $\alpha - \beta$  axis currents displayed using the

422 DAC. Since  $\alpha$ -axis current is equal the a-phase current, the both currents waveforms are overlapped

423 to check the function of DAC. The  $\alpha - \beta$  axis currents, as represented by the x-y plot, shows the

424 ideal circular shape as the ideal sinusoidal current waveforms.

425

426 **Figure 27.**  $\alpha - \beta$  axis currents on the stationary reference frame and on the x-y plot of Figure 23.

427

428

Figure 28.  $\alpha - \beta$  axis currents on the stationary reference frame and on the x-y plot of Figure 24.

429

430

Figure 29.  $\alpha - \beta$  axis currents on the stationary reference frame and on the x-y plot of Figure 25.431

432

433

434

435

Figure 29 demonstrates the currents waveforms on the stationary reference frame when the suggested DTCS is applied. The currents waveform on the x-y plot is close to the ideal circle than the waveforms in Figure 26, 27. The currents waveform in Figure 30 appear closer to the circle than in the Figure 27, 38. However, due to the current distortion near the zero-crossing point, it is impossible to display the ideal circular waveform as proposed DTCS's.

436

437

Figure 30.  $\alpha - \beta$  axis currents on the stationary reference frame and on the x-y plot of Figure 26.

438

439

440

441

442

443

444

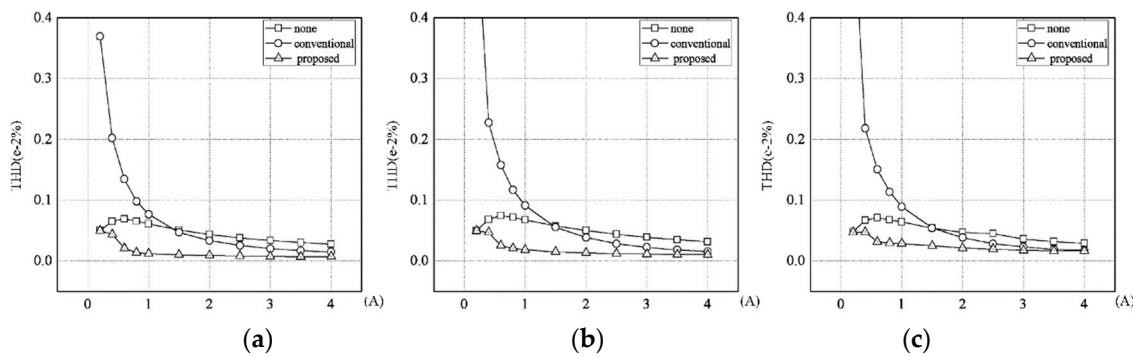

The current THD is computed in the several conditions to compare the performance of the proposed DTCS in Figure 31. The current THD figured according to the amplitude and fundamental frequency of the current in a-phase. The square and circle symbols represent the THD without DTCS as Figure 23 and the THD with DTCS only considering  $T_d$  as Figure 24 respectively. The triangle symbol is the THD of the a-phase current with the proposed DTCS as Figure 25. The vertical axis denotes the THD value of the a-phase current and the horizontal axis denotes the peak values of the three-phase current in Figure 31.

445

446

Figure 31. Comparing the THD according to the fundamental frequency of current; (a) 10Hz; (b) 30Hz; (c) 50Hz.

447

448

449

450

451

452

453

454

455

456

457

In case of the DTCS is applied which only considers dead-time  $T_d$ , the THD is very seriously high at the low current region where the  $T_{off}$  affects on the output voltage of the three-phase VSI. And the THD becomes decease as the current amplitude increasing because of the  $T_{off}$  effect is as saturated APVE as reduced. These results show that it is worse when inaccurate compensation voltage is applied than without any DTCS. In case of the any DTCS is not employed, the THD is low in the low current region since the influence of the dead-time is disappear due to the  $T_{off}$ . As the amplitude of the current increases, the impact of  $T_{off}$  is reduced. As a result, the current distortion gradually increases. However, the THD is becomes lower when the current level is more raised because of the duty ratio becomes enough large than the dead-time. The proposed DTSC shows much lower current THD in all current ranges. Especially, at the low current region, the proposed algorithm has a better performance than convention's by containing the on-line TCV controller.

458

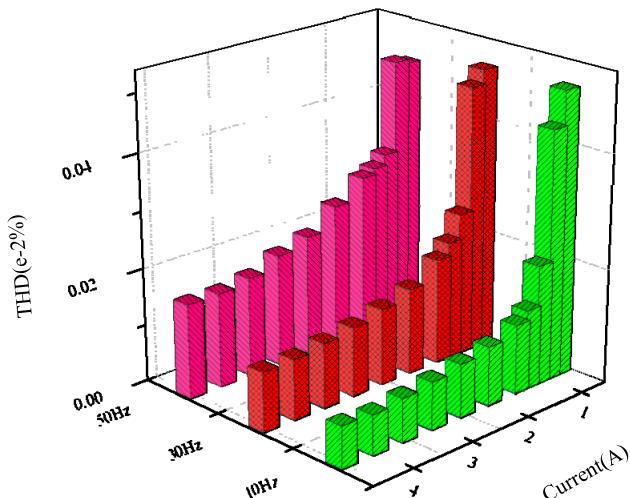

459 **Figure 32.** The differences of the THD along the fundamental frequency of the proposed DTCS.

460 Figure 32 shows the graphs comparing the current THD according to the fundamental frequency

461 when the suggested DTCS is adapted. It can be realized that the current THD arises along the current

462 frequency. The TCV should be generated to appropriate compensation but the fixed PWM is not

463 enough to produce the slop of the TCV for the high frequency. Therefore, in the high frequency, the

464 current THD is grown due to the imperfect TCV.

465 **6. Conclusions**

466 In this paper, the analysis of the output distortion of the three-phase VSI due to the dead-time

467 and the parasitic component of the switch has been conducted, and a novel method of simply

468 implementing the trapezoidal compensation voltage using the position of the three-phase current has

469 been proposed. In addition, a novel compensation voltage controller is proposed to adjust the slope

470 of the trapezoidal compensation voltage as well as the compensation voltage magnitude. That is

471 robust to the internal parameters and current variations. An analysis of the maximum linear

472 modulation region of the three-phase VSI is performed in parallel to normal operating at the high MI

473 area by limiting the voltage reference. The proposed dead-time compensation strategy has been

474 verified by simulation and experiment. The experimental results show that the it has excellent

475 performance over all current range.

476 **Author Contributions:** J.-W.L. designed the proposed strategy and implemented the system and performed the

477 experiments. H.Y. assisted a research and investigation process. Y.C. assisted with the idea development and

478 paper writing.

479 **Funding:** This work was supported by "Human Resources Program in Energy Technology" of the Korea

480 Institute of Energy Technology Evaluation and Planning (KETEP), granted financial resource from the Ministry

481 of Trade, Industry & Energy, Republic of Korea. (No. 20174030201660), and also this work was supported by the

482 National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT)(No.

483 2017R1C1B2009425).

484 **Acknowledgments:** This work was supported by "Human Resources Program in Energy Technology" of the

485 Korea Institute of Energy Technology Evaluation and Planning (KETEP), granted financial resource from the

486 Ministry of Trade, Industry & Energy, Republic of Korea. (No. 20174030201660), and also this work was

487 supported by the National Research Foundation of Korea(NRF) grant funded by the Korea government(MSIT)(No.

488 2017R1C1B2009425).

489 **Conflicts of Interest:** The authors declare no conflict of interest.

490

491

492 **References**

493 1. SUKEGAWA, Takashi, et al. Fully digital, vector-controlled PWM VSI-fed ac drives with an inverter dead-

494 time compensation strategy. In: *Industry Applications Society Annual Meeting, 1988., Conference Record of the*

495 *1988 IEEE*. IEEE, 1988. p. 463-469.

496 2. CHOI, Jong-Woo; SUL, Seung-Ki. Inverter output voltage synthesis using novel dead time

497 compensation. *IEEE transactions on Power Electronics*, 1996, 11.2: 221-227.

498 3. PELLEGRINO, Gianmario, et al. Self-commissioning algorithm for inverter nonlinearity compensation in

499 sensorless induction motor drives. *IEEE Transactions on Industry Applications*, 2010, 46.4: 1416-1424.

500 4. MORIMOTO, Shigeo; SANADA, Masayuki; TAKEDA, Yoji. High-performance current-sensorless drive

501 for PMSM and SynRM with only low-resolution position sensor. *IEEE Transactions on Industry Applications*,

502 2003, 39.3: 792-801.

503 5. KIM, Sam-Young, et al. Effective dead-time compensation using a simple vectorial disturbance estimator

504 in PMSM drives. *IEEE Transactions on Industrial Electronics*, 2010, 57.5: 1609-1614.

505 6. URASAKI, N., et al. Dead-time compensation strategy for permanent magnet synchronous motor drive

506 taking zero-current clamp and parasitic capacitance effects into account. *IEE Proceedings-Electric Power*

507 *Applications*, 2005, 152.4: 845-853.

508 7. MUÑOZ, Alfredo R.; LIPO, Thomas A. On-line dead-time compensation technique for open-loop PWM-

509 VSI drives. *IEEE Transactions on power electronics*, 1999, 14.4: 683-689.

510 8. GUHA, Anirudh; NARAYANAN, G. An improved dead-time compensation scheme for voltage source

511 inverters considering the device switching transition times. In: *Power Electronics (IICPE), 2014 IEEE 6th India*

512 *International Conference on*. IEEE, 2014. p. 1-6.

513 9. HWANG, Seon-Hwan; KIM, Jang-Mok. Dead time compensation method for voltage-fed PWM

514 inverter. *IEEE Transactions on energy conversion*, 2010, 25.1: 1-10.

515 10. RYU, Ho-Seon, et al. A dead time compensation method in voltage-fed PWM inverter. In: *Industry*

516 *Applications Conference, 2006. 41st IAS Annual Meeting. Conference Record of the 2006 IEEE*. IEEE, 2006. p. 911-

517 916.

518 11. ZHAO, Hengbing; WU, QM Jonathan; KAWAMURA, Atsuo. An accurate approach of nonlinearity

519 compensation for VSI inverter output voltage. *IEEE transactions on power electronics*, 2004, 19.4: 1029-1035.

520 12. KIM, Sam-Young; PARK, Seung-Yub. Compensation of dead-time effects based on adaptive harmonic

521 filtering in the vector-controlled AC motor drives. *IEEE Transactions on Industrial Electronics*, 2007, 54.3:

522 1768-1777.

523 13. URASAKI, Naomitsu, et al. An adaptive dead-time compensation strategy for voltage source inverter fed

524 motor drives. *IEEE Transactions on Power Electronics*, 2005, 20.5: 1150-1160.

525 14. KIM, Hyun-Soo; MOON, Hyung-Tae; YOUN, Myung-Joong. On-line dead-time compensation method

526 using disturbance observer. *IEEE Transactions on Power Electronics*, 2003, 18.6: 1336-1345.

527 15. PARK, Yongsoon; SUL, Seung-Ki. Implementation schemes to compensate for inverter nonlinearity based

528 on trapezoidal voltage. *IEEE Trans. Ind. Appl.*, 2014, 50.2: 1066-1073.

529 16. PARK, Yongsoon; SUL, Seung-Ki. A novel method utilizing trapezoidal voltage to compensate for inverter

530 nonlinearity. *IEEE Transactions on power Electronics*, 2012, 27.12: 4837-4846.

531 17. ZHANG, Zhendong; XU, Longya. Dead-time compensation of inverters considering snubber and parasitic

532 capacitance. *IEEE Transactions on Power Electronics*, 2014, 29.6: 3179-3187.