1 Article

# 2 Optimization of Line-Tunneling Type L-Shaped

# 3 Tunnel Field-Effect-Transistor for Steep

### 4 Subthreshold Slope

- 5 Faraz Najam 1 and Yun Seop Yu 1,\*

- <sup>1</sup> Department of Electrical, Electronic and Control Engineering and IITC, Hankyong National University

- 7 \* Correspondence: ysyu@hknu.ac.kr; Tel.: +81-31-670-5293

**Abstract:** Recently L-shaped tunneling field-effect-transistor (LTFET) has been introduced to overcome the thermal subthreshold limit of conventional metal-oxide-semiconductor field-effect-transistors (MOSFET). In this work, shortcoming of LTFET was investigated. It was found that corner effect present in LTFET effectively degrades its subthreshold slope. To get rid of corner effect a new type of device with dual material gates is presented. The new device termed as DG-LTFET gets rid of the corner effect and results in a significantly improved subthreshold slope of less than 10 mV/dec, and an improved ON/OFF current ratio over LTFET. In this work DG-LTFET was evaluated for different device parameters, and bench-marked against LTFET. This work presents an optimum configuration of DG-LTFET in terms of device dimensions and doping levels, to get the best subthreshold, ON current and ambipolar performance from the DG-LTFET.

**Keywords:** Band-to-band tunneling, L-shaped tunnel field-effect-transistor, double-gate tunnel field-effect-transistor, corner-effect.

### 1. Introduction

Tunnel field-effect-transistors (TFET) are being actively pursued as a potential replacement to conventional complementary metal-oxide-semiconductor (CMOS) technology [1]. TFETs offer sub-thermal subthreshold slope (SS) but suffer from limited ON current *I*<sub>ON</sub> performance [2]. To overcome the limit, recently different types of line tunneling type TFETs have been introduced including L-shaped TFET [3] (LTFET), U-shaped [4] (UTFET), and Z-shaped [5] TFET (ZTFET). Among them, only LTFET has been experimentally demonstrated [3].

It was found using device simulations that 2-dimenasional (2D) corner effect [6] present in LTFET degrades its subthreshold performance. In order to remove SS degradation due to the kink effect induced by the source corner, the fully depleted rounded corner with gradual doping profile was used [6]. LTFET still achieves sub-thermal SS but as shown in this work there is room for significant improvement in the subthreshold performance of LTFET. To achieve this improvement, a new device based on the original LTFET is introduced in this work. The new device uses a dual-gate (DG) structure, and is termed as DG-LTFET. The two gates (gate1 and gate2) have different workfunctions and different heights. DG-LTFET was thoroughly evaluated for different device parameters including the source region height, gate1 and gate2 heights, gate1 and gate2 workfunctions, channel thickness, and drain doping levels. Optimum dimensions and drain doping level were determined for the DG-LTFET. Section 2 briefly discusses the corner-effect problem of LTFET. Section 3 introduces DG-LTFET, and compares its results with LTFET. Section 4 presents conclusion.

(c) (i)

#### 2. LTFET: Corner Effect

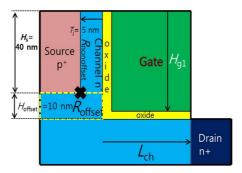

Fig. 1 shows a schematic for LTFET. The p<sup>+</sup> ( $10^{20}$  cm<sup>-3</sup>) doped source region overlaps the gate with the n<sup>-</sup> ( $10^{12}$  cm<sup>-3</sup>) channel sandwiched in between them. This sandwiched channel region is termed as  $R_{\text{nonoffset}}$ . Also, there is a part of the channel termed as  $R_{\text{offset}}$  in which there is an offset present between the source and the gate as indicted in Fig. 1. The following parameters were used for all devices considered in this work unless otherwise specified. Source height ( $H_{\text{s}}$ ) = 40 nm, oxide thickness ( $t_{\text{ox}}$ ) = 2 nm, length of  $R_{\text{nonoffset}}$  ( $H_{\text{in}}$ ) = 5 nm, channel length ( $H_{\text{ch}}$ ) = 50 nm, height of  $H_{\text{nonoffset}}$ 0 nm, height of  $H_{\text{nonoffset}}$ 1 nm, dielectric permittivity  $H_{\text{ox}}$ 2 = 25, metal gate workfunction  $H_{\text{rk}}$ 1 = 4.72 eV, and drain doping ( $H_{\text{ol}}$ 1) =  $H_{\text{ox}}$ 3.

Figure 1. Schematic of LTFET.

Sentaurus technology-computer-aided-design tool (TCAD) was used as the simulator [7]. The following models were used in the simulation: dynamic nonlocal band-to-band-tunneling (BTBT) model, fermi statistics, and constant mobility model. Dynamic nonlocal BTBT model calculates BTBT in both lateral and 1-dimensional (1D) directions. Crystal orientation is assumed to be <100> in all devices. A constant electron effective tunneling mass of 0.19  $m_0$  was used in all simulations [8]. All simulation were done at drain source bias  $V_{\rm ds} = 0.1$  V unless otherwise specified.

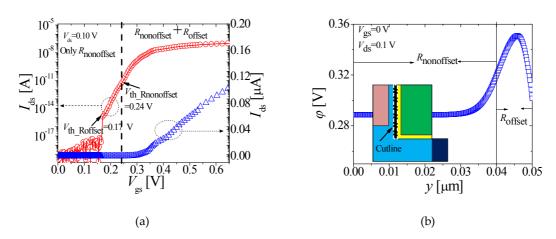

**Figure 2.** (a).  $I_{ds}$ - $V_{gs}$  transfer characteristics of LTFET. Indicated are  $V_{th\_Rnonoffset}$  = 0.24 V, and  $V_{th\_Roffset}$  = 0.17 V. (b) Potential along the cutline shown in the inset at  $V_{gs}$  = 0 V. Potential is higher in  $R_{offset}$ .

For analysis to follow, drain-source current ( $I_{ds}$ ) versus gate-source bias ( $V_{gs}$ ) characteristics of the LTFET are shown in Fig. 2(a). There is a direct overlap between gate and source in  $R_{nonoffset}$ , and the electric field in  $R_{nonoffset}$  is in 1D direction. However, in  $R_{offset}$ , electric field from the gate converges around the sharp source corner marked by an  $\mathbf{X}$  in Fig. 1. This increases the potential in  $R_{offset}$  as compared to  $R_{nonoffset}$  for any given bias (until potential saturates due to electron inversion). Fig. 2(b) shows the surface potential at  $V_{gs} = 0$  V. It can be seen that because the electric field

converges around the sharp source corner [6], the potential in  $R_{\text{offset}}$  has increased. Since the potential is higher in  $R_{\text{offset}}$  as compared to  $R_{\text{nonoffset}}$ , the threshold voltage for BTBT in  $R_{\text{offset}}$  ( $V_{\text{th\_Ronoffset}}$ ) is lower than the threshold voltage for BTBT in  $R_{\text{nonoffset}}$  ( $V_{\text{th\_Ronoffset}}$ ).

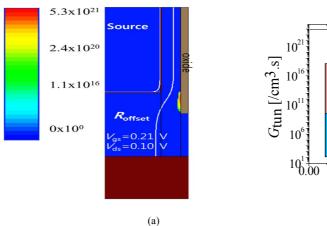

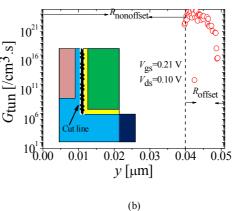

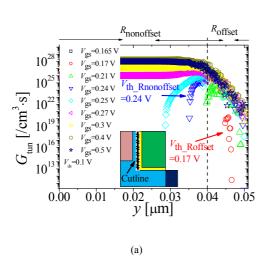

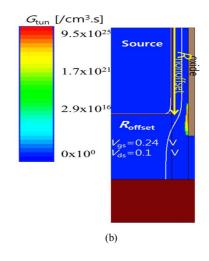

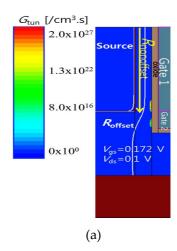

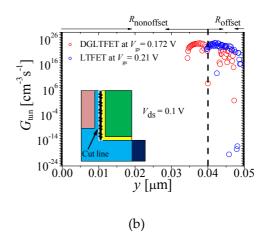

Figs. 3(a) and (b) show the tunneling rate ( $G_{tun}$ ) contour plot and  $G_{tun}$ , respectively at  $V_{gs} = 0.21$  V which is the bias needed to generate  $I_{ds} = 10^{-13}$  A (from Fig. 2(a)). It is obvious from Fig. 3 that the BTBT only takes place in  $R_{offset}$  whereas  $R_{nonoffset}$  is completely switched off. Fig. 4(a) shows  $G_{tun}$  at several  $V_{gs}$  values. From Fig. 4(a)  $V_{th\_Ronoffset}$  and  $V_{th\_Ronoffset}$  can be found to be around  $V_{gs} = 0.17$  and 0.24 V, respectively. Fig. 4(b) shows  $G_{tun}$  contour plot at  $V_{gs} = V_{th\_Ronoffset} = 0.24$  V. It can be noticed from Fig. 4(a) that  $G_{tun}$  in  $R_{nonoffset}$  just after it turns on, is always higher and has much larger BTBT area (in y direction) as compared to  $R_{offset}$ . Thus whenever  $R_{nonoffset}$  turns on, it dominates over  $R_{offset}$ . The reason why  $G_{tun}$  is higher in  $R_{nonoffset}$  is simply because the BTBT paths in  $R_{nonoffset}$  are laterally oriented or 2D from source to the surface in  $R_{offset}$ , whereas the BTBT paths in  $R_{nonoffset}$  are 1D. The 2D BTBT paths being naturally longer than the 1D paths result in lower  $G_{tun}$  in  $R_{offset}$ .

**Figure 3.** (a)  $G_{\text{tun}}$  contour plot at  $V_{\text{gs}} = 0.21$  V, which is the bias needed to generate  $I_{\text{ds}} = 10^{-13}$  A and (b)  $G_{\text{tun}}$  extracted from Fig. 3(a).

Figure 4. (a)  $G_{\text{tun}}$  at different  $V_{\text{gs}}$ . Indicated in Fig. 4(a) are  $V_{\text{th\_Rnonoffset}} = 0.24 \text{ V}$ , and  $V_{\text{th\_Roffset}} = 0.17 \text{ V}$  and (b)  $G_{\text{tun}}$  contour plot at  $V_{\text{gs}} = V_{\text{th\_Rnonoverlap}} = 0.24 \text{ V}$ . In Fig. 4(b), yellow arrow indicates the height of  $R_{\text{nonoffset}}$ .

From Fig. 4(a), it can be observed that for a large part of the subthreshold region ( $V_{\rm gs}$  < 0.24 V) only  $R_{\rm offset}$  with the longer 2D BTBT paths and lower  $G_{\rm tun}$  is contributing to the BTBT current and the more efficient  $R_{\rm nonoffset}$  makes no contribution to the current. In other words, LTFET underperforms in the subthreshold region. If  $R_{\rm nonoffset}$  could be forced to turn on at a lower bias than  $R_{\rm offset}$  that is the

condition  $V_{\text{th\_Rnonoffset}} < V_{\text{th\_Roffset}}$ ,  $R_{\text{nonoffset}}$  will turn on in the subthreshold region, and with the condition,  $G_{\text{tun}}$  in  $R_{\text{nonoffset}} > G_{\text{tun}}$  in  $R_{\text{offset}}$ , demonstrated in Fig. 4(a), a significant improvement in SS could be expected.

#### 3. DG-LTFET

#### 3.1. DG-LTFET: Basic Device Physics

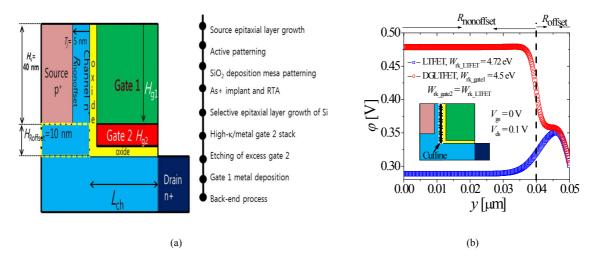

In order to achieve the condition  $V_{\text{th\_Rnonoffset}} < V_{\text{th\_Rnoffset}}$ , DG-LTFET is presented in Fig. 5(a). DG-LTFET uses dual material gates denoted by gate1 and gate2, each with a different workfunction  $(W_{\text{rk\_gate1/2}})$  and height  $(H_{\text{g1/2}})$ .  $H_{\text{g1}} = H_{\text{nonoffset}} = H_{\text{s}} = 40$  nm,  $H_{\text{offset}} = 10$  nm,  $H_{\text{g2}} = H_{\text{nonoffset}} - H_{\text{g1}} + (H_{\text{offset}} - t_{\text{ox}}) = 8$  nm, and  $T_{\text{j}} = 5$  nm.  $W_{\text{rk\_gate1}}$  is always lower than  $W_{\text{rk\_gate2}}$ .  $W_{\text{rk\_gate2}}$  is fixed at  $W_{\text{rk\_LTFET}} = 4.72$  eV for all DG-LTFET considered in this work. DGLTFET process-flow is indicated in Fig. 5(a). The process-flow is based on LTFET process-flow [3]. DGLTFET process-flow follows LTFET process-flow until the metal-organic chemical vapor deposition of gate 2 (similar to gate deposition in LTFET). After this two additional steps are required. The device is masked to protect the gate oxide and channel areas, and gate 2 is selectively etched according to desired height. Metal of Gate 1 is then deposited in the recess created by gate 2-etching. Similar dual-material gate structures have been extensively reported in the literature including [9-11].

Lower  $W_{rk\_gate1}$  results in an increased flatband voltage ( $V_{fb}$ ) [12] in  $R_{nonoffset}$  as compared to  $R_{offset}$ . Fig. 5(b) shows  $V_{fb}$  of DG-LTFET (red symbols) with  $W_{rk\_gate1}$  = 4.5 eV and  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ . Also  $V_{fb}$  of LTFET (blue symbols) is shown for reference. Expectedly DG-LTFET potential increases in  $R_{nonoffset}$ . The potential does not change abruptly from gate1 to gate2 because of the presence of 2D effects around the source corner. Electric field from bottom of gate2 converges around the source corner. Around the middle of  $R_{offset}$ , equilibrium is established between the two gates and DG-LTFET potential overlaps LTFET potential since  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ . With  $W_{rk\_gate1} < W_{rk\_gate2}$ , the increased potential in  $R_{nonoffset}$  reduces  $V_{th\_Ronoffset}$ . If  $W_{rk\_gate1/2}$  are appropriately tuned with  $W_{rk\_gate1} < W_{rk\_gate2}$ , the condition  $V_{th\_Ronoffset} < V_{th\_Roffset} = 0.17$  V could be achieved. Because  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$  = 4.72 eV,  $V_{th\_Roffset}$  (in DG-LTFET) is equal to  $V_{th\_Roffset}$  (in LTFET).

**Figure 5.** (a) Schematic of DG-LTFET with process-flow indicated alongside and (b)  $V_{\text{fb}}$  of DG-LTFET (red symbols) compared with that of LTFET (blue symbols). In DG-LTFET,  $W_{\text{rk\_gate1}} = 4.5$  eV and  $W_{\text{rk\_gate2}} = W_{\text{rk\_LTFET}} = 4.72$  eV were used.

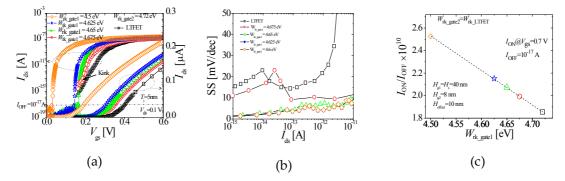

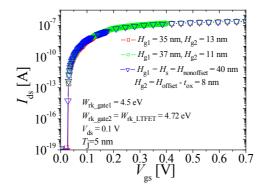

Figs. 6(a), (b), and (c) show  $I_{ds}$ - $V_{gs}$  characteristics at different  $W_{rk\_gate1}$ , SS, and  $I_{ON}/I_{OFF}$  of DG-LTFET with constant  $W_{rk\_gate2} = W_{rk\_LTFET} = 4.72$  eV for all DG-LTFET, respectively. Also the  $I_{ds}$ - $V_{gs}$  characteristics of LTFET (black squares) are shown for reference.  $I_{ON}$  is extracted at  $V_{gs} = 0.7$  V, and  $I_{OFF}$  is defined as  $I_{ds} = 10^{-17}$  A. With  $W_{rk\_gate1} = 4.675$  eV (red circles), the  $V_{th\_Rnonoffset}$  is reduced to 0.189 V. Compared with LTFET,  $R_{nonoffset}$  now turns on earlier in the subthreshold region, along with  $R_{offset}$ . Since BTBT is more efficient in  $R_{nonoffset}$  (Fig. 4(a)) as compared to  $R_{offset}$ ,  $I_{ds}$  increases more rapidly within the subthreshold region. Hence, just at the transition point, where  $R_{nonoffset}$  turns on ( $V_{gs} \sim 0.189$ ) a kink appears in the  $I_{ds}$ - $V_{gs}$  curve. With  $W_{rk\_gate1} = 4.65$  eV (green triangles),  $V_{th\_Rnonoffset}$  is reduced to  $V_{gs} = 0.167$  V and the condition  $V_{th\_Rnonoffset} < V_{th\_Roffset}$  is achieved and DG-LTFET exhibits a remarkable SS with values less than 10 mV/dec as seen in Fig. 6(b). With  $W_{rk\_gate1} = 4.625$  eV (blue stars),  $V_{th\_Rnonoffset}$  reduces further to 0.1448 V which is  $V_{th\_Roffset}$ . If  $V_{th\_Rnonoffset} < V_{th\_Roffset}$  is established than any increase in  $V_{th\_Roffset} - V_{th\_Rnonoffset}$  simply shifts the  $I_{ds}$ - $V_{gs}$  to the left without any change in SS as shown by the blue stars ( $W_{rk\_gate1} = 4.625$  eV) and orange diamonds ( $W_{rk\_gate1} = 4.5$  eV) in Figs. 6(a) and (b), respectively. An improvement of ~16 % is observed in  $I_{ON}/I_{OFF}$  of DG-LTFET (with  $W_{rk\_gate1} = 4.625$  eV) over LTFET.

**Figure 6.** (a).  $I_{ds}$ - $V_{gs}$  characteristics of DG-LTFET with different  $W_{rk\_gate1}$  and fixed  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ . Also shown is  $I_{ds}$ - $V_{gs}$  characteristics of LTFET (black squares). (b) SS extracted from  $I_{ds}$ - $V_{gs}$  characteristics in Fig. 8(a). Red circles:  $W_{rk\_gate1}$  = 4.675 eV, Green triangles:  $W_{rk\_gate1}$  = 4.65 eV, Blue stars:  $W_{rk\_gate1}$  = 4.625 eV, Orange diamonds:  $W_{rk\_gate1}$  = 4.5 eV.

**Figure 7.** (a)  $G_{\text{tun}}$  contour plot of DG-LTFET with  $W_{\text{rk\_gate1}} = 4.65$  eV at  $V_{\text{gs}} = 0.172$  V, which is needed to generate  $I_{\text{ds}} = 10^{-13}$  A and (b)  $G_{\text{tun}}$  extracted from Fig. 7(a) (red symbols). Also  $G_{\text{tun}}$  (blue symbols) of LTFET at a  $V_{\text{gs}}$  bias needed to generate  $I_{\text{ds}} = 10^{-13}$  A are shown for reference. In Fig. 7(a), yellow arrow indicates the height of  $R_{\text{nonoffset}}$ .

Fig. 7(a) shows  $G_{tun}$  contour plot of DG-LTFET at a  $V_{gs}$  (= 0.172 V) bias needed to achieve an equivalent  $I_{ds}$  of  $10^{-13}$  A in DG-LTFET with  $W_{rk\_gate1}$  = 4.65 eV. Fig. 7(b) shows contour plot extracted from Fig. 7(a). For reference Fig. 7(b) also shows  $G_{tun}$  needed to generate an equivalent amount of  $I_{ds}$  in LTFET (at a  $V_{gs}$  bias of 0.21 V, Fig. 3(b)). As can be seen in Fig. 7(b), LTFET needs contribution only from  $R_{offset}$ , but to generate the same amount of  $I_{ds}$ , DG-LTFET depends heavily on  $R_{nonoffset}$  with some contribution from  $R_{offset}$ . Because  $G_{tun}$  in  $R_{nonoffset}$  is more efficient (Fig. 4(a)), as the  $V_{gs}$  bias increases,  $G_{tun}$  increases exponentially in a much larger area in  $R_{nonoffset}$  which results in the DG-LTFET exhibiting a much steeper subthreshold swing, while the LTFET continues to depend only on the inefficient BTBT in  $R_{offset}$  until around  $V_{th\_Rnonoffset}$  = 0.24 V.

#### 3.2. Device Optimization

To optimize device performance, impact of variations in key parameters including  $H_{g1/2}$ ,  $H_s/T_j$ , and  $N_d$  was investigated. To investigate the impact of  $H_{g1/2}$  values,  $I_{ds}-V_{gs}$  characteristics for DG-LTFET at different  $H_{g1}$  and  $H_{g2} = H_{nonoffset} - H_{g1} + (H_{offset} - t_{ox})$  with fixed  $W_{rk\_gate1} = 4.5$  eV and  $W_{rk\_gate2} = W_{rk\_LTFET}$ ,  $H_s = H_{nonoffset} = 40$  nm,  $H_{offset} = 10$  nm, and  $T_j = 5$  nm is presented in Fig. 8. It can be seen that  $I_{ds}$  is independent of  $H_{g1/2}$ .

7 of 10

**Figure 8.**  $I_{ds}$ - $V_{gs}$  characteristics for several  $H_{g1/2}$ s with  $W_{rk\_gate1/2}$  = 4.5 eV and  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ . Red squares, green circles, and blue triangles:  $H_{g1}$  = 35, 37, and 40 nm, respectively.

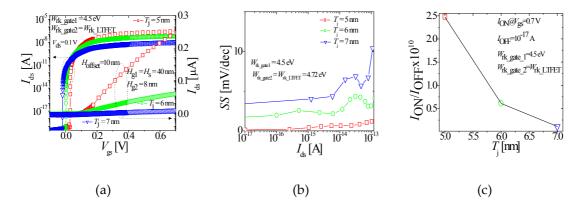

Next, to investigate the effect of  $T_j$  on device performance,  $I_{ds}$ - $V_{gs}$  characteristics, SS, and  $I_{ON}/I_{OFF}$  of DG-LTFET are presented for different  $T_j$  with fixed  $W_{rk\_gate1}$  = 4.5 eV and  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ ,  $H_{g1}$  =  $H_{nonoffset}$  = 40 nm,  $H_{offset}$  = 10 nm. and  $H_{g2}$  =  $H_{nonoffset}$  -  $H_{g1}$  + ( $H_{offset}$  -  $H_{g1}$ ) = 8 nm in Fig. 9(a), (b) and (c), respectively. It was found that the increasing  $T_j$  results in a degradation of  $I_{ON}/I_{OFF}$  ratio. It is simply because of the increase in BTBT path length with the increase in  $T_j$ .  $T_j$  of 5 nm was found to be optimum in this work as any further reduction will bring significant quantum confinement effect into play which is well known to degrade device performance [4-5], [13-15].

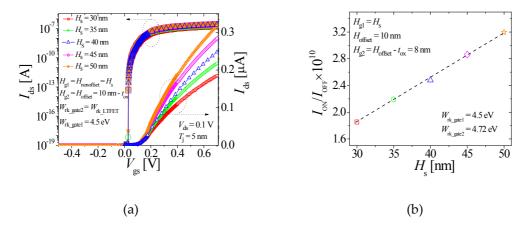

Next, the impact of varying  $H_s$  is investigated.  $I_{ds}$ - $V_{gs}$  characteristics of DG-LTFET for several  $H_s$  with fixed  $W_{rk\_gate1}$  = 4.5 eV and  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ ,  $H_{g1}$  =  $H_s$  =  $H_{nonoffset}$ ,  $H_{g2}$  =  $H_{nonoffset}$  -  $H_{g1}$  + ( $H_{offset}$  -  $H_{g1}$  + ( $H_{offset}$  -  $H_{g1}$  + ( $H_{offset}$  -  $H_{g1}$  + ( $H_{g1}$  =  $H_{g1}$  +  $H_{g2}$  =  $H_{g1}$  + ( $H_{g2}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g2}$  +  $H_{g1}$  + ( $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g1}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +  $H_{g1}$  +  $H_{g2}$  +  $H_{g1}$  +

**Figure 9.**  $I_{ds}$ - $V_{gs}$  characteristics of DG-LTFET with different  $T_j$  and fixed  $W_{rk\_gate1}$  = 4.5 eV,  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$  and  $H_{g1}$  =  $H_s$  =  $H_{nonoffset}$  = 40 nm,  $H_{g2}$  =  $H_{offset}$  (10 nm) -  $t_{ox}$  = 8 nm. (b) SS of  $I_{ds}$ - $V_{gs}$  shown in Fig. 8(a). (c)  $I_{ON}/I_{OFF}$  ratio of  $I_{ds}$ - $V_{gs}$  characteristics shown in Fig. 8(a). Red squares, green circles, and blue triangles:  $T_j$  = 5, 6 and 7 nm, respectively.

**Figure 10.**  $I_{ds-}V_{gs}$  characteristics of DG-LTFET with different  $H_s$ , fixed  $W_{rk\_gate1} = 4.5$  eV,  $W_{rk\_gate2} = W_{rk\_LTFET}$ , and  $H_{g1} = H_s = H_{nonoffset}$ ,  $H_{g2} = H_{offset}$  (= 10 nm) -  $t_{ox} = 8$  nm. (b)  $I_{ON}/I_{OFF}$  ratio of  $I_{ds-}V_{gs}$  characteristics shown in Fig. 10(a). Red squares, green circles, blue triangles, magenta diamonds, and orange stars:  $H_s = 30$ , 35, 40, 45, and 50 nm, respectively.

Finally, ambipolar current of DG-LTFET is discussed. Ambipolar Ids of TFET depends on

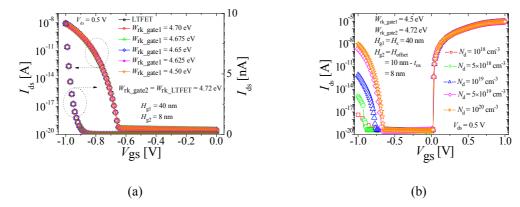

drain-channel junction. In DG-LTFET, drain-channel junction is controlled by gate2 with  $W_{rk\_gate2} = W_{rk\_LTFET}$ . With the same workfunction, the electrostatics of drain-channel junction in DG-LTFET is exactly the same as that in LTFET. Fig. 11(a) shows ambipolar  $I_{ds}$  of DG-LTFET compared with LTFET. Any change in  $W_{rk\_gate1}$  in DG-LTFET does not affect the drain-channel junction. Same argument applies for any other design parameter variation in DG-LTFET including  $H_s$ ,  $H_{g1/2}$ ,  $T_j$ , that is, as long as electrostatics of drain-channel junction remains unaffected, DG-LTFET will exhibit equivalent ambipolar  $I_{ds}$  as LTFET. Further, impact of  $N_d$  on ambipolar  $I_{ds}$  was considered. Different  $N_d$  values were considered for a DG-LTFET with  $W_{rk\_gate1} = 4.5$  eV and  $W_{rk\_gate2} = W_{rk\_LTFET}$ ,  $H_{g1} = H_{nonoffset} = 40$  nm,  $H_{g2} = H_{offset} - t_{ox} = 8$  nm, and  $T_j = 5$  nm and the results are shown in Fig. 11(b).

$H_{\text{nonoffset}} = 40 \text{ nm}$ ,  $H_{\text{g2}} = H_{\text{offset}} - t_{\text{ox}} = 8 \text{ nm}$ , and  $T_{\text{j}} = 5 \text{ nm}$  and the results are shown in Fig. 11(b). Drain doping level of  $10^{18} \text{ cm}^{-3}$  was found to suppress ambipolar  $I_{\text{ds}}$  appreciably without affecting the  $I_{\text{ON}}$ .

**Figure 11.** (a)  $I_{ds}$ - $V_{gs}$  characteristics of DG-LTFET at  $V_{ds}$  = 0.5 V with different  $W_{rk\_gate1}$  and  $W_{rk\_gate2}$  =  $W_{rk\_LTFET}$ ,  $H_{g1}$  =  $H_{offset}$  = 10 nm,  $H_{g2}$  = 8 nm,  $T_j$  = 5 nm and  $N_d$  = 10<sup>20</sup> cm<sup>-3</sup>. Red circles, green triangles, blue diamonds, magenta stars, and orange right triangles:  $W_{rk\_gate1}$  = 4.7, 4.675, 4.65, 4.625, and 4.5 eV. (b) DG-LTFET  $I_{ds}$  with different  $N_d$ .  $N_d$  = 10<sup>18</sup> cm<sup>-3</sup> demonstrates almost negligible ambipolar  $I_{ds}$ . Red squares, green circles, blue triangles, magenta diamonds, and orange stars:  $N_d$  = 10<sup>18</sup>, 5×10<sup>18</sup>, 10<sup>19</sup>, 5×10<sup>19</sup>, and 10<sup>20</sup> cm<sup>-3</sup>.

#### 5. Conclusions

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

Device physics of LTFET were investigated. It was found that a large part of subthreshold region is dominated by the parasitic, lateral, and 2D BTBT from source to Roffset with lower Gtun. The more efficient 1D BTBT from source to  $R_{\text{nonoffset}}$ , which has higher  $G_{\text{tun}}$ , takes place at a higher bias in the subthreshold region because of Vth\_Rnonoffset > Vth\_Roffset. The device does not utilize its channel fully during the subthreshold region due to  $V_{\text{th\_Rononfiset}} > V_{\text{th\_Roffset}}$ . A new type of device based on LTFET was introduced in this work. The device uses a dual gate-stacked structure which workfunction of upper gate W<sub>rk\_gate1</sub> is below that of lower gate W<sub>rk\_gate2</sub>. This makes the potential in R<sub>nonoffset</sub> increase and thus  $V_{\text{th\_Rnonoffset}}$  reduce. DG-LTFET reverses the threshold condition of LTFET, which it lowers  $V_{\text{th\_Rnonoffset}}$  (<  $V_{\text{th\_Roffset}}$ ).  $R_{\text{nonoffset}}$  with higher  $G_{\text{tun}}$  turns on earlier than  $R_{\text{offset}}$  in the subthreshold region of DG-LTFET and the device exhibits SS of less than 10 mV/dec. It was found that Wrk\_gate1 in DG-LTFET needs to be sufficiently less than W<sub>rk\_gate2</sub> to achieve the sub 10 mv/dec SS. It was found that  $I_{ds}$  and SS are independent of  $H_{g1/2}$ . DG-LTFET was further evaluated for different device dimensions including  $T_i$  and  $H_{s_r}$  while maintaining the electric field vector distribution equivalent.  $I_{ds}$  decreases with an increase in  $T_1$  and scales with  $H_s$ .  $N_d$  value of  $10^{18}$  cm<sup>-3</sup> was found to appreciably reduce ambipolar Ids. With the results presented in this work DG-LTFET could be considered as a viable potential replacement to conventional MOSFET.

**Author Contributions:** Conceptualization, N.F., and Y.S.Y.; methodology, N.F, and Y.S.Y.; investigation, N.F., and Y.S.Y.; data curation, N.F.; writing—original draft preparation, N.F.; writing—review and editing, N.F., and Y.S.Y.; supervision, Y.S.Y.; project administration, Y.S. Y.; funding acquisition, Y.S.Y.

**Funding:** This research was funded by Ministry of Trade, Industry & Energy (MOTIE), project number 10054888 and Korea Semiconductor Research Consortium (KSRC) support program for the development of future semiconductor devices.

Acknowledgments: This work was supported by IDEC (EDA tool).

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

#### 205 References

- 206 1. Avci, U. E.; Morris, D. H. Tunnel field-effect transistors. *IEEE J. Electron Devices Soc.* 2015, 3, 88-95, doi: 10.1109/JEDS.2015.2390591.

- 208 2. Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy efficient electronic switches. *Nature* **2011**, 479, 329-337, doi: 10.1038/nature10679.

- 3. Kim, S. W.; Kim, J. H.; Liu, T. K.; Choi, W. Y.; Park, B. Demonstration of L-shaped tunnel field-effect transistors. *IEEE Trans. Electron Devices* **2016**, 63, 1774-1778, doi: 10.1109/TED.2015.2472496.

- 4. Yang, Z. Tunnel field-effect transistor with an L-shaped gate. *IEEE Electron Device Lett.***2016**, 4, 839-842, doi: 10.1109/LED.2016.2574821.

- 5. Imenabadi, R. M.; Saremi, M.; Vandenberghe, W. G. A novel PNPN-like Z-shaped tunnel field-effect transistor with improved ambipolar behavior and RF performance. *IEEE. Trans. Electron Devices* **2017**, 64, 4752-4758, doi: 10.1109/TED.2017.2755507.

- 6. Kim, S. W.; Choi, W. Y.; Sun, M. C.; Park, B. G. Investigation on the corner effect of L-shaped tunneling field-effect transistors and their fabrication method. *J. Nanosci. Nanotechnol.* **2016**, 9, 6376-6381, doi: 10.1166/jnn.2013.7609.

- 7. Sentaurus User Manual, version L-2016.03, Mar. 2016.

- 8. Kao, K. H.; Verhulst, A. S.; Vandenberghe, W. G.; Soree, B.; Groeseneken, G.; Meyer, K. D. Direct and indirect band-to-band-tunneling in germanium-based TFETs. *IEEE Trans. Electron Devices* **2012**, 59, 292-301, doi: 10.1109/TED.2011.2175228.

- 9. Saxena, R. S.; Kumar, M. J. Dual-material gate technique for enhanced transconductance and breakdown voltage of trench power MOSFETs. *IEEE. Trans. Electron Devices* **2009**, 56, 517-522, doi: 10.1109/TED.2008.2011723.

- Long, W.; Ou, H.; Kuo, J-M.; Chin, K. K. Dual-material gate (DMG) Field Effect Transistor. *IEEE. Trans. Electron Devices* 1999, 46, 865-870, doi: 10.1109/16.760391.

- 229 11. Polishchuk, I.; Ranade, P.; King, T-J.; Hu, C. Dual work function metal gate CMOS technology using metal interdiffusion. . *IEEE Electron Device Lett.* 2001,9, 444-446, doi: 10.1109/55.944334.

- 231 12. Sze S.M.; Kwok, K. Ng. *Physics of Semiconductor Devices*, 3<sup>rd</sup> ed.; John Wiley & Sons: Hoboken, New Jersey, USA, 2006; ISBN: 9780471143239.

- 233 13. Walke, A. M.; Verhulst, A. S.; Vandooren, A.; Verreck, D.; Simeon, E.; Rao. V. R.; Groeseneken, G.; 234 Collaert, N.; Thean, A. V. Y. Part I: Impact of field-induced quantum confinement on subthreshold swing behavior of line TFETs. *IEEE Trans. Electron Devices* 2013, 60, 4057-4064, doi: 10.1109/TED.2013.2287259.

- 236 14. Padilla, J. L.; Gamiz, F.; Godoy, A. A simple approach to quantum confinement in tunneling field-effect transistors. *IEEE Electron Device Lett.* **2012**, 33, 1342-1344, doi: 10.1109/LED.2012.2207876.

- 238 15. Padilla, J. L.; Alper, C.; Gamiz, F.; Ionescu, A. M. Assessment of field-induced quantum confinement in heterogate germanium electron-hole bilayer tunnel-field transistor. *Applied Physics Letters* **2014**, 105, 082108-1 082108-4, doi.org/10.1063/1.4894088.