Article

# **Voltage Control for DC-DC Converters**

Usman Rahat 1, Abdul Basit 2 and Muhammad Salman 3,\*

- <sup>1</sup> U.S PCAS-E, UET Peshawar; engr.usmanrahat93@gmail.com

- <sup>2</sup> U.S PCAS-E, UET Peshawar; abdul.basit@uetpeshawar.edu.pk

- <sup>3</sup> U.S PCAS-E, UET Peshawar; 12ktele0236@uetpeshawar.edu.pk

- \* Correspondence: engr.usmanrahat93@gmail.com; Tel.: +92-313-9779334

**Abstract:** In this paper, we discuss voltage control method for buck converter operating in continuous conduction mode (CCM) using analog feedback system. The aim of this work is to control the output voltage of a buck converter during the variation in load current. This is obtained using analog feedback made with operational amplifier (Opamp). However, the same technique can be applied to other DC-DC converters (e.g boost, buck-boost, cuk converter, etc) in CCM mode, but for the purpose of analysis buck converter is chosen as an example.

**Keywords:** analog feedback, operational amplifier (Opamp), buck converter, continuous conduction mode.

#### 1. Introduction

The issue of voltage regulation cannot be neglected in power electronics circuits. The load requires a controlled and regulated output voltage to operate. However the non-linear and abrupt current drawing nature of the load causes the output voltage of the converter to deviate from the desired level. This could result in failure of the load operation. The main role of a power electronics circuit is to convert one form of electric power to the other form of electric power by changing either voltage, frequency or both. In DC-DC converters the level of voltage is either shifted up or down depending upon the application. In this work the output voltage of a buck converter is controlled. Buck converter converts its input voltage to a lower dc output level. This work is primarily focused on voltage control of DC-DC converter (buck converter as an example). The converter is basically non-linear and time variant in nature. The principles of state space averaging [1]–[6] and circuit averaging [1], [7], [8] can be applied to obtain linear time invariant (LTI) model. Moreover, this paper focuses the continuous conduction mode (CCM) operation. During CCM the inductor current is always positive and never drops to zero. In CCM mode the converter has two states. In general a DC-DC converter can operate in either continuous conduction mode (CCM) or discontinuous conduction mode (DCM).

## 2. Modeling and Simulation

Modeling is a way to represent a process or phenomenon in a mathematical form. This step can be as simple as setting up some linear equations to as complex as set of non linear differential equations. It is worth mentioning to point out that mathematical models are not exact but some kind of approximation to the real physical systems. The more accurate a model is the more mathematical rigor it has and thus more complex. Therefore, we often have to trade off between the level of accuracy we require from our models and the level of complexity we can handle. In fact, what we really tend to do is model the significant components and factors of the system and ignore all the unnecessary details. Moreover, it is better to start with simple model and analyze it, and later on if we find out that the model is inaccurate we can refine it again but in the meanwhile we get some good insights of the system.

2 of 7

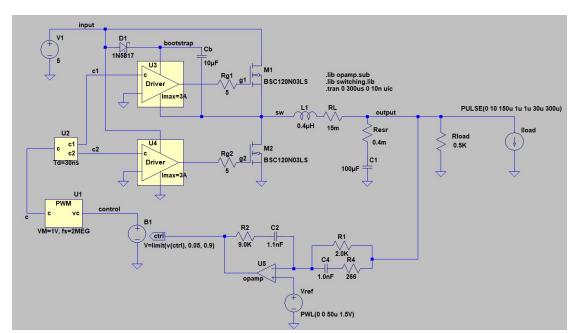

The simulation model is setup in LTspice where the buck converter along with its controller is simulated. The simulation model is explained in detail below:

#### 2.1. Load Current Variation

The simulation setup from LTspice in fig1 is discussed where the main objective is to regulate the output voltage irrespective of output load current. The pulse source is used to model the varying load.

The converter designed has considerably high end specifications which are hard to achieve. The details are given:

- Input Voltage *vg*=5V. The input voltage is 5V.

- Output Voltage *v*=1.5V. The objective is to regulate the output voltage at 1.5V.

- Output Current *iload* range= 0-10A. The output current can vary between 0 and 10A.

- Power Stage Switching Frequency=2MHz.

- Bandwidth of the feedback loop/Crossover Frequency = 200KHz, implies Settling Time = 5us.

- Phase Margin (P.M) =50 degrees

**Figure 1.** Simulation for Load Variation

The PWM block can generate a duty cycle value ranging [Dmin = 0.05- Dmax = 0.9]. Some important blocks of the simulation model are:

### • Gate Drivers (U3 and U4)

The gate driver block switch on/off the MOSFETs in complimentary fashion.

#### • Pulse Width Modular (U1)

The PWM block generates the switching signal proportional to its input signal.

#### • Dead Time (U2)

The dead time block does not allow both MOSFETs to conduct at the same time.

## • Feedback Circuit

This block has operational amplifier with resistors and capacitors making up the proportional

3 of 7

integral derivative (PID) controller.

#### • Sources

Input Voltage Source = 5V Output Current Pulse Source = 0-10A

| Sr.No. | Component      | Value                        |

|--------|----------------|------------------------------|

| 1.     | PWM (U1)       | Dmin = 0.05; Dmax = 0.9      |

| 2.     | Dead Time (U2) | 30ns                         |

| 3.     | Opamp (U5)     | Aol = 100meg; GBW = 10000meg |

Table 1. Important Blocks in Simulation Setup

#### 2.2. Load Current Simulation Overview

In fig1, for setting the reference level a soft start switching technique is realized. The voltage at reference node increases in a linear fashion from 0 to 1.5V in 50us. The 1.5V is not applied upfront as initially the output voltage will be zero. This will produce high error signal pushing the opamp to its limits to achieve the low error state. In doing so the feedback system may damage the power MOSFETs.

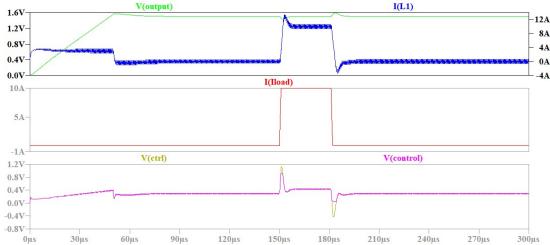

Figure 2. Load Variation Overview

- 1) The fig2 shows the output voltage follows a reference value Vref in a linear fashion and the gets stable when reaches to steady state condition.

- 2) At 150us there is a step change in the output load current and it jumps from 0 to 10A. The value of output current pulse source remains high for 30us and then at 180us there is another step change but this time from 10 to 0A. It is important to observe that the output voltage in such an enormous step change of load current remains close to 1.5V with good accuracy.

- 3) During the rising edge of load current, the inductor current rises, output voltage dips and stabilizes. While during the falling edge of load current, the inductor current drops, output voltage overshoots and stabilizes.

4) It is important to note that when the load current takes a positive step, there is an output voltage dip. The deviation in the output voltage from its reference value is used as an error signal to drive the opamp. Similarly, during the negative step, the output voltage overshoots the reference value and the error is used to drive the opamp.

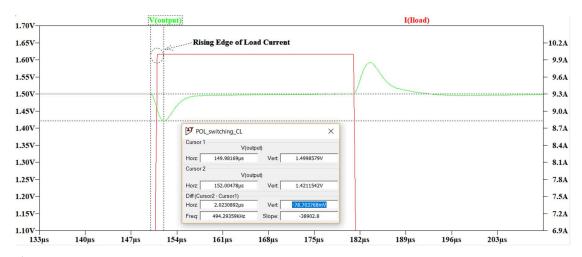

## 2.3. Rising Edge of Load Current and Output Voltage

As mentioned that during the positive step of load current from 0 to 10A, there is a voltage dip in the output voltage. This is verified in fig3 through LTspice where the voltage dip of -78mV is shown. It should be noted that the control signal in fig2 gets saturated for some time, otherwise the dip would have been further lower than -78mV.

Figure 3. Load Current Rising Edge

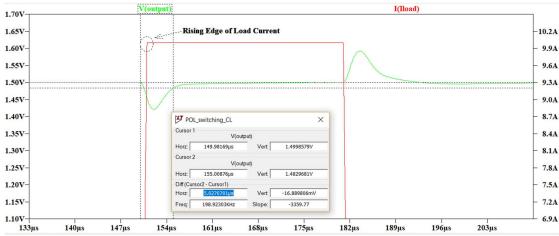

# 2.4. Settling Time on Rising Edge

The lower voltage difference of the output voltage from the reference (1.5V in this case) is not the only desired behavior of a good feedback controller. The feedback loop should also have sufficient bandwidth to quickly respond to the variations. The higher the bandwidth of the feedback loop, the lesser the time it would take to reach its steady state condition of reference voltage. In fig4 this is verified that the output voltage with good precision gets very close to 1.5V in the time span of 5us which is the settling time of the feedback loop.

Figure 4. Settling Time on Rising Edge

| Sr.No | Parameter             | Value        |

|-------|-----------------------|--------------|

| 1.    | Total Simulation Time | 300us        |

| 2.    | $V_{ref}$             | 1.5V         |

| 3.    | Pulse Current Source  | Range: 0-10A |

Table 2. Some Simulation Parameters

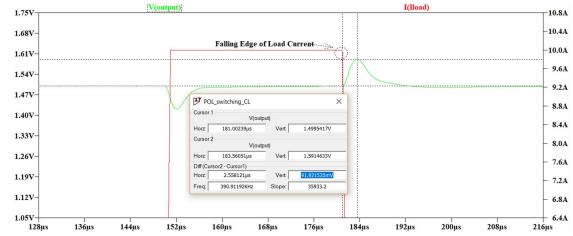

# 2.5. Falling Edge of Load Current and Output Voltage

As mentioned that during the negative step of load current from 10 to 0A, there is a voltage overshoot in the output voltage. This is verified in fig5 through LTspice where the voltage overshoot of 91.92mV is shown. It should be noted that the control signal in fig2 gets saturated for longer time, otherwise the dip would have been further lower than 91.92mV.

Figure 5. Load Current Falling Edge

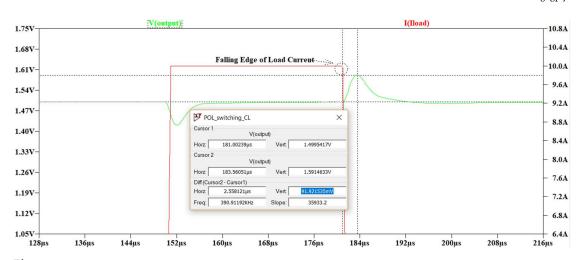

# 2.6. Settling Time on Falling Edge

The same arguments hold true in this case for the settling time which we can see in fig6. There is a considerable deviation found in the output voltage after 5us of the settling time. This is because the control signal in fig2 gets saturated for a longer period of time in the case of falling edge.

Figure 6. Settling Time on Falling Edge

#### 4. Discussion and Future Work

In this paper the techniques of linear control theory involving circuit averaging are used. However, many other state of the art and advanced techniques can be applied in the future to solve other issues. These issues include the output voltage deviation in the presence of input voltage deviation or parameters change. In this paper only the output voltage deviation caused by the load current variation is considered. While in reality the voltage deviation due to non regulated input voltage can be crucial to handle. Furthermore, the circuit parameters can change because of temperature variations which could cause the impedance values of the elements to deviate causing the output voltage to deviate dramatically. In this work analog feedback control is used, while digital control can be implemented whose main advantage could be to change the circuit behavior later on according to new requirements. This will reduce the bulk production cost of the system. However, the down side of this approach is that it would cause additional delay due to analog to digital conversion of the signal.

#### 5. Conclusions

In this paper a simulation model was setup in LTspice to regulate the output voltage of the buck converter to 1.5V in the presence of disturbances in the output load current. It was seen that the output current was varied in step change of 10A. The output current was a pulse source which was used to trigger a positive edge of 0 to 10A, and negative edge of 10 to 0A at the load side. In both the cases the output voltage was well regulated near 1.5V. The control signal was saturated for negligible time because the load current variation was very abrupt and fast, due to which the controller faced some issues to meet the exact settling time requirements.

**Author Contributions:** Conceptualization, U.R..; Methodology, U.R.; Software, U.R.; Validation, M.S. and U.R.; Investigation, A.B and M.S.; Resources, M.S.; Data Curation, A.B and M.S.; Writing-Original Draft Preparation, U.R.; Writing-Review & Editing, A.B and M.S.; Visualization, U.R.; Supervision, A.B.; Project Administration, A.B.

Funding: This research received no external funding.

Conflicts of Interest: The authors declare no conflict of interest.

## References

R. W. Erickson and D. Maksimovic, Fundamentals of power electronics. Springer Science & Business Media, 2007.

7 of 7

- 2. R. Middlebrook and S. Cuk, "A general unified approach to modeling switching-converter power stages," in *Power Electronics Specialists Conference*, 1976 IEEE. IEEE, 1976, pp. 18–34.

- 3. J. Mahdavi, A. Emaadi, M. Bellar, and M. Ehsani, "Analysis of power electronic converters using the generalized state-space averaging approach," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 44, no. 8, pp. 767–770, 1997.

- 4. R. Middlebrook, "Small-signal modeling of pulse-width modulated switched-mode power converters," *Proceedings of the IEEE*, vol. 76, no. 4, pp. 343–354, 1988.

- W. Polivka, P. Chetty, and R. Middlebrook, "State-space average modelling of converters with parasitics and storage-time modulation," in *Power Electronics Specialists Conference*, 1980. PESC. IEEE. IEEE, 1980, pp. 119–143.

- R. Erickson, "Dc-dc power converters department of electrical and computer engineering university of colorado boulder, co 80309-0425," Article in Wiley Encyclopedia of Electrical and Electronics Engineering, 1999.

- 7. E. Van Dijk, J. Spruijt, D. M. O'sullivan, and J. B. Klaassens, "Pwmswitch modeling of dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 10, no. 6, pp. 659–665, 1995.

- 8. A. Ayachit, A. Reatti, and M. K. Kazimierczuk, "Small-signal modeling of pwm dual-sepic dc-dc converter by circuit averaging technique," in *Industrial Electronics Society, IECON 2016-42nd Annual Conference of the IEEE*. IEEE, 2016, pp. 3606–3611.