l Article

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

33

34

35

36

37

38

39

40

41

42

43

44

45

## 2 Small Scale Modular Multilevel Converter for Multi

# 3 Terminal DC Networks Applications: System Control

## 4 Validation

- 5 Elie Talon Louokdom <sup>1</sup>, Serge Gavin <sup>2</sup>, Daniel Siemaszko <sup>3</sup>, Frédéric Biya-Motto <sup>1</sup>, Bernard

- 6 Essimbi Zobo 1, Mario Marchesoni 4 and Mauro Carpita 2,\*

- Laboratory of Electronics, Department of Physics, Faculty of Science, University of Yaoundé I,

P.O. Box 812, Yaoundé, Cameroon, talonelie@gmail.com, biyamotto@yahoo.fr, bessimb@yahoo.fr.

- 9 <sup>2</sup> Département des Technologies Industrielles (TIN), Haute école spécialisée de Suisse occidentale (HES-SO),

10 University of Applied Sciences of Western Switzerland, Route de Cheseaux 1, 1401 Yverdon-les-Bains,

11 Switzerland, mauro.carpita@heig-vd.ch

- 12 <sup>3</sup> Power Electronics and Systems Consultancy, Rue de Lyon 27 CH-1201, Geneva, Switzerland, daniel.siemaszko@pesc.ch

- Department of Electrical, Electronic, Telecommunications Engineering and Naval Architecture, University of Genova, Via all'Opera Pia 11A, 16145 Genova, Italy, marchesoni@unige.it

- \* Correspondence: mauro.carpita@heig-vd.ch

Abstract: This paper presents the design and implementation of a digital control system for modular multilevel converters (MMC) and its use in a 5-kW small scale prototype. To achieve higher system control reliability and multi-functionality, the proposed architecture has been built with an effective split of the control tasks between a master controller and six slave controllers, one for each of the six arms of the converter. The MMC prototype have been used for testing both converter and system level controls in a reduced scale laboratory set up of a Multi-Terminal DC transmission network (MTDC). The whole control has been tested in order to validate the proposed control strategies. The tests performed at system level allowed to explore the advantages of using an MMC in a MTDC system.

**Keywords:** Digital controller; digital signal processors (DSP); modular multilevel converters (MMC), multi-terminal DC network (MTDC)

#### 30 1. Introduction

UE to the energy challenges the world is facing nowadays, the interest in the integration into the utility grids of renewable energy sources has significantly increased in recent years. In this context, high voltage direct current (HVDC) systems are considered as one of the best options to achieve high reliability in future long distance offshore grids that are needed to interconnect offshore wind farms, loads and large-scale storage facilities [1].

Among the different power converter topologies proposed in the literature on high voltage direct current (HVDC) applications, Modular Multilevel Converters (MMC) [2] have emerged in recent years due to their attractive properties such as low harmonic distortion, scalability and flexibility. The use of MMC for HVDC systems has been largely studied by the scientific community and some commercials products have been developed by constructors such as ABB, Siemens and Alstom [3,4].

HVDC systems using MMC installed last decade are mostly point-to-point systems [5-7]. However, the needs to strengthen the existing AC transmission grids and to balance the intermittent power of offshore wind farms over a wider area by interconnecting multiple neighboring HVDC systems have increased the interest on Multi-terminal HVDC systems (MTDC) [8]. The use of MMC

2 of 18

in MTDC systems instead of conventional two-level voltage source converters (VSC) has the already cited advantages to be redundant and scalable, to reduce or eliminate bulky harmonics filters on the AC side and to avoid DC link capacitors banks. Despite these advantages, many technical challenges have to be tackled to allow their large scale use. Among these challenges, the lack of a standardized grid code for interconnecting adjacent HVDC systems [9], the DC faults protections management [9,10], the experimental validation of system control strategies to ensure power flow and DC voltage control [11,12] can be cited.

Concerning this last issue, MMC-based MTDC system control can be splitted among a high-level (or system level) control and a low-level (or converter level) control. In order to test and verify these control levels under realistic conditions, as well as their interactions, it is really useful to develop small scale laboratory prototypes, able to handle the various operational modes. Some small scales prototypes have been proposed in the scientific literature since the introduction of MMC. For instance, a prototype of MMC is built in [13], with 44 submodules (SM) per arm, each SM capacitor with a nominal voltage at 10 V. In [13], a 20kW back-to-back MMC-based system with 3 SM per arm is presented, while [15] presents a 25kW six-level MMC prototype. In [16], a hybrid small scale prototype is proposed for Alternate Arm Converter (AAC) and MMC.

Considering all these previous studies, it is obvious that, given the large number of submodules used to form the whole structure of a MMC [6], the complex command and control schemes require efficient architectures. This can only be implemented by digital control techniques, making use of advanced FPGA (Field Programmable Gate Array) or DSP (Digital Signal Processors) for fast calculation and accurate timing of the switching signals of the multiple power semiconductors. An FPGA-based control of an MMC has been proposed in [17], making use of a lookup table for the generation of the output references. This approach is not well suited for closed loop control of both the external and internal dynamic behavior of the MMC. It's quite obvious that a single microcontroller will have difficulties in effectively performing the complex control schemes and the communication with external peripherals. Most of previous works [18-22] propose a combination of DSP and FPGA boards to handle the control and communication. In [21], the combination of both processors (DSP and FPGA) is used as a central supervision unit. The DSP performs the analog to digital conversion and all the high-level control tasks, while the FPGA manages the modulation, the capacitor voltage balancing and the communication with the submodules tasks. This allow to achieve the advantage of a central modulator, that generates all naturally synchronized PWM signals for all switches. However, the capacitor voltage balancing in an MMC usually uses a sorting algorithm which is in itself a sequential process, not leading to an efficient use of parallel logical resources. Distributed controller architecture can meet these challenges. A distributed architecture fits very well with the scalability of the converter's structure and the computational load is shared between several microprocessors. Nevertheless, a distributed architecture of the controller requires an effective synchronization of all arm controllers to ensure that the gate signals of all submodules are synchronous. A robust and fast communication link between the master controller and arm controllers must also be assured.

In this paper, a small scale MMC prototype with a controller architecture designed with only DSPs is presented. The master controller uses a dual core processor which combines a C2000 Texas Instruments (TI) MCU for real time control tasks and an Arm Cortex-M3 processor for the communication purposes. This master controller interacts with six slave controllers, one for each arm, implemented with another C2000 Texas Instruments MCU. This MMC prototype is used in a reduced scale laboratory setup of a MTDC [23] to implement both system level and converter level controls, and to study MMC interactions with other VSC in an existing MTDC system.

The novelty of the paper concern the usefulness of the proposed MMC control structure, answering to the challenge of experimental validation of system control strategies to ensure power flow and DC voltage control in MTDC systems.

The paper is organized as follows: Section 2 presents the topology of MMC and a brief review of its control and MTDC control strategies. Section 3 describes the controller structure, the task partitioning as well as the communication protocols. The actual implementation and the

experimental validation of the proposed architecture are presented in section 4. A discussion on how this architecture may be practically extended to be used in MMC systems utilizing more submodules is done in Section 5. Finally, conclusion is given in Section 6.

#### 2. Structure of MMC and control strategies

#### 2.1. Structure

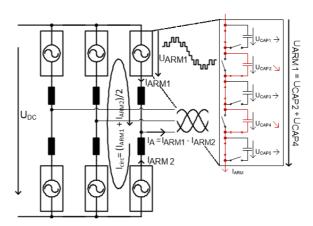

Even though the MMC converter is well known in the power electronics community, it's worthwhile here to briefly summarize its main characteristics [1]. Figure 1 presents the typical structure of an MMC. It consists of six arms, working as voltage sources. Each arm is made of N power submodules. A submodule consists of a storage capacitor and a half or full bridge converter. The bridge is used to insert or bypass the capacitor. The three-phase AC voltages and the total arm voltage are respectively composed of 2N+1 and N+1 levels per signal cycle, corresponding to different insertions or removal of capacitors. This minimizes voltage harmonic distortions and consequently allows to reduce/eliminate the filter on the AC side. Furthermore, a large and bulky capacitor on the DC side is no longer necessary. The modularity of the converter allows the use of power semiconductors with reduced voltage to achieve high AC and DC voltages.

Figure 1. Structure of the Modular Multilevel Converter.

#### 2.2. Converter level control

MMCs need controllers fulfilling several purposes: the control of external voltages and/or currents loops, the control of internal current loops and the control and balancing of the capacitor voltages [4].

#### 2.2.1. Modulation strategies of MMC

Many modulation techniques have been proposed in the literature [4, 24-28]. In this paper, phase shifted carrier pulse width modulation (PS-PWM) has been chosen, given the low number of submodules used in the prototype [24]. For a full-scale application with an increasing number of modules, other modulation schemes should be preferred, e.g. the Nearest Level Control [29].

#### 2.2.2. Output current and energy stored control

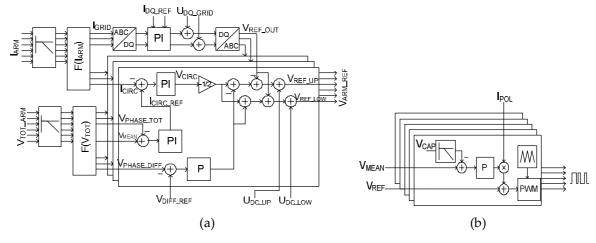

The output currents control in the MMC is similar to control used in conventional 2-level VSC. For the internal control of MMC, two approaches can be used: Non-energy based approach, where the output DC current is uncontrolled [30] and Energy-based control, where the energy stored in converter is controlled making use of the circulating currents [31], which are an intrinsic feature of the MMC converters. In this paper, an Energy-based control, already presented by the authors in [32], has been used to decouple the capacitors voltages from the DC bus. Figure 2(a) illustrates its working principle.

## 2.2.3. Capacitor voltage balancing

The sub-modules voltages balancing is implemented to prevent the divergence of capacitors voltages which would eventually result on the collapse of the whole system. Many researches have dealt with SM voltages balancing [24-25]. The strategy retained in this paper is based on what was presented in [32]. Figure 2(b) summarizes this balancing strategy, with obvious meaning of all the signals involved. In principle, each sub-module capacitor voltage is measured and compared with the mean value of all arm capacitor voltage. The difference resulting from this comparison, with a sign given by the arm current direction, is used by a proportional controller to provide a correction value which is added to the set point voltage given to the sub-module PWM generation.

Figure 2. (a) MMC control strategy diagram.; (b) Submodules capacitors voltage balancing strategy [32]

#### 2.3. MTDC control strategies

The control of a MTDC system focused on DC line voltage control and the control of the power exchange among HVDC stations. Several control strategies have been proposed in the literature. These include voltage margin control, voltage droop control, dead-band voltage droop control and non-dead band voltage control [33].

The voltage margin control method is an extension of the point-to-point HVDC transmission systems control. One of the terminals (also called master terminal or "slack-bus") controls the DC voltage and the other terminals (slaves terminals) can arbitrarily (or on the basis of available resources) inject or draw power. Controlling the MTDC network voltage at a single terminal has the drawbacks that the master converter is the only one to participate in the regulation of the DC voltage. It is therefore necessary that the AC network associated with the master converter can absorb or provide all the power variations necessary for the balance of the MTDC system, in particular in case of a fault. Moreover, the single terminal used as balanced terminal must be sized to cope with all power variations situations. This result in a weakness of the whole system since if the master converter is lost, the MTDC system will be no longer regulated and collapses [9].

In the voltage droop control method, the DC voltage variation is used as a common signal by all converters that adjust their power based on this DC voltage. Thus, the task of controlling the DC voltage is shared among all the converters. In order to stabilize the MTDC system, a dead zone can be added to the droop control setting, also called dead-band voltage droop control. This allows discriminating between normal and disturbed operation of the MTDC system. However, the control activity of the converters within the band (normal operation) is fully lost. This has the disadvantage that some of the droop control parameters are set to zero and infinity, which gives any degree of freedom for optimization [34]. In the non-dead band voltage droop control, the dead zone is replaced by a real power-voltage characteristic slightly inclined. So, different droop constants can be used, depending on the deviation between DC voltage set-point and measure. Several control

5 of 18

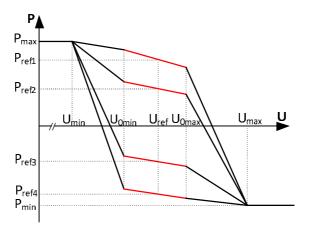

characteristics of a non-dead band voltage control scheme are shown in Figure 3: a reference voltage and power is set for each converter, and the balancing of the system occurs by increasing the DC voltage in case of excess of power, while decreasing it otherwise. The slopes of the different sections of the characteristic are chosen according to the connected loads or sources (e.g. wind generators cannot usually provide large amounts of additional power). This method is effective to ensure stable operation of the DC network, also in case of a failure of one or even several converters.

Figure 3.. Power-voltage control characteristics of a non-dead band voltage control [33].

#### 3. MMC control system design

## 3.1. Overall controller operation

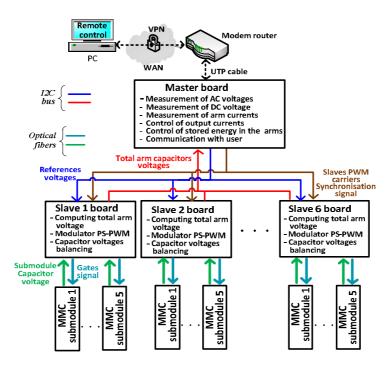

The MMC controller architecture is presented in Figure 4. A distributed controller architecture has been chosen, given the computational limitations of a centralized controller [35].

Figure. 4. Signals flows between controllers and power submodules

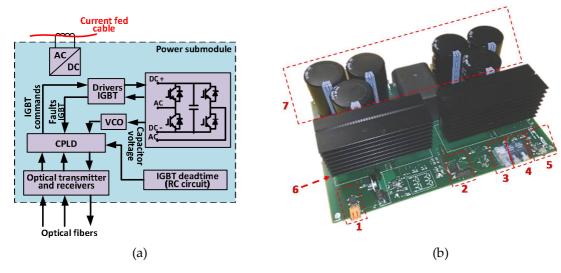

**Figure 5**. Power submodule. (a) Schematic, (b) Module Hardware: (1) Power supply, (2) CPLD, (3) Optical transmitter, (4) Optical receiver, (5) VCO, (6) IGBT et radiators, (7) submodule capacitors.

Table 1. Main power submodule devices

| Main devices            | References               |

|-------------------------|--------------------------|

| CPLD                    | XILINX XC9536XL-10VQG44C |

| VCO                     | AD654JRZ                 |

| IGBT                    | IXBH16N170               |

| Optical transmitter     | AVAGO HFBR-1522Z         |

| Optical receiver        | AVAGO HFBR-2522Z         |

| IGBT gate driver        | ST TD350E                |

| Electrolytic capacitors | ESMH451VND102MB63T       |

| Film Capacitor          | MKP1848C63012JY5         |

All control and communication tasks are distributed between the "master" controller and the arms "slave" controllers. The master controller manages the real and reactive power flow, and the communications tasks with the external world. The master controller communicates to the six slave controllers the voltage references, the arm current signs, the synchronization signal of the arm controllers and other commands such as start driving submodules. Each slave controller sends back periodically to the master the total arm voltage and performs the balancing of its arm capacitor voltages using the arm current sign received from master.

#### 3.2. Power submodules

The power submodules are driven by the slave controller through optical fibers. To prevent faults and generate the dead-times, the signals are pretreated by a programmable logic device (CPLD) before being sent to the gates. The capacitor voltages are measured using a voltage-controlled oscillator (VCO) which converts the capacitor voltage into a variable frequency signal. It is then sent to the corresponding arm controller through an optical fiber link. In this application, for a capacitor voltage range between 1 and 250 V, the VCO frequency varies linearly from 3 to 450 kHz. Each module has DC bus connectors and AC output connectors (middle points of H-bridge arms). Two PWM input signals are available to control the two IGBT legs. A 3.2mF capacitor is connected between the DC bus for local power storage. In this paper, two IGBTs only (half-bridge operation) are mounted in the power module, requiring just one PWM input. The nominal ratings of the module are 10 A and 200 V, with some 1 kV isolation voltage. The low power supply for the sub-module is provided by a medium frequency current fed system, consisting of an isolated power supply and a cable passing through thirty small torus from the secondary of each torus, one for each sub-module [36]. An inverter fed a nominal current of 5 A in the cable at 45 kHz. Figure 5 presents the sub-module

schematic and its hardware implementation. Table 1 give some specifications of the main power submodules devices.

#### 217 3.3. Slave controllers

The main tasks of the slave controllers consist in receiving each capacitor voltage, performing capacitor voltage balancing and generating command signals for each submodule. The slave controllers communicate with the master board using inter-integrated circuit bus (I2C), and with submodules using optical fibers. This ensure the insulation requirements between the control board and the power boards. The advantages of I2C bus are the reduced number of wires and the quite simple implementation in a multi-slave environment. The I2C fast mode has been chosen with a clock frequency of 350 kHz. Each arm controller is implemented using a TMS320F28335 TI C2000 DSP family. The frequency sent by the power submodule for the capacitor voltage measurement is measured by the enhanced capture (eCAP) peripheral of the DSP and then converted into voltage.

#### 227 3.4. Master controller

The master controller board is designed using a TI Concerto DSP F28M35x. The main tasks of the master board are the communication with the user or host, the digital conversion of measurements, the energy flow control, the start and stop tasks and the communication with the slave boards.

## 232 3.4.1. User communication

The master communicates with operator through a User Interface (UI). It interacts with the M3 core of the master board using Ethernet protocol allowing, for instance, the converter to be compliant with IEC61850. Information such as real power, reactive power, nominal current, start and stop command are send to the master by the user through the UI. This feature allows commanding the converter remotely in a Wide Area Network (WAN).

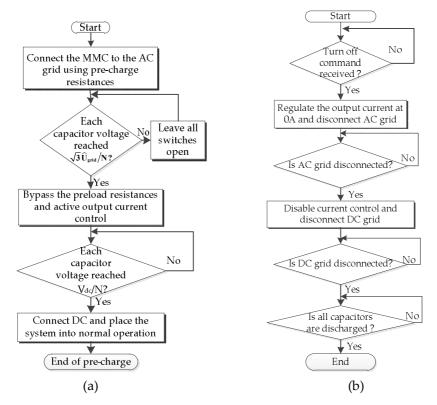

#### 3.4.2. Start and stop tasks

Once the master controller receives start command from UI, switches connect the converter to the grid through pre-charge resistors. Flowcharts of the pre-charge and the shutdown of the MMC are presented in Figure 6.

#### 3.4.3. Currents and voltages measurements and energy flow control.

ADC operations are performed by the C2000 core. Afterwards, PLL based grid synchronization, AC current PI controllers and energy balancing are executed. The master controller is then able to send the six voltage references to each individual arm controller. To increase the bandwidth of the communication between master and slaves, the switching frequency has been chosen as one half of the sampling frequency. The arm voltage references are then updated every half period of the switching frequency, see details next section.

#### 3.4.4. Communication and synchronization with slave boards.

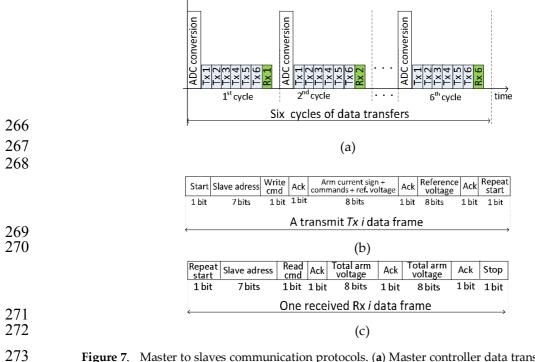

Figure 7(a) shows the master controller data transfer process to the slaves in six sampling periods. Figure 7(b) and 7(c) show the communication protocol developed to meet the data transfer needs. The voltage references are coded with 12 bits.

The four remaining bits are used to send the corresponding arm current sign and other commands to each slave such as the commands to start and stop the driving of submodules. All sending and receiving operations are performed within one sampling period. This protocol ensures that the voltage references and arm current sign, which are key information for the control, are updated and sent to slaves every sampling cycle. After three switching periods, the master has received the six arm voltages. This reception delay, caused by the low speed of I2C, is not so critical

260

261

262

263264

265

274

275

8 of 18

for the control since the capacitor voltage balancing is performed by the arm controllers. Moreover, the total arm capacitor voltages do not change significantly during this time. This delay has been taken into account in the controller design.

Figure 6. Flowchart of the pre-charge and turn off strategy. (a) Pre-charge, (b) Turn off

**Figure 7**. Master to slaves communication protocols. (a) Master controller data transfer with slaves per ADC cycle of conversion. Tx i = transmit to slave i; Rx i = receipt from slave I, (b) data protocol used when sending messages to each slave, (c) data protocol used to receive message from each slave.

A distributed architecture of the controller requires an effective synchronization of all arm controllers, to ensure that the gates signals of all submodules are synchronized. To manage this issue, a dedicated synchronization signal is used as event trigger to adjust the phase of the first PWM on each of the six slave controllers. The other carriers of the same slave controller are referenced to the first carrier.

#### 3.5. Protections functions

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

Protection functions are included at various levels of the control system. The master controller redundantly checks for possible failures by analyzing the measurements received from ADC module. If a failure is detected, it sends the appropriate command to slave controllers to stop the submodules. The master also checks if a slave controller fails to communicate. In that case, it will also send the suitable command to the other slave boards to stop the whole converter. Submodule protections concerning power section faults, overvoltage and undervoltage are directly performed by the slave controllers. Their thresholds values are included in the capacitor's voltage balancing scheme. If a noncritical failure occurs on a submodule, slave controller sends the appropriate command to bypass the faulty submodule. If the occurred failure is critical for the safe operation of the converter, the slave controller sends the appropriate command to the master and stops the entire arm. The last protection layer is performed by the CPLD on the submodule board. The CPLD uses a logic to protect the semiconductors in case of improper commands or incompatible capacitor voltage.

#### 4. Experimental validation

The proposed architecture has been implemented on a 5-kW reduced scale MMC demonstrator. Figure 5(b) shows the power board, Figure 8(a) and (b) show the slave and master boards, and Figure 8(c) show the whole MMC demonstrator. The main system parameters are shown in Table 2. Tests have been carried out with MMC working as inverter on a three-phase passive load with a DC link of 800 V and in a reduced scale laboratory setup of a MTDC transmission network [23,37].

The experimental validation of the control architecture and the overall functionality of the MMC includes several aspects. The communication between the master board and an UI, the data flow between the master and slave boards together with the synchronization of the generated PWM signals, the operation of the modules driven by the slave boards have been tested.

(c)

305

Figure 8 Circuits boards and converter: (a) arm (slave) controller, (b) master controller, (c) whole converter reduced scale prototype.

306

307

308

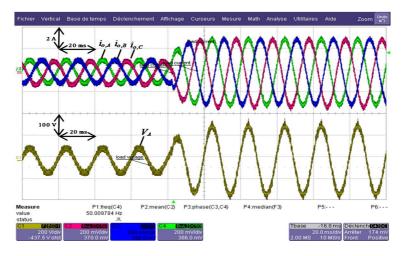

The current and voltage waveforms as seen from the AC side, the MMC output current and energy stored control and the power flow control in a MTDC network have been tested too.

## **Table 2.** Experimental setup

| Symbol        | Quantity                                | Value  |  |

|---------------|-----------------------------------------|--------|--|

| $U_{ m grid}$ | RMS grid AC voltage                     | 230 V  |  |

| $I_{nom}$     | RMS nominal current                     | 7 A    |  |

| $U_{DC}$      | DC voltage                              | 800 V  |  |

| L             | Arm inductance                          | 6 mH   |  |

| $f_s$         | Switching frequency                     | 1 kHz  |  |

| $f_{ m ech}$  | Sampling frequency                      | 2 kHz  |  |

| $f_{ m grid}$ | Grid frequency                          | 50 Hz  |  |

| С             | Submodule capacitor                     | 3.3 mF |  |

| Vc            | Submodule nominal voltage 160 V         |        |  |

| N             | Number of submodule per arm 5           |        |  |

| Rload         | AC passive load resistance $100 \Omega$ |        |  |

| $L_{load}$    | AC load Inductance 3 mH                 |        |  |

#### 4.1. Communications tests

To check the communication between master board and the UI, a hypertext transfer protocol (HTTP) has been used, allowing the master board to host a web page.

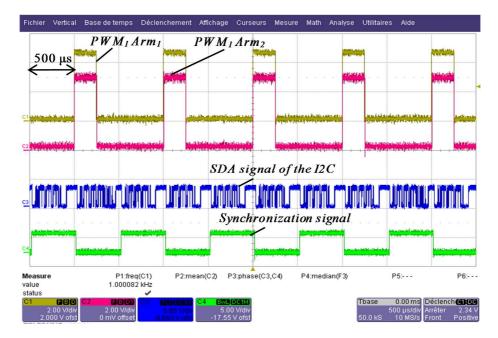

The correct flow of data between master board and slave boards has been tested, checking the information timing on the serial data line (SDA) and serial clock line (SCL) of the I2C bus. Figure 9 shows communication signals in compliance with the protocol presented in Figure 7(a). The communication between master and slaves is effectively performed at each sampling period (half of the switching period). Data transfer duration between boards at each sampling cycle is about 400  $\mu s$ , i.e. 80% of the period. The synchronization of PWM signals between two slave boards is also highlighted in Figure 9.

**Figure 9.** Signals on the converter: PWM 1 signals of two arms controllers (duty cycle 25%), Serial data (SDA) line of the I2C (blue trace) and arms' synchronization signal (green trace).

#### **4.**2. *MMC control*

#### 4.2.1. Pre-charge test

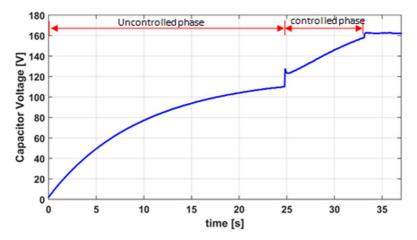

The pre-charge is performed directly from the AC side without using any external power supply, in accordance with the flowchart presented in Figure 6(a) and to the fact that the module's control is supplied independently of the capacitor voltage. The transient behavior of the voltage of a single SM capacitor during the pre-charge is presented in Figure 10. During the uncontrolled phase, this evolution corresponds to the exponential charge waveform of a capacitor as expected. Bypassing the pre-charging resistors creates a voltage jump of approximately 15 V, due to the direct connection of the MMC to the AC network. The evolution of the voltage of each capacitor during the second phase is approximately linear, thanks to the output current controller that limits the current withdrawn from the AC side. With the chosen parameters, the entire pre-charge takes less than one minute.

Figure 10. Evolution over time of a submodule capacitor voltage during pre-charge

## 4.2.2. Capacitor voltage balancing test

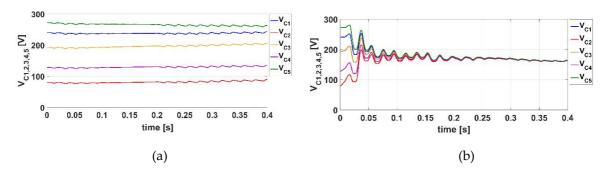

During this test, the capacitor voltage balancing algorithm has simply been disabled and enabled for short periods to evaluate its impact on the operation of the MMC. This test has been performed with the DC bus at 150 V to prevent any accidental capacitors failures. In order to better illustrate the dynamics of the balancing strategy at nominal voltage, some simulations were performed where all capacitor voltages were unbalanced with a large spread. Their initial values are:  $V_{C1} = 240 \text{ V}$ ,  $V_{C2} = 80 \text{ V}$ ,  $V_{C3} = 192 \text{ V}$ ,  $V_{C4} = 128 \text{ V}$  and  $V_{C5} = 272 \text{ V}$ .

Figure 11 presents the evolution over time of the capacitor voltages on the same arm in the two situations. It can be observed in Figure 11(a) that, when the algorithm is disabled, the SM capacitors voltages will not converge to their average value. Figure 11(b) shows that, when the balancing algorithm is activated, after about 0.2 s, all SM capacitor voltages converge to their average value. This result confirms the effectiveness of the SM capacitor balancing algorithm presented in § 2.2.3.

**Figure 11**. Capacitor balancing test on the MMC, (a) With the balancing algorithm disabled, (b) With the balancing algorithm enabled.

### 4.2.3. Output current and energy stored control tests

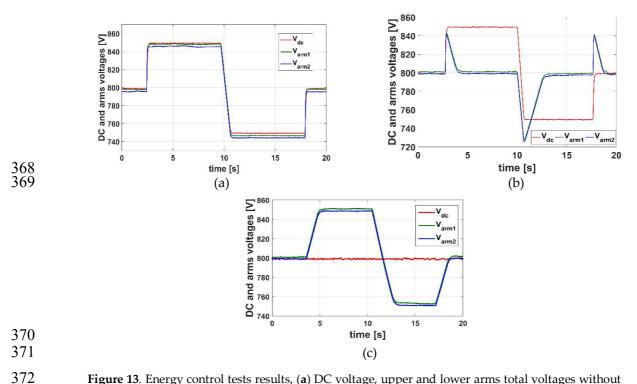

The output current controller has been tested with the MMC working as an inverter, supplied by a DC voltage of 800 V and injecting power into the AC utility grid. Figure 12 presents the dynamics of the controller during a change of the reference of the output current from 1 A to 3 A. The new reference value is reached in less than half a period of the output current denoting thereby a good dynamic of the regulator. The control of the energy stored in the converter is performed as presented in § 2.2.2. Figure 13 presents the control of total arms voltages. In Figure 13(a), the total arm voltages are not controlled. When the DC voltage changes, the total voltages of the upper and lower arms follow the DC voltage.

Figure 12. Output current control: output currents and output voltage of the phase A

**Figure 13.** Energy control tests results, (a) DC voltage, upper and lower arms total voltages without an energy control, (b) DC voltage, upper and lower arms total voltages with an energy control and step change in the DC voltage, (c) DC voltage, upper and lower arms total voltages with an energy control and step change of total arm voltages.

Hence the DC voltage is not decoupled from capacitors voltages. If a short time brake occurs in the DC bus, this will directly affect the capacitor voltages. In Figure 13(b) and 13(c), the energy control is enabled. In Figure 13(b), the total arm voltages are controlled at 800V and the DC voltage steps successively from 800V to 850 V, from 850 V to 750 V and from 750V to 800V. After a short transient phase, the total arm voltages remain at their reference value. In Figure 13(c), the DC voltage is held at 800 V and the total arm voltages are set to step successively from 800V to 850 V, from 850 V to 750 V and from 750V to 800V. The energy control allows a decoupling between capacitor voltages and the DC bus voltage. The dynamics of the total arm voltage control loop has been intentionally reduced to avoid overvoltage on the capacitors.

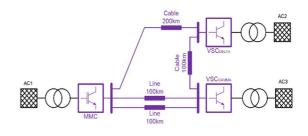

## 4.3. Power flow control in a MTDC network

The MMC has been implemented in a reduced scale laboratory setup to test system level control algorithms. Figure 14 shows the MTDC mock-up previously developed and described in [1]. The laboratory set-up presented in Figure 14 (b) simulates the following imaginary situation: Three converters, namely VSCDELTA, VSCGAMMA, and the MMC, simulate an MTDC connection between three different AC grids. This could be the case as an example of the connection between Italy, Sardinia and Corsica, actually made with thyristors technology. All converters are implemented with independent controllers to test the stability of the DC grid. A non-dead band voltage control [37] has been implemented on VSCDELTA and VSCGAMMA converters while the MMC controls the power injected in the AC grid. Several tests have been performed in order to verify the functionalities of the MMC when connected to a MTDC transmission network.

|           | Real scale | Reduced scale mockup |

|-----------|------------|----------------------|

| Voltage   | 400 kV     | 400 V                |

| Current   | 3,5 kA     | 3,5 A                |

| Impedance | 1 Ω        | 1 Ω                  |

| Power     | 1 GW       | 1 kW                 |

399 (a)

**Figure 14**. MTDC mockup, (a) MTDC mockup on laboratory, (b) Single line diagram of the laboratory setup.

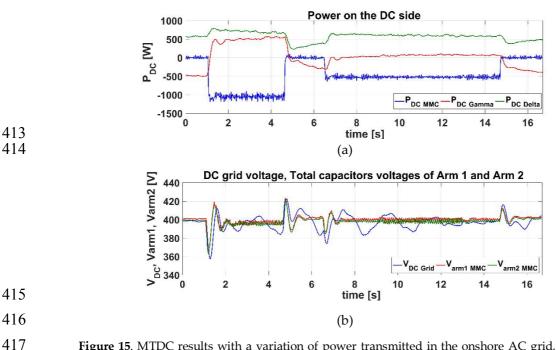

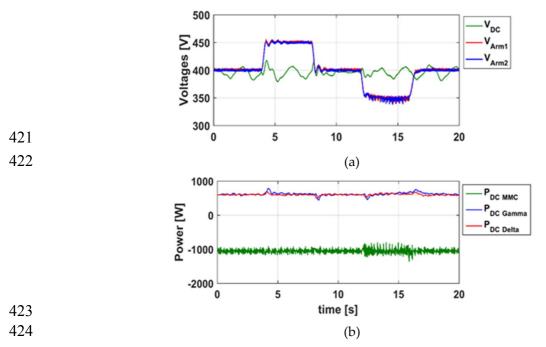

In a first test, different power profiles have been imposed on the AC side and corresponding powers are absorbed by the MMC on the DC side, as illustrated in Figure 15(a). On the DC side, the stability of the DC network is secured, showing the effectiveness of the non-dead band voltage control. On the MMC side, the energy control allows to maintain a stable voltage in the converter's sub-modules, decoupling them from the DC-link voltage variations as illustrated in Figure 15 (b).

A second test was performed in order to observe the whole MTDC system behavior when the SM of the MMC are used to store and restore energy in the system. The power transmitted between the DC and the AC1 grid remains constant. The DC link and two arms of the MMC voltages variations voltages are shown in Figure 16(a), and the power variations on the three VSC are shown in Figure 16(b). It can be seen in Figure 16 that the DC bus is not affected by these energy variations on the MMC and that the transients due to these charges and discharges are well absorbed.

14 of 18

**Figure 15**. MTDC results with a variation of power transmitted in the onshore AC grid, (a) Power variations in the experimental set-up with controlled MMC and two inverters implemented with non-dead band voltage control, (b) DC voltage variation and two arms of the MMC voltages during power flow

**Figure 16**. MTDC results when the stored energy in the MMC varies, **(a)** DC voltage variation and two arms of the MMC voltages, **(b)** Power variations in the experimental set-up with controlled MMC and two inverters implemented with non-dead band voltage control.

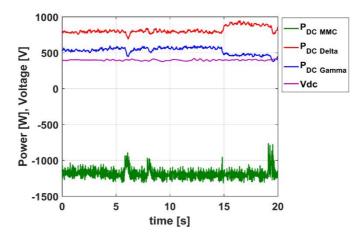

A third test was run to test the MTDC system with all VSC implementing the non-dead band droop control. Figure 17 presents the DC link voltage and power variation over the three converters when slight power variations are provoked. It can be seen on Figure 17 that the DC bus is well controlled and the transients are well absorbed by the three converters when the whole system is facing power variations. This third scenario also highlights the contribution of each converter to the stability of the DC bus.

Those results confirm the correct behavior of the MMC in a MTDC system and against power variation.

### 5. Discussion and further improvements

Concerning the controller architecture presented in this paper, the goal was to propose a light architecture with well-known DSP that could be quickly built and that could successfully be implemented in a small-scale prototype to test the control strategies developed. One critical point of this control structure is its scalability in case of a higher number of modules. Due to its decentralized architecture, in principle it is suitable for a higher number of SM in each arm, because all the operations assigned to the master controller and the communication between the master and the slave controllers do not depend on the number of SM to control. The local management of each arm is performed by an independent controller sending the reference set-points to all PWM modulators. However, the DSP used has twelve independent PWM outputs, so a maximum number of 12 modules can be controlled, without acting on the slave hardware.

Figure 17. MTDC results when all VSC implement Non-dead band droop control

For more modules, the slave controller could be combined, or even replaced by a low-cost FPGA that would produce as many PWM outputs as required. In case of combination of the slave DSP and an FPGA, the capacitor balancing and sorting algorithms which are sequential operations remain the task of the DSP. These aspects are under development and will not be discussed further in this paper.

The proposed hardware structure will be used for a lower demanding application in terms of voltage rating, i.e. a medium voltage application like a MV-Statcom or MV-SOP (Soft Open Point). In this case, the number of modules to be managed is about 20-24, which is feasible with the proposed multi-DSP approach.

Another critical point is the robustness of the I2C bus. It appeared a few times during tests in a highly EM perturbed environment that the I2C bus was perturbed when the bus was not shielded enough. However, all the EMC problems in the prototype have been solved with suitable shielding and accurate state-machine and communication tuning to avoid critical situations, like the switching of the main contactors.

#### 6. Conclusion

This paper presents the design and the implementation of a small scale modular multilevel converter. The proposed MMC prototype has been used to test both converter and system level controls in a reduced scale MMC-based MTDC network. Several MMC control levels have been tested and the results obtained validated the control strategies implemented and the controller architecture designed. The tests performed at system level have enabled to explore the advantages of using an MMC-based MTDC system. Among these, the capability of the MMC to store and restore the energy

- in the system, its scalability which allow the extend the DC link voltage as desired or to improve the AC side voltage harmonics contents.

- 471

- 472 Author Contributions: Conceptualization, Elie Talon Louokdom, Serge Gavin, Daniel Siemazsko and Mauro

- 473 Carpita; Formal analysis, all authors Funding acquisition, Mauro Carpita; Software, Elie Talon Louokdom, Serge

- Gavin and Daniel Siemazsko; Supervision, Mauro Carpita; Validation, all authors; Writing original draft, Elie

- Talon Louokdom; Writing review & editing, Elie Talon Louokdom and Mauro Carpita.

- 476

- 477 Acknowledgments: The authors acknowledge EOS-Holding (CH) for the funding of the research presented in

- 478 this paper. This research is part of the activities of the Swiss Centre for Competence in Energy Research on the

- Future Swiss Electrical Infrastructure (SCCER-FURIES), which is financially supported by the Swiss Innovation

- 480 Agency (Innosuisse-SCCER program). The authors would like to thank P. Favre-Perrod, D. Leu, H. Parisod

- 481 (HES-SO), J. Braun (CERN) for their contributions and useful suggestions.

- 482 **Conflicts of Interest:** The authors declare no conflict of interest.

- 483 References

- Siemaszko, D.; Carpita, M.; Favre-Perrod, P. Conception of a Modular Multilevel Converter in a Multi-Terminal DC/AC transmission network. In Proceedings of the Power Electronics and Applications (EPE'15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015.

- 487 DOI: 10.1109/EPE.2015.7309452

- 488 2. Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of IEEE Bologna Power Tech Conference, Bologna, Italy, 23-26 June 2003. DOI: 10.1109/PTC.2003.1304403

- 3. Sharifabadi, K.; Harnefors, L.; Nee, H.P.; Norrga, S.; Teodorescu, R. *Design, Control, and Application of Modular Multilevel Converters for HVDC Transmission Systems.* Wiley-IEEE Press, 2016.

- 493 4. Perez, M. A.; Bernet, S.; Rodriguez, J.; Kouro, S.; Lizana, R. Circuit topologies, modelling, control schemes and applications of modular multilevel converters. *IEEE Trans. Power Electron.*, **2015**, vol.30 no. 1, pp. 4–17. DOI: 10.1109/TPEL.2014.2310127

- 496 5. Dorn, J.; Gambach, H.; Strauss, J.; Westerweller, T.; Alligan, J. Transbay cable-A breakthrough of VSC multilevel converters in HVDC transmission. In Proceedings of CIGRE San Francisco Colloquium, San Francisco; 2012.

- 499 6. Francos, P. L.; Verdugo, S.; Alvarez, H. F.; Guyomarch, S.; Loncle, J. INELFE Europe's first integrated

500 onshore HVDC interconnection. In Proceedings of IEEE Power and Energy Society General Meeting, San

501 Diego, CA, USA, 22-26 July 2012.

- 502 7. Hussennether, V.; Rittiger, J.; Barth, A.; Worthington, D.; Rapetti, D.G.M.; Huhnerbein, B.; Siebert, M. Project borwin2 and helwin1-large scale multilevel voltage sources converter technology for bundling of offshore windpower. In Proceedings of CIGRE, Paris, France, 26-31 August 2012.

- 505 8. Ahmed, N.; Haider, A.; Van Hertem, D.; Zhang, L.; Nee, H. P. Prospects and challenges of future HVDC SuperGrids with modular multilevel converters. In Proceedings of 14th European Conference on Power Electronics and Applications, Birmingham, United Kingdom, 30 August 01 September 2011.

- 508 9. Van Hertem, D.; Ghandhari, M. Multi-terminal VSC HVDC for the European supergrid: Obstacles. *Renew. Sustain. Energy Rev.* **2010**, vol.14, no. 9, pp 3156-3163.

- 510 DOI.org/10.1016/j.rser.2010.07.068

- 511 10. Bucher, M.K.; Franck, C.M. Fault Current Interruption in Multiterminal HVDC Networks. *IEEE Trans. Power Del.*, **2015**, vol. 31, no. 1, pp. 87-95.

- 513 DOI: 10.1109/TPWRD.2015.2448761

- 514 11. Egea-Alvarez, A.; Bianchi, F.; Junyent-Ferre, A.; Gross, G.; Gomis-Bellmunt, O. Voltage Control of Multiterminal VSC-HVDC Transmission Systems for Offshore Wind Power Plants: Design and Implementation in a Scaled Platform. *IEEE Trans. Ind. Electron.*, **2013**, vol. 60, no. 6, pp. 2381-2391.

- 517 12. Aragüés-Peñalba, M.; Egea-Àlvarez, A.; Galceran Arellano, S.; Gomis-Bellmunt, O. Droop control for loss minimization in HVDC multi-terminal transmission systems for large offshore wind farms. *Electr. Power* 519 Syst. Res., **2014**, vol. 112, pp. 48-55

- 520 13. Zhou, Y.; Jiang, D.; Hu, P.; Guo, J.; Liang, Y.; Lin, Z. A prototype of modular multilevel converters. *IEEE Trans. Power Electron.*, **2014**, vol. 29, no. 7, pp. 3267–3278.

- 522 14. Binbin, L.; Dandan, X.; Dianguo, X.; Rongfeng, Y. Prototype design and experimental verification of modular multilevel converter based back-to-back system. In Proceedings International Symposium on Industrial Electronics, Istanbul, Turkey, 1-4 June 2014, pp. 626–630

- 525 15. Moranchel, M.; Sanchez, F.M.; Bueno, E.J.; Rodriguez, F.J.; Sanz, I. Six-level modular multilevel converter prototype with centralized hardware platform controller. In Proceedings of IECON 2015, Yokohama, Japan, 9-12 November 2015, pp. 863–868.

- 528 16. Jasim, O.F.; Moreno, F.J.; Trainer, D.R.; Feldman, R.; Farr, E.M.; Claree, J.C. Hybrid experimental setup for alternate arm converter and modular multilevel converter. In Proceedings of the 13th IET international conference on AC and DC Power Transmission, Manchester, UK, 14-16 Feb. 2017, pp. 1-6.

- 531 17. Islam, M.R.; Guo, Y.; Zhu, J. FPGA-based control of modular multilevel converters: Modeling and experimental evaluation In Proceedings of the International Conference on Electrical & Electronic Engineering (ICEEE), Rajshahi, 4-6 November 2015, pp. 89-92.

- 534 18. Atalik, T.; Deniz, M.; Koc, E.; Gercek, C.; Gultekin, B.; Ermis, M.; Cadirc, I. Multi-DSP and -FPGA based fully-digital control system for cascaded multilevel converters used in FACTS. *IEEE Trans. Ind. Informat.*, **2012**, vol. 8, no. 3, pp. 511–527.

- Liu, W.; Jayakar, R.; Song, W.; Huang, A.Q. A modular digital controller architecture for multinode high power converter applications. In Proceedings of the 31th Annual Conference of IEEE Industrial Electronics

Society (IECON), Raleigh, NC, USA 6-10 November 2005, pp. 715–720

DOI: 10.1109/IECON.2005.1568992

- 541 20. Francis, G. A synchronous distributed digital control architecture for high power converters. M.S. dissertation, Virginia Polytechnic Inst. State Univ., Blacksburg, VA, Mar. 2004.

- 543 21. Lago, J.; Sousa, G.J.M.; Heldwein, M.L. Digital control/modulation platform for a modular multilevel converter system. In Proceedings of COBEP, Gramado, Brazil, 2013, pp. 271-277

- 545 22. McGrath, B.P.; Holmes, D.G.; Kong, W.Y. A decentralized controller architecture for a cascaded H-bridge multilevel converter. *IEEE Trans. Ind. Electron.*, **2014**, vol. 61, no. 3, pp. 1169-1178.

- 547 23. Luginbühl, M.; Pidancier, T.; Favre-Perrod, P. Transmission d'énergie par réseaux à courant continu multiterminaux. *Bulletin AES/Electrosuisse*, **2014**.

- 549 24. Hagiwara, M.; Akagi, H. Control and experiment of pulse widthmodulated modular multilevel converters. *IEEE Trans. Power Electron.*, **2009**, vol. 24, no. 7, pp. 1737–1746.

- 551 25. Siemaszko, D. Fast Sorting Method for Balancing Capacitor Voltages in Modular Multilevel Converters. 552 *IEEE Trans. Power Electron.*, **2015**, vol.30, no.1, pp. 463-470.

- 553 26. Ängquist, L.; Antonopoulos, A.; Siemaszko, D.; Ilves, K.; Vasiladiotis, M.; Nee, H.P. Open-loop control of modular multilevel converters using estimation of stored energy. *IEEE Trans. Ind. Appl.*, **2011**, vol. 47, no. 6, pp. 2516–2524.

- 556 27. Edpuganti, A.; Rathore, A.K. Optimal Pulsewidth Modulation of Medium-Voltage Modular Multilevel Converter. *IEEE Trans. Ind. Appl.*, **2016**, vol. 52, no. 4, pp. 3435-3442.

- 558 28. Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.M. The age of multilevel converters arrives. *IEEE Trans. Ind. Electron. Magazine*, **2008**, vol. 2, no. 2, pp. 28–39.

- 560 29. Kouro, S.; Bernal, R.; Miranda, H.; Silva, C.A.; Rodriguez, J. High-Performance Torque and Flux Control for Multilevel Inverter Fed Induction Motors. *IEEE Trans. Power Electron.*, **2007**, vol. 22, n. 6,

- 562 30. Tu, Q.; Xu, Z.; Zhang, J. Circulating current suppressing controller in modular multilevel converter. In Proceedings of 36th Annual Conference on IEEE Industrial Electronics Society (IECON), Glendale, AZ, USA, 7-10 November 2010, pages 3198–3202.

- 565 31. Delarue, P.; Gruson, F.; Guillaud, X. Energetic macroscopic representation and inversion based control of a modular multilevel converter. In Proceedings 15th European Conference on Power Electronics and Applications (EPE'13 ECCE Europe), Lille, France, 3-5 September 2013, pages 1–10.

- 32. Siemaszko, D.; Talon Louokdom, E.; Parisod, H.; Braun, J.; Gavin, S.; Eggenschwiler, L.; Favre-Perrod, P.;

569 Carpita, M. Implementation and experimental set-up of a Modular Multilevel Converter in a Multi

570 Terminal DC/AC transmission network. In Proceedings of 18th European Conference on Power Electronics

571 and Applications (EPE'16 ECCE Europe), Karlsruhe, Germany, 5-9 September 2016, pp. 1-12.

- 572 33. Luginbühl, M.; Lalou, M.J. Contrôle coordonné des convertisseurs de réseaux MTDC. *Bulletin AES/Electrosuisse*, **2013**.

583

584

585

586587

18 of 18

- 574 34. Vrana, T.K.; Zeni, L.; Fosso, O.B. Active power control with undead-band voltage & frequency droop for HVDC converters in large meshed DC grids. In Proceedings of EWEA Conference, Copenhagen, Denmark, Apr. 2012.

- 577 35. Talon, E.L.; Gavin, S.; Siemaszko, D.; Biya-Motto, F.; Essimbi, B.Z.; Carpita, M. Design and implementation of a multi-dsp based digital control system architecture for modular multilevel converters. In Proceedings of IEEE-PEMC, Varna, Bulgaria, 2016, pp. 1182-1187.

- Wen, H.; Xiao, W.; Lu, Z. Current-Fed High-Frequency AC Distributed Power System for Medium–High-Voltage Gate Driving Applications. *IEEE Trans. Ind. Electron.*, **2013**, vol. 60, no. 9, pp. 3736-3751.

- 37. Talon Louokdom, E.; Siemaszko, D.; Gavin, S.; Leu, D.; Favre-Perrod, P.; Carpita, M. Use of Modular Multilevel Converter in multi-terminal DC transmission network: Reduced scale set-up and experimental results. In Proceedings of 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw, Poland, 11-14 September 2017, pp. P.1-P.9