1 Article

## 2 A Single-Stage Asymmetrical Half-Bridge Flyback

# Converter with Resonant Operation

- 4 Chung-Yi Ting <sup>2</sup>, Yi-Chieh Hsu <sup>2</sup>, Jing-Yuan Lin <sup>1,\*</sup> and Chung-Ping Chen <sup>2</sup>

- 5 Department of Electronic and Computer Engineering, National Taiwan University of Science and Technology, Taiwan, ROC; jylin@mail.ntust.edu.tw (J.L.)

- Graduate Institute of Electronics Engineering, National Taiwan University; d01943002@ntu.edu.tw (C.T.); d02943003@ntu.edu.tw (Y.H.); cpchen@ntu.edu.tw (C.C.)

- \* Correspondence: jylin@mail.ntust.edu.tw (J.L.); Tel.: x-886-2-27376419

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Abstract: This paper proposes a single-stage asymmetrical half-bridge fly-back (AHBF) converter with resonant mode using dual-mode control. The presented converter has an integrated boost converter and asymmetrical half-bridge fly-back converter and operates in resonant mode. The boost-cell always operates in discontinuous conduction mode (DCM) to achieve high power factor. The presented converter operates simultaneously using a variable-frequency-controller (VFC) and pulse-width-modulation (PWM) controller. Unlike the conventional single-stage design, the intermediate bus voltage of this controller can be regulated depending on the main power switch duty ratio. The asymmetrical half-bridge fly-back converter utilizes a variable switching frequency controller to achieve the output voltage regulation. The asymmetrical half-bridge fly-back converter can achieve zero-voltage-switching (ZVS) operation and significantly reduce the switching losses. Detailed analysis and design of this single-stage asymmetrical half-bridge fly-back converter with resonant mode is described. A wide AC input voltage ranging from 90 to  $264 \, V_{rms}$  and output  $19 \, \text{V} / 120 \, \text{W}$  prototype converter was built to verify the theoretical analysis and performance of the presented converter.

**Keywords:** fly-back converter; zero-voltage-switching (ZVS); Variable-frequency-controller (VFC); single-stage

1. Introduction

A conventional power supply was designed with a two-stage scheme that can be divided into two parts. The first stage achieves power-factor-correction (PFC) to reduce the input current harmonics. The second stage is a DC/DC converter that regulates the output voltage. However, the two-stage scheme has several defects, such as high cost and power supply system complexity. In recent years, a single-stage scheme was proposed [1-5] that integrates a boost stage and a DC/DC stage to share a common switch. The boost-cell stage operates in discontinuous conduction mode (DCM) to provide high power factor while the DC/DC stage can be responsible for output voltage regulation. Unfortunately, the single-stage scheme presents major problems in which the intermediate bus voltage cannot be regulated, such as the BIFRED converter, single-stage fly-back converter and single-stage LLC resonant converter [6-10]. When voltage is input for universal applications, the intermediate bus voltage could be as high as 1000 V, causing difficulty in selecting converter components, with voltage stress issues throughout the capacitors and switches. The wide intermediate bus voltage variation will cause output voltage regulation design difficulty and also cause lower conversion efficiency though the DC/DC stage. The single-stage scheme intermediate bus voltage cannot be regulated at light loads and universal input voltage. The zero-voltage-switching (ZVS) fly-back converters have been used widely in industry and are suitable for low-to-medium power applications, such as LED-driver and desktop computer power supplies. Various kinds of ZVS schemes have been proposed, such as the active-clamp network and asymmetrical half-bridge circuit [11,12]. The active-clamp fly-back converter [13] employs the active clamp network to achieve ZVS operation; however, the voltage stresses on the switches are greater than input voltage which will cause high conduction losses in the power switches. The asymmetrical half-bridge fly-back converter (AHBF) with resonant mode [14-17] was developed to achieve ZVS and reduce the voltage stresses on the switches to less than that of the active-clamp fly-back converter, so the power density and conversion efficiency can be effectively increased. Furthermore, it can operate under changed duty cycles or variable switching frequencies for regulated output voltage.

This paper proposes a new single-stage asymmetrical half-bridge fly-back converter with resonant mode. The proposed converter integrates a boost converter and an asymmetrical half-bridge fly-back converter with resonant mode using dual-mode control. The converter intermediate bus voltage can be regulated by the pulse-width-modulation control (PWM). The variable-frequency-controller (VFC) can regulate the converter output voltage. Therefore, this proposed converter can operate in universal input voltage and solves the voltage stress issues throughout the capacitors and switches. The proposed converter utilizes the ZVS technique to decrease the switching losses, resulting in high conversion efficiency. The operational principle for the proposed converter is analyzed, a prototype converter with AC input voltage of 90-264 V<sub>rms</sub> and output voltage/current of 19 V/8 A is built to verify the analytical results.

### 2. Circuit Description and Principle Operation of Proposed Converter

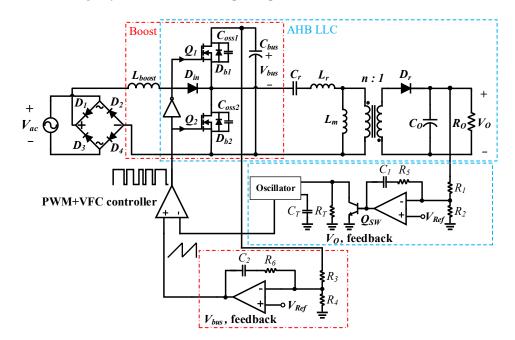

Figure 1 shows the circuit configuration for the single-stage asymmetrical half-bridge fly-back converter with resonant mode. The primary switches  $Q_1$  and  $Q_2$  operate at asymmetrical duty ratio.  $D_{b1}$  and  $D_{b2}$  are the anti-paralleled power MOSFETs. The primary side diode  $D_{in}$  is a braking diode. The  $L_{boost}$  is a boost-cell inductor. The resonant inductor  $L_r$ , resonant capacitor  $C_r$  and magnetizing inductor  $L_m$  for are the resonant tank for the asymmetrical half-bridge fly-back converter. The secondary diode  $D_r$  is a rectifier diode, the  $C_{bus}$  is boost cell output capacitor and  $C_O$  is the asymmetrical half-bridge fly-back converter output capacitor.

**Figure 1.** Schematic of the proposed single-stage asymmetrical half-bridge fly-back converter with resonant

- The following assumptions were made to analyze the proposed single-stage asymmetrical half-bridge fly-back converter.

- 78 The conduction losses of all switches, diodes and layout traces, and the copper losses of the transformer are neglected.

- 80 The turn ratio of the transformer windings is  $n = N_1/N_2$ .

- 81 The resonant inductor  $L_r$  is composed of a leakage inductor and external inductor, where

- $L_r = L_{eakage} + L_{ex}.$

89

90

91

92

93

94

96

97

98

99

- 83 The conduction times for  $Q_1$  are  $(1-D)T_s$  and  $Q_2$  is  $DT_s$ , respectively, where D is the duty cycle for  $Q_2$ , and  $T_s$  denotes the switching period. In addition, the dead time is much smaller than that other of conduction times.

- 86 In the steady state the bus capacitance  $C_{bus}$  and output capacitance  $C_0$  are large enough so that the bus voltage  $V_{bus}$  and output voltage  $V_0$  are a constant value.

- Both the boost-cell stage and asymmetrical half-bridge fly-back converter stage share the common switches  $Q_1$  and  $Q_2$ , and furthermore there is bus capacitor  $C_{bus}$  between the two stages. The boost-cell stage was presented in [18]. When the switch  $Q_2$  is turned on and the switch  $Q_1$  is turned off, this results in a positive voltage  $V_{Lboost} = V_{IN}$  across the inductor  $L_{boost}$  causing a linear increase in the inductor current  $i_{Lboost}$ . Conversely, when the switch  $Q_1$  is turned on and the switch  $Q_2$  is turned off, the inductor  $L_{boost}$  is releases energy to the bus capacitor  $C_{bus}$ . Therefore, from the flux-balance of  $L_{boost}$  under the steady-state,  $V_{bus}$  can be determined as

95

$$\frac{V_{bus}}{V_{IN}} = \frac{1}{2} + \frac{\sqrt{1 + 2 \cdot \frac{D^2 \cdot R_{L,bus}}{L \cdot f_s}}}{2}$$

(1)

In the DC/DC stage, when the switch  $Q_1$  is turned on, the intermediate bus voltage  $V_{bus}$  will charge  $C_r$ ,  $L_r$  and  $L_m$ . Conversely, when the switch  $Q_2$  is turned on, the secondary diode  $D_r$  conducts and  $L_m$  is releases energy to the output load. When the asymmetrical half-bridge fly-back converter operates in resonant mode, the voltage transfer ratio can be expressed as

$$100 M = \frac{nV_O}{V_{bus}} = \frac{(1-D) \cdot \frac{1-\cos\left[\omega_r \cdot \left(\frac{D}{f_s}\right)\right]}{Z_r \cdot \omega_r}}{\frac{1-D}{\omega_r} \left[\frac{1}{n^2 R_o} + \frac{D}{2L_m f_s}\right] \cdot \sin\left[\omega_r \cdot \left(\frac{D}{f_s}\right)\right] + \frac{(1-D)^2}{n^2 R_o f_s} + \frac{1-\cos\left[\omega_r \cdot \left(\frac{D}{f_s}\right)\right]}{Z_r \cdot \omega_r}}$$

(2)

101 Where

$$\omega_r = \frac{1}{\sqrt{C_r \cdot L_r}} \tag{3}$$

$$Z_r = \sqrt{\frac{L_r}{C_r}} \tag{4}$$

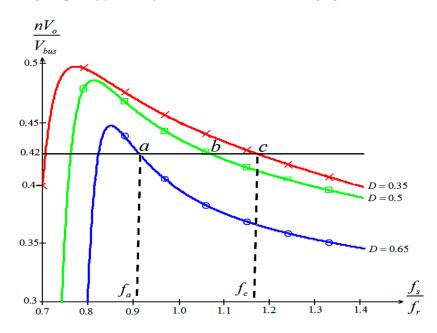

From equation (2), the voltage transfer ratio of the asymmetrical half-bridge fly-back converter includes relation between the duty ratio D and switching frequency  $f_s$  simultaneously. Figure 2 shows the relation between the duty ratio D, switching frequency  $f_s$  and voltage transfer ratio. It shows that when the duty-ratio D is decreased from 0.35 to 0.65, to maintain fixed voltage gain, the switching frequency can shift from  $f_c$  to  $f_a$  correspondingly. However, Figure 2 also shows that when the switching frequency  $f_s$  or duty ratio D decreases the voltage gain will be increased. In contrast, when the switching frequency  $f_s$  or duty ratio D increase, the voltage gain will be decreased.

Figure 2. Voltage transfer ratio versus normalized switching frequency.

From Figure 1,  $Q_2$  is the boost-cell stage main switch, therefore the intermediate bus voltage  $V_{bus}$  is regulated by the D to  $Q_2$  duty ratio. Unfortunately, changing the D to  $Q_2$  duty ratio will affect the asymmetrical half-bridge fly-back converter output voltage. For example, when the D to  $Q_2$  duty ratio is increased, the asymmetrical half-bridge fly-back converter output voltage will decrease. Conversely, when the D to  $Q_2$  duty ratio is decreased, the asymmetrical half-bridge fly-back converter output voltage will increase. To overcome the change in D to  $Q_2$  duty ratio causing unstable asymmetrical half-bridge fly-back converter output voltage, a VFC has been added to the feedback control loop. When the asymmetrical half-bridge fly-back converter output voltage is decreased, the switching frequency  $f_s$  will decrease to provide larger voltage gain for regulated output voltage. Conversely, when the output voltage is increased, the switching frequency  $f_s$  will be increased to provide lower voltage gain. According to the above analysis, the intermediate bus voltage  $V_{bus}$  and output voltage  $V_O$  of the proposed converter can be regulated simultaneously from the PWM control and VFC.

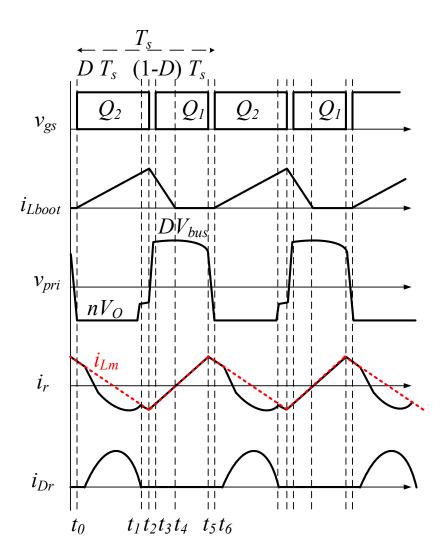

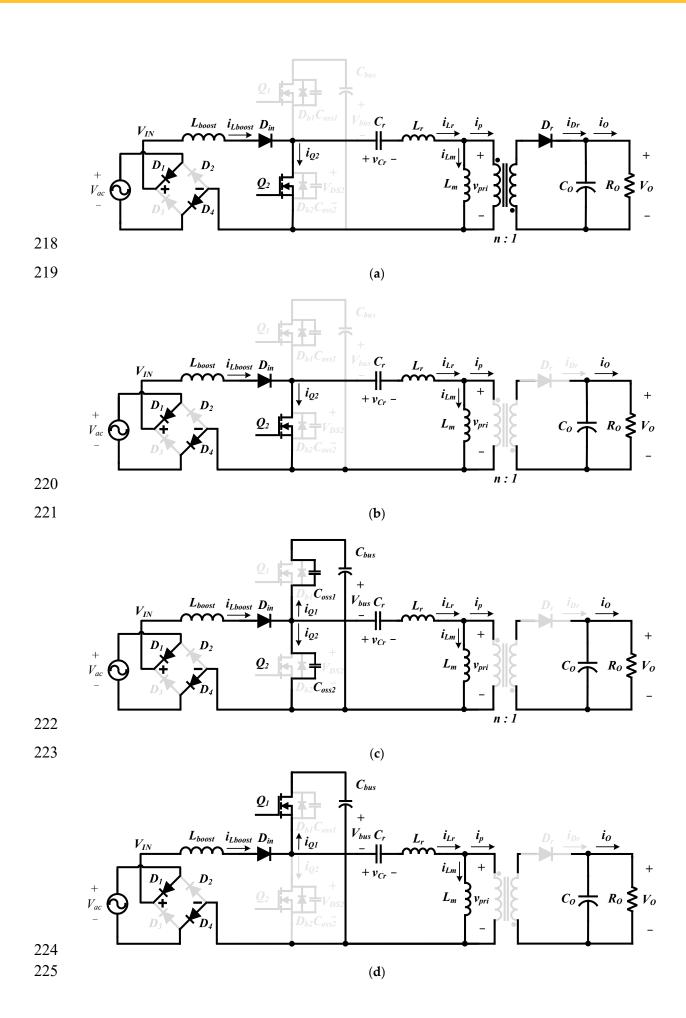

Figure 3 depicts the key waveforms of the proposed single-stage asymmetrical half-bridge fly-back converter with resonant mode. Six states are required to complete a switching cycle. The conduction paths for each operating state are illustrated in Figure 4.

**Figure 3.** Key waveforms of the proposed single-stage asymmetrical half-bridge fly-back converter with resonant mode.

132 State 1: *t*<sub>0</sub><*t*<*t*<sub>1</sub>

As shown in Figure 4,  $Q_2$  is turned on with the ZVS operating condition. In the meantime the rectifier diode  $D_r$  is conducted and the energies stored in the transformer magnetizing inductors are transferred to the output load. The output voltage is reflected to the primary side, therefore, the primary transformer is clamped to -nVo, and  $i_{Lm}$  decreases linearly. During this period, the resonant inductor  $L_r$  and resonant capacitor  $C_r$  begin to resonate. On the other hand, the diode  $D_{im}$  is conducted and the voltage across the input inductor  $L_{boost}$  is equal to the input voltage  $V_{IN}$  so the input inductor current  $i_{Lboost}$  increases linearly. The input current  $i_{Lboost}$  can be expressed as

$$i_{Lboost}(t) = \frac{V_{bus}}{L_{boost}}(t - t_0)$$

(5)

The resonant inductor current  $i_{Lr}$  and the resonant capacitor voltage  $v_{Cr}$  are given as

$$i_{Lr}(t) = i_{Lr}(t_0) \cdot \cos\left[\omega_r(t - t_0)\right] - \frac{v_{Cr}(t_0) + nV_o}{Z_r} \cdot \sin\left[\omega_r(t - t_0)\right]$$

(6)

$$v_{Cr}(t) = nV_O + \left[v_{Cr}(t_0) + nV_O\right] \cdot \cos\left[\omega_r(t - t_0)\right] + Z_r i_{Lr}(t_0) \cdot \sin\left[\omega_r(t - t_0)\right]$$

(7)

144 The magnetizing current  $i_{Lm}$  of transformer can be expressed as

145

$$i_{Lm}(t) = i_{Lm}(t_0) - \frac{nV_O(t - t_0)}{L_m}$$

(8)

- 146 This interval is ended when  $i_{Lr}$  equals  $i_{Lm}$  at  $t_1$ .

- 147 State 2: *t*<sub>1</sub><*t*<*t*<sub>2</sub>

- 148 At time  $t_1$  the input inductor current  $i_{Lboost}$  increases linearly. The resonant inductor current  $i_{Lr}$  is 149 the same as the magnetizing current  $i_{Lm}$  therefore, no current is transferred to the secondary side so 150 the rectifier diode  $D_r$  is turned off. During this mode, the resonant circuit is composed of  $C_r$ ,  $L_r$  and 151  $L_m$ . Moreover,  $L_m$  is equal to series with  $L_r$  and  $L_m$  is much larger than  $L_r$ , so that the resonant cycle is

- 152 much longer than the previous state. The  $i_{Lm}$ ,  $i_{Lr}$  and  $v_{Cr}$  are expressed as

153

$$i_{Lr}(t) = i_{Lr}(t_1) \cdot \cos\left[\omega_{r2}(t - t_1)\right] - \omega_{r2}C_r v_{cr}(t_1) \cdot \sin\left[\omega_{r2}(t - t_1)\right]$$

(9)

$$v_{Cr}(t) = v_{Cr}(t_1) \cdot \cos\left[\omega_{r2}(t - t_1)\right] + L_m i_{Lr}(t_1) \omega_{r2} \cdot \sin\left[\omega_{r2}(t - t_1)\right] + L_r i_{Lr}(t_1) \omega_{r2} \cdot \sin\left[\omega_{r2}(t - t_1)\right]$$

$$(10)$$

$$i_{Lm}(t) = i_{Lr}(t) \tag{11}$$

156 Where

$$\omega_{r2} = \frac{1}{\sqrt{C_r \cdot \left(L_m + L_r\right)}} \tag{12}$$

- 158 When  $Q_2$  is turned off this interval is ended.

- 159 State 3: *t*2<*t*<*t*3

- 160 The mode begins when  $Q_2$  is turned off at  $t = t_2$ . The magnetizing current  $i_{Lm}$  charges the  $Q_2$ 161 junction capacitors and discharges the  $Q_1$  junction capacitors until the  $Q_2$  junction capacitors equal 162  $V_{bus}$  and the  $Q_1$  body diode conducts. Therefore, at time  $t_3$ ,  $Q_1$  can be turned on to achieve ZVS. 163 During this period, which is used to allow enough time to achieve ZVS, as well as prevent shoot 164 through in the two switches, the  $i_{Lr}$  and  $v_{Cr}$  are expressed as

$$i_{Lr}(t) = i_{Lr}(t_2) \cdot \cos\left[\omega_{r1}(t - t_2)\right] - \omega_{r2}C_r v_{cr}(t_1) \cdot \sin\left[\omega_{r1}(t - t_2)\right]$$

(13)

$$v_{Cr}(t) = \frac{i_{Lr}(t_2)}{\omega_{r1}C_r} \cdot \sin\left[\omega_{r1}(t - t_2)\right] + v_{cr}(t_2) \cdot \cos\left[\omega_{r1}(t - t_2)\right]$$

(14)

167 Where

168

$$\omega_{r1} = \frac{1}{\sqrt{(L_m + L_r) \cdot (C_{eq} \parallel C_r)}}, \quad C_{oss1} = C_{oss2}; C_{eq} = C_{oss1} = C_{oss2}$$

(15)

The input current  $i_{Lboost}$  can be expressed as

$$i_{Lboost}(t) = -\frac{V_{IN} - V_{bus}}{L_{boost}}(t - t_2)$$

(16)

171 State 4: *t*<sub>3</sub><*t*<*t*<sub>4</sub>

172

173

174

175

176

177

In this state,  $Q_I$  is turned on which carries the resonant inductor current  $i_{Lr}$  and input inductor current  $i_{Lboost}$ . The voltage across the input inductor  $L_{boost}$  is about  $(V_{IN}-V_{bus})$  so the input inductor current  $i_{Lboost}$  linearly decreasing. Referring to Figure 4(d), the rectifier diode  $D_r$  is reverse-biased and in the meantime the input energy is stored in the primary magnetizing inductance  $L_m$ , while the output capacitors  $C_O$  provide energy to the output load. The resonant inductor current  $i_{Lr}$ , magnetizing inductance current  $i_{Lm}$  and resonant capacitors voltage  $v_{Cr}$  can be expressed as

178

$$i_{Lr}(t) = i_{Lr}(t_3) \cdot \cos\left[\omega_{r_2}(t - t_3)\right] + \omega_{r_2}C_r v_{bus} \cdot \sin\left[\omega_{r_2}(t - t_3)\right] \\ -\omega_{r_2}C_r v_{cr}(t_3) \cdot \sin\left[\omega_{r_2}(t - t_3)\right]$$

$$(17)$$

179

$$v_{Cr}(t) = v_{cr}(t_3) + i_{Lr}(t_3) \cdot \cos\left[\omega_{r_2}(t - t_3)\right] + \omega_{r_2}C_r v_{bus} \cdot \sin\left[\omega_{r_2}(t - t_3)\right] - \omega_{r_2}C_r v_{cr}(t_3) \cdot \sin\left[\omega_{r_2}(t - t_3)\right]$$

$$(18)$$

$$i_{Lm}(t) = i_{Lr}(t) \tag{19}$$

181 The input current  $i_{Lboost}$  are given as

$$i_{Lboost}(t) = -\frac{V_{IN} - V_{bus}}{L_{boost}}(t - t_3)$$

(20)

- When input current *i*<sub>Lboost</sub> reach zero level, this interval is ended.

- 184 State 5: *t*<sub>4</sub><*t*<*t*<sub>5</sub>

- During this stage,  $Q_1$  remains turned on so that the direction of  $i_{Lr}$  is reversed. As with Stage 4 the primary magnetizing inductance  $L_m$  stores energy and the output capacitors  $C_0$  continue to provide energy through the output load. The current in  $L_{boost}$  stays at zero (DCM operation) so the PFC feature can be achieved. In the meantime, diode  $D_{in}$  is in reverse bias. The resonant inductor current  $i_{Lr}$ , magnetizing inductance current  $i_{Lm}$  and the resonant capacitor voltage  $v_{Cr}$  are given as

190

$$i_{Lr}(t) = i_{Lr}(t_4) \cdot \cos\left[\omega_{r2}(t - t_4)\right] + \omega_{r2}C_r v_{bus} \cdot \sin\left[\omega_{r2}(t - t_4)\right] - \omega_{r2}C_r v_{cr}(t_4) \cdot \sin\left[\omega_{r2}(t - t_4)\right]$$

(21)

191

$$v_{Cr}(t) = v_{cr}(t_4) + i_{Lr}(t_4) \cdot \cos\left[\omega_{r2}(t - t_4)\right] + \omega_{r2}C_r v_{bus} \cdot \sin\left[\omega_{r2}(t - t_4)\right] - \omega_{r2}C_r v_{cr}(t_4) \cdot \sin\left[\omega_{r2}(t - t_4)\right]$$

(22)

Peer-reviewed version available at Energies 2018, 11, 1721; doi:10.3390/en1107172

$$i_{Lm}\left(t\right) = i_{Lr}\left(t\right) \tag{23}$$

193 where

$$\omega_{r2} = \frac{1}{\sqrt{C_r \cdot (L_m + L_r)}} \tag{24}$$

- When  $Q_1$  turned off, this interval is ended.

- 196 State 6: *t5*<*t*<*t*6

In this stage,  $Q_1$  and  $Q_2$  are turned off and the input current  $i_{Lboost}$  remains at zero, while the output capacitors continue to provide energy through the output load. At this interval, the resonant current  $i_{Lr}$  charges the  $Q_1$  junction capacitors and discharges the  $Q_2$  junction capacitors. When  $Q_1$  equals  $V_{bus}$  and the body diode across  $Q_2$  conducts, this interval is ended and the operating state returns to Stage 1 to begin the next switching cycle. The resonant inductor current  $i_{Lr}$ , magnetizing inductance current  $i_{Lm}$  and resonant capacitor voltage  $v_{Cr}$  can be expressed as

$$i_{Lr}(t) = i_{Lr}(t_5) \cdot \cos\left[\omega_{r1}(t - t_5)\right] + \omega_{r1}C_r v_{Cr}(t_5) \cdot \sin\left[\omega_{r1}(t - t_5)\right]$$

(25)

$$v_{Cr}(t) = \frac{I_{Lr}(t_5)}{\omega_{r1}C_r} \cdot \sin\left[\omega_{r1}(t - t_5)\right] + v_{Cr}(t_5) \cdot \cos\left[\omega_{r2}(t - t_5)\right]$$

(26)

$$i_{Lm}(t) = i_{Lr}(t) \tag{27}$$

- When Stage 6 ends the operating state returns to Stage 1 and the next switching cycle begins.

- 207 State 6: *t*5<*t*<*t*6

In this stage,  $Q_1$  and  $Q_2$  are turned off and the input current  $i_{Lboost}$  remains at zero, while the output capacitors continue to provide energy through the output load. At this interval, the resonant current  $i_{Lr}$  charges the  $Q_1$  junction capacitors and discharges the  $Q_2$  junction capacitors. When  $Q_1$  equals  $V_{bus}$  and the body diode across  $Q_2$  conducts, this interval is ended and the operating state returns to Stage 1 to begin the next switching cycle. The resonant inductor current  $i_{Lr}$ , magnetizing inductance current  $i_{Lm}$  and resonant capacitor voltage  $v_{Cr}$  can be expressed as

$$i_{Lr}(t) = i_{Lr}(t_5) \cdot \cos\left[\omega_{r1}(t - t_5)\right] + \omega_{r1}C_r v_{Cr}(t_5) \cdot \sin\left[\omega_{r1}(t - t_5)\right]$$

(28)

$$v_{Cr}(t) = \frac{I_{Lr}(t_5)}{\omega_{-1}C_{rr}} \cdot \sin\left[\omega_{r1}(t-t_5)\right] + v_{Cr}(t_5) \cdot \cos\left[\omega_{r2}(t-t_5)\right]$$

(29)

$$i_{Lm}(t) = i_{Lr}(t) \tag{30}$$

When Stage 6 ends the operating state returns to Stage 1 and the next switching cycle begins.

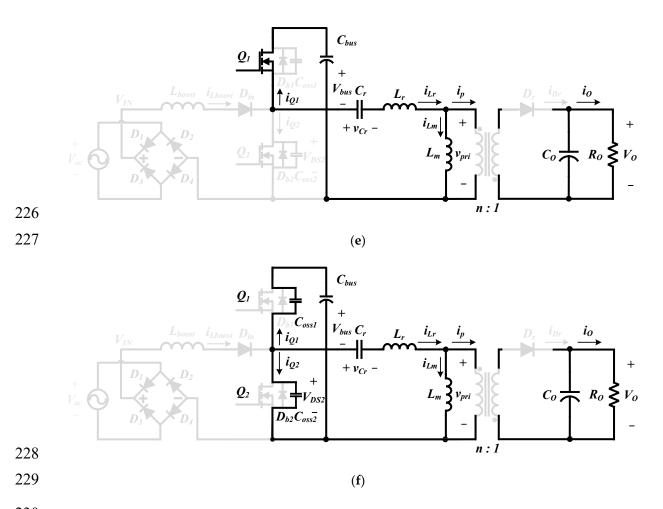

Figure 4. Operation Modes of the proposed single-stage asymmetrical half-bridge fly-back converter during one switching period: (a) State 1; (b) State 2; (c) State 3; (d) State 4; (e) State 5; (f) State 6.

## 3. Circuit Design for the Proposed Converter

232

233

234

236

237

238

$D_{max}$  is the maximum duty cycle for the proposed converter. For to achieve high power-factor the input inductor current must be operated in DCM so the input inductor  $L_{boost}$  can be expressed as

$$L_{boos} < \frac{V_{bus}T_s}{2 \cdot i_{IN \text{ peak}} f_{s \text{ min}}} \cdot (D_{\text{max}}) \cdot (1 - D_{\text{max}})^2$$

(31)

Where  $i_{IN\_peak}$  is the maximum peak-current of the input inductor  $L_{boost}$ , and  $f_{s\_min}$  is the lowest switching frequency for the proposed converter. From equation (28), when  $L_m$  is greater than the resonant inductor  $L_r$ , the voltage gain can be approximated as

$$V_O = \frac{1}{n} V_{bus} \cdot (1 - D) \tag{32}$$

240 Therefore, the turn ratio of the transformer primary winding to secondary winding can be equal to

$$n = \frac{V_{bus}}{V_O} \cdot (1 - D) \tag{33}$$

At  $t = t_3$ , to ensure the ZVS operation for  $Q_1$ , the magnetizing inductance current  $i_{Lm}$  must discharge the  $C_{0851}$  until the voltage is equal to zero so the minimum  $i_{Lm}$  at  $t_3$  can be given as

$$i_{Lm(t_3)_{-}\min} = \frac{nV_O}{2L_m} \cdot D_{\min} T_s$$

(34)

According to equation (31), the maximum magnetizing inductance  $L_m$  can be expressed as

$$L_{m(t_3)_{-}\max} = \frac{nV_O \cdot t_{dead}}{2 \cdot V_{bus} \left( C_{oss1} + C_{oss2} \right) \cdot f_s} \cdot D_{\min}$$

(35)

- On the other hand, at  $t = t_6$ , to ensure ZVS operation for  $Q_2$ , the magnetizing inductance current  $i_{Lm}$  must discharge  $C_{oss2}$  until the voltage is equal to zero so the minimum  $i_{Lm}$  at  $t_6$  can be given as

- 249  $i_{Lm(t_6)_{-\min}} = \frac{nV_O}{2 \cdot L_m \cdot f_s} \cdot (1 D_{\max})$  (36)

- According to equation (33), the maximum magnetizing inductance  $L_m$  can be expressed as

251

$$L_{m(t_6)_{-}\max} = \frac{nV_O \cdot t_{dead}}{2 \cdot V_{bus} \left( C_{oss1} + C_{oss2} \right) \cdot f_s} \cdot (1 - D_{\max})$$

(37)

- Form Figure 3a, the resonant capacitor  $C_r$  and the resonant inductor  $L_r$  are resonating from  $t_0$  to  $t_1$ , this time interval is during the  $Q_2$  turn-on time, which is about half the resonant period and can be

- approximately expressed as

$$C_r \le \frac{\left(\frac{2 \cdot D_{\text{max}}}{\omega_r}\right)^2}{L_r} \tag{38}$$

256 The output filter capacitance *Co* can be calculated as

$$C_O \ge \frac{\frac{P_O}{V_O} \cdot (1 - D_{\text{max}})}{\Delta V_O \cdot f_s}$$

(39)

- Where  $f_s$  is the switching frequency and  $\Delta V_0$  is the output voltage ripple. The voltage stresses of  $Q_1$

- and  $Q_2$  are equal to  $V_{bus}$ . The voltage stresses of the secondary diode  $D_r$  is

$$D_r = \frac{D_{\text{max}} \cdot V_{bus}}{n} + V_O \tag{40}$$

The peak secondary diode current is expressed as

$$I_{Dr,\text{max}} = \frac{\pi}{2 \cdot (1 - D_{\text{max}})} \cdot I_O \tag{41}$$

263

## 4. Experimental Results

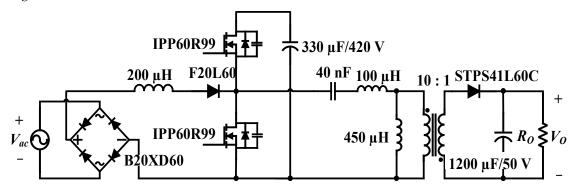

In order to verify the feasibility of the proposed converter, a 120 W prototype converter is built in the laboratory. Figure 5. shows the proposed converter and the experimental parameters are designed in Table 1.

**Figure 5.** Implementation of the proposed single-stage asymmetrical half-bridge fly-back converter with resonant mode.

**Table 1**. Experimental parameters of the proposed converter.

| Parameters                | Value                            |

|---------------------------|----------------------------------|

| Input ac voltage range:   | 85~264 Vrms                      |

| Output voltage:           | $V_0 = 19 \text{ V}$             |

| Output voltage ripple:    | $\triangle V_O = 0.95 \text{ V}$ |

| Intermediate bus voltage: | V <sub>bus</sub> =420 V          |

| Maximum output current:   | Io = 6.32 A                      |

| Input inductor:           | $L_{boost} = 200 \ \mu H$        |

| Magnetizing inductance:   | $L_m = 450  \mu \text{H}$        |

| Turns ratio:              | $n = N_p/N_s = 3T$               |

| Resonant inductor:        | $L_r = 100  \mu \text{H}$        |

| Maximum duty cycle:       | $D_{max} = 0.75$                 |

| Resonant capacitors:      | $C_r = 40 \text{ nF}$            |

| Switching frequency:      | $f_s = 60 \sim 150 \text{ kHz}$  |

| Output capacitor:         | Co = 1200 μF                     |

A PQ26/20 TDK core is used for the input inductor. The PQ32/30 core is used for the isolation transformer and the transformer turn ratio is calculated from (29). The magnetizing inductance  $L_m$  is designed from (32) at approximately 450  $\mu$ H. The IPP60R99 MOSFET is used producing output capacitance Coss of about 130 pF at a 430 V drain-to-source voltage, including the output capacitances of  $Q_1$  and  $Q_2$  it is about 260 pF. Therefore, to ensure ZVS operations, 330 ns dead time was inserted between the  $Q_1$  and  $Q_2$  gate signals. The resonant frequency  $f_r$  is placed at about 80 kHz so the resonant capacitor  $C_r$  and resonant inductor  $L_r$  can be calculated from (35). The output voltage

ripple  $\Delta Vo$  is required to be smaller than 0.95 V. The output capacitor Co is calculated to be greater than 474  $\mu$ F from equation (36). Therefore, a 1200  $\mu$ F output capacitor is used.

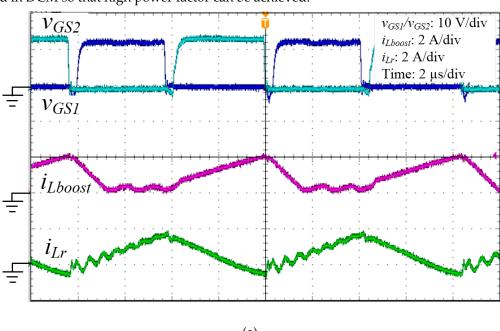

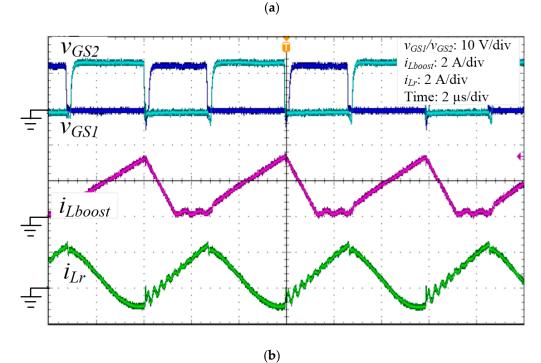

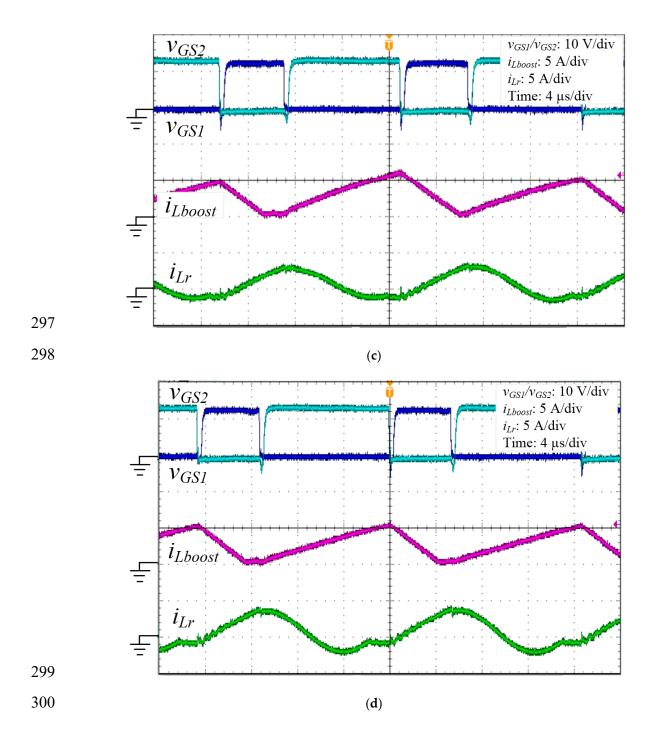

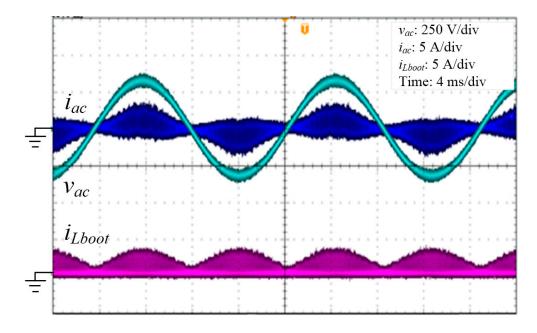

Figure 6 shows the experimental results for  $v_{GS1}$ ,  $v_{GS2}$ ,  $i_{Lboost}$  and  $i_{Lr}$  at different output currents and at  $V_{In,main}$ . Referring to Figure 3, six operation states can be observed in Figure 6. When  $Q_1$  is turned on and  $Q_2$  is turned off, the  $i_{Lboost}$  linearly decreases and  $i_{Lr}$  linearly increases. When  $Q_1$  and  $Q_2$  are turned off, ZVS operation can be achieved. During the  $Q_1$  turned off and  $Q_2$  turned on period, the  $i_{Lboost}$  increases linearly and the resonant inductor  $L_r$  and resonant capacitor begin to resonate. On the other hand, Figure 6 also shows that when the output load increases from light load to full load, the duty ratio of  $Q_2$  increases from 0.5 to 0.75 for regulated bus voltage  $V_{bus}$ , and the switching frequency decreases from about 125 kHz to 62 kHz for regulated output voltage  $V_0$ . Figure 7 shows the measured input voltage  $v_{ac}$ , input current  $v_{ac}$  and input inductor current  $v_{ac}$  under full load conditions. The input current near sinusoidal waveform and input inductor current are shown operated in DCM so that high power factor can be achieved.

**Figure 6.** Waveforms for *v*<sub>GS1</sub>, *v*<sub>GS2</sub>, *i*<sub>Lboost</sub> and *i*<sub>Lr</sub> at different load current: (a) 1.6 A; (b) 3.2 A; (c) 4.7 A; (d) 6.3 A.

**Figure 7.** Waveforms for  $v_{ac}$ ,  $i_{ac}$  and  $i_{Lboost}$  at  $v_{ac}$  = 230  $V_{rms}$ .

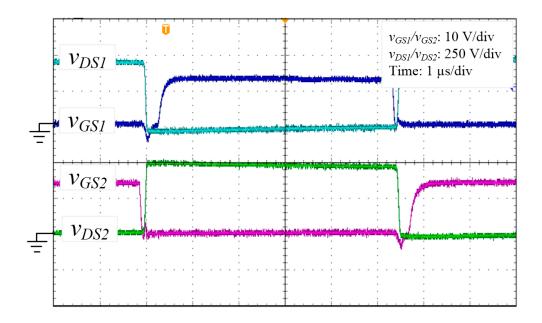

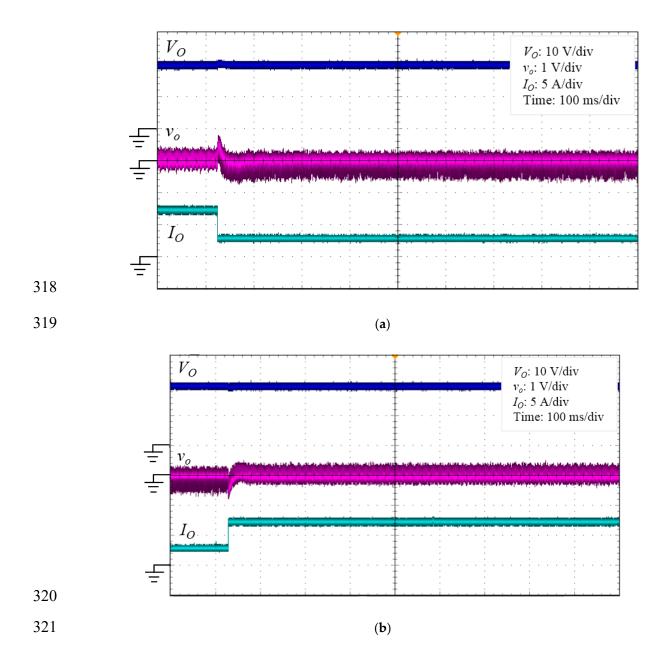

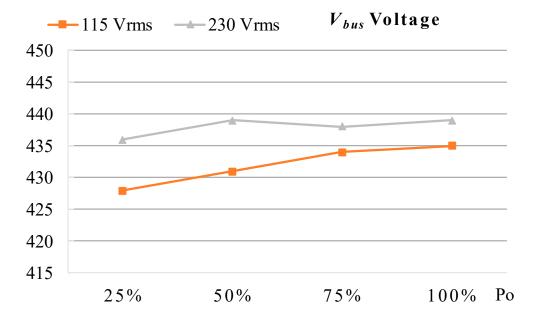

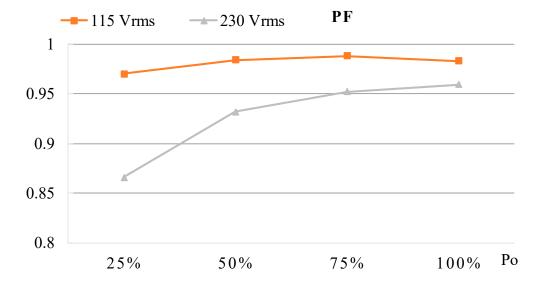

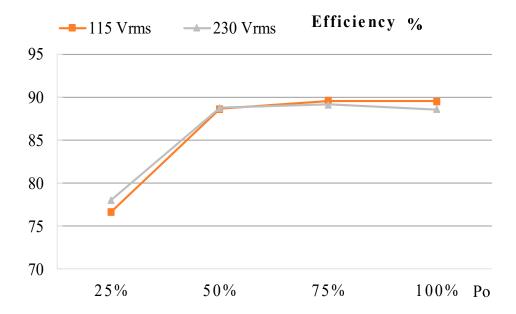

Figure 8 shows the gate-to-source waveforms and drain-to-source voltages for primary switches  $Q_1$  and  $Q_2$  at the full-load. The waveform shows that  $V_{DS1}$  and  $V_{DS2}$  reach zero levels after  $Q_1$  and  $Q_2$  are turned on. Therefore, ZVS conduction is achieved so that overall conversion efficiency is increased. The transient output voltage  $V_0$  during a step load current from 1.6 to 6.3 A and 6.3 to 1.6 A are shown in Figure 8 when input voltage of 230  $V_{rms}$ , which shows that  $V_0$  can still be regulated. Figure 10 depicts the bus voltage variation under 25%, 50%, 75% and 100% load condition and the bus voltage is regulated around 430 V. Figure 11 also depicts the input current power factor. It indicates that the power factor is greater than 0.9 at different load conditions. Figure 12 shows the measured efficiencies of the proposed single stage asymmetrical half-bridge fly-back converter through different outputs. The average efficiency is around 86% above which the rated full load efficiency is about 90%.

**Figure 8.** Zero-voltage turn-on switching for  $Q_1$  and  $Q_2$ .

Figure 9. Load transient response under different loads: (a) 20% to 100%; (b) 100% to 20%.

324

**Figure 10.**  $V_{bus}$  voltage variation curve for 115  $V_{rms}$  and 230  $V_{rms}$ .

325

**Figure 11.** PF curve for 115  $V_{rms}$  and 230  $V_{rms}$ .

**Figure 12.** Efficiency curve for 115 V<sub>rms</sub> and 230 V<sub>rms</sub>

#### 5. Conclusions

This paper presented a single stage asymmetrical half-bridge fly-back converter with resonant mode. The switches operate simultaneously in the variable-frequency-controller (VFC) and pulse-width-modulation (PWM) control to regulate the bus voltage and output voltage. The operating modes in a complete switching cycle were analyzed and discussed in detail. The key equations were derived and the design procedures formulated. The experimental results on an AC input voltage 90 to 264  $V_{rms}$  with output 120 W prototype were recorded to verify the theoretical scheme. The measured results show that the power factor is above 0.9, the average efficiency is around 86% and the highest conversion efficiency is about 90%. The proposed single stage asymmetrical half-bridge fly-back converter is especially suitable for low-to-medium power level applications.

**Author Contributions:** Chung-Yi Ting designed, simulated the work, and wrote the paper; Yi-Chieh Hsu implemented the work and performed the experiment; Jing-Yuan Lin and Chung-ping Chen provided all material for implementing the work, supervised the design, circuit simulation, analysis, experiment, and correct the paper.

**Acknowledgments:** The authors would like to acknowledge the financial support of the Ministry of Science and Technology of Taiwan through grant number MOST 106-2221-E-011-095-MY3.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Qian, J.; Lee, F.C. A high-efficiency single-stage single-switch high-power-factor AC/DC converter with universal input. *IEEE Trans. Power Electron.* **1998**, 13, 699-705. [CrossRef]

- 2. Kang, F.S.; Park, S.J.; Kim, C.U. ZVZCS single-stage PFC AC-to-DC half-bridge converter. *IEEE Trans. Industrial Electron.* **2002**, 49, 206-216. [CrossRef]

- 3. Zhang, J.; Lee, F.C.; Jovanovic, M.M. An improved CCM single-stage PFC converter with a low frequency auxiliary switch. *IEEE Trans. Power Electron.* **2003**, 18, 44-50. [CrossRef]

- 356 4. Ogata, M.; Nishi, T. Graph-theoretical approach to 2-switch DC-DC converter. *International Journal of Circuit Theory and Applications.* **2005**, 33, 161-173. [CrossRef]

- 5. O'Sullivan, D. L.; Egan, M.G.; Willers, M. J. A Family of Single-Stage Resonant AC/DC Converters with PFC. *IEEE Trans. Power Electron.* **2009**, 24, 398-408. [CrossRef]

- 360 6. Willers, M.J.; Egan, M.G.; Daly, S.; Murphy, J.M.D. Analysis and design of a practical discontinuous-conduction-mode BIFRED converter. *IEEE Trans. Industrial Electron.* 1999, 46, 724-733. [CrossRef]

- 563 7. Shu, Y.; Lin, B.T. Add active clamping and soft switching to boost flyback single stage isolated power factor corrected power supplies. *IEEE Trans. Power Electron.* **2011**, 26, 3144-3152. [CrossRef]

- 365 8. Chen, S.Y.; Li, Z.R.; Chen, C. L. Analysis and Design of single stage AC/DC LLC resonant converter. *IEEE Trans. Industrial Electron.* **2012**, 59, 1538-1544. [CrossRef]

- Luo, S.; Wei, H.; Zhu, G.; Batarseh, I. Several schemes of alleviating bus voltage stress in single stage

power factor correction converters. *In Proceedings Power Electronics and Drive Systems Conference*, Hong

Kong, 27-29 July 1999; pp. 921-926.

- 370 10. Wu, X.; Yang, J.; Zhang, J.; Xu, M. Design Considerations of Soft-Switched Buck PFC Converter with Constant On-Time (COT) Control. *IEEE Trans. Power Electron.* **2011**, 26, 3144-3152. [CrossRef]

- 372 11. Wu, X.; Zhang, J.; Ye X.; Qian, Z. Analysis and Derivations for a Family ZVS Converter Based on a New Active Clamp ZVS Cell. *IEEE Trans. Industrial Electron.* **2008**, 55, 773-781. [CrossRef]

- 12. Choi, B.; Lim, W.; Bang, S.; Choi, S. Small-signal analysis and control design of asymmetrical half-bridge DC-DC converters. *IEEE Trans. Industrial Electron.* **2006**, 53, 511-520. [CrossRef]

- 376 13. Watson, R.; Hua, G.C.; Lee, F.C. Characterization of an active clamp flyback topology for power factor correction applications. *IEEE Trans. Power Electron.* **1996**, 11, 191-198. [CrossRef]

- 378 14. Kim, K.T.; Kwon, J.M.; Lee, H.M.; Kwon, B.H. Single-stage high-power factor half-bridge flyback converter with synchronous rectifier. *IET Trans. Power Electron.* **2014**, *7*, 1755-4535. [CrossRef]

- 380 15. Buso, S.; Spiazzi, G.; Sichirollo, F. Study of the asymmetrical half-bridge flyback converter as an effective line fed solid state lamp driver. *IEEE Trans. Industrial Electron.* **2014**, 61, 6730-6738. [CrossRef]

- 382 16. Song, W.; Zhong, Y.; Zhang, H.; Sun, X.; Zhang, Q.; Wang, W. A Study of Z-Source Dual-Bridge Matrix

383 Converter Immune to Abnormal Input Voltage Disturbance and with High Voltage Transfer Ratio. *IEEE*384 *Trans. Industrial Informat.* 2013, 9, 828-838. [CrossRef]

- Li, H.; Zhou, W.; Zhou, S.; Yi, X. Analysis and design of high frequency asymmetrical half bridge flyback

converter. Electrical Machines and Systems International Conference, Wuhan, China, 17-20 October 2008;

pp. 1902-1904.

- 388 18. Tse, C.K.; Chow, M.H.L. New single-stage power-factor-corrected regulators operating in discontinuous capacitor voltage mode. In Proceedings of the 28th IEEE Power Electronics Specialists Conference, Saint Louis, MO, USA, 27-27 June 1997; pp. 371-377.