## Article

# New Switched-Dual-Source Multilevel Inverter for Symmetrical and Asymmetrical Operation

Kennedy Aganah <sup>1\*</sup>, Cristopher Luciano <sup>1</sup>, Mandoye Ndoye <sup>1</sup> and Gregory Murphy <sup>1</sup>

<sup>1</sup> Tuskegee University, Tuskegee AL, USA; kaganah@tuskegee.edu; cluciano0209@tuskegee.edu; mndoyle@tuskegee.edu; gmurphy@tuskegee.edu

\* Correspondence: kaganah@tuskegee.edu; Tel.: +1-334-724-4470

Academic Editor: name

Version March 12, 2018 submitted to Entropy

**Abstract:** The past two decades has seen a growing demand for high-power, high-voltage utility scale inverters mostly fueled by the integration of large solar PV and wind farms. Multilevel inverters have emerged as the industry choice for these megawatt range inverters because their reduced voltage stress, capable of generating an almost sinusoidal voltage, in-built redundancy, among others. This paper present a new Switched-Source Multilevel Inverter (SS MLI) architecture. The new inverter show superior over existing topologies. It has reduced voltage stress on the semiconductor, uses less number of switches –reduced size/weight/cost and increased efficiency. The new SSMLI is comprised of two voltage sources ( $V_1, V_2$ ) and 6 switches. It is capable of generating 5-level output voltage in symmetric modes (i.e.,  $V_1 = V_2$ ), and 7-level output voltage in asymmetric modes (i.e.,  $V_1 \neq V_2$ ). To demonstrate the validity of the proposed inverter, simulations results using MATLAB®/Simulink® for 5- and 7-level output voltages are presented. The simulations are also verified experimentally using a laboratory prototype.

**Keywords:** multilevel; inverter; single phase; reduced switch-count; h-bridge.

---

## 1. Introduction

The past couple of decades has seen huge investments in renewable resources (RES) as a way to reduce carbon footprint. These initiatives have resulted, in recent years, in the installation of utility scale wind and solar PV farms. The operations of such MW-scale plants require high voltage/power multilevel inverters (MLIs), leading to the proliferation of MLI [1,2]. MLIs can be categorized into three types:neutral-point-clamped (NPC) [2,3], flying-capacitor (FC) [4,5], and cascaded H-bridge (CHB) topologies[6,7]. Some research have also proposed hybrids of the above types [8,9]. The main advantages of MLIs over their traditional 2-level counterparts are improved power quality, reduced filter requirements, lower electromagnetic interference, and lower  $dv/dt$  stress on loads [10,11].

A shortcoming of NPC topology is an unbalance of the neutral point leading to uneven thermal distribution among the semiconductor devices, increase in harmonics, and reduction of power quality [12]. FC inverters also suffer from capacitor voltage imbalance issues, which lead to a deterioration of power quality and an increase in blocking voltages. They also require larger capacitor banks and additional pre-charging circuitry. CHB MLIs suffer from input DC leakage current that could damage, for example, PV panels and pose safety problems [13,14]. However, CHB topology has a lot of advantages – modularity, fewer number of components, symmetric and asymmetric operating modes (i.e., equal and unequal DC sources), etc.

Many recent studies on the CHB topology have focused on generating more voltage levels by using switched-capacitor (SC) or switched-source (SS) MLI configurations. The SC MLIs [15,16] aim to produce more output voltage levels with a single or minimal number of power supplies and a series of self-balancing capacitors. However, they suffer from increased voltage stress on the switches and power dissipation in the increasing number of series diodes [15]. Several SS MLIs are proposed in [7,17]. Unlike the SC configuration where capacitors are switched in series/parallel combinations, the

37 SS configuration uses instead multiple DC sources to achieve the voltage levels. This configuration is

38 inherently suited for applications where there are multiple DC sources such as in battery storage, solar

39 PV or fuel cells. In the SS configuration, a higher number of voltage levels can be obtained when the

40 DC sources have different amplitudes (asymmetric operation) [18] than the symmetric topology (all

41 DC sources have the same amplitude) using the same number of components (sources, switches, and

42 passive devices). Additionally, the current commutation path is generally shorter in the SS topology

43 than in the SC topology; thereby, reducing power dissipation. Another advantage of SS MLIs over

44 SC MLIs is the high number of redundant switching states which may be useful for certain control

45 applications, e.g., fault-tolerant inverters.

46 In this paper, a new SS MLI topology is proposed. The new topology exhibits better performance,

47 when compared to similar SS MLI topologies, in terms of the number of switches, current commutation

48 path, and voltage stress on the switches. The validity of the proposed topology is verified by

49 MATLAB®/Simulink® simulations. The rest of the paper is organized as follows: The structure and

50 operation of the inverter is presented in Section 2. Comparisons among the topologies is discussed in

51 Section 3, and simulation results are presented in Section 4. Finally, conclusions are drawn in Section 5.

## 52 2. Architecture and Principle of Operation

### 53 2.1. Architecture

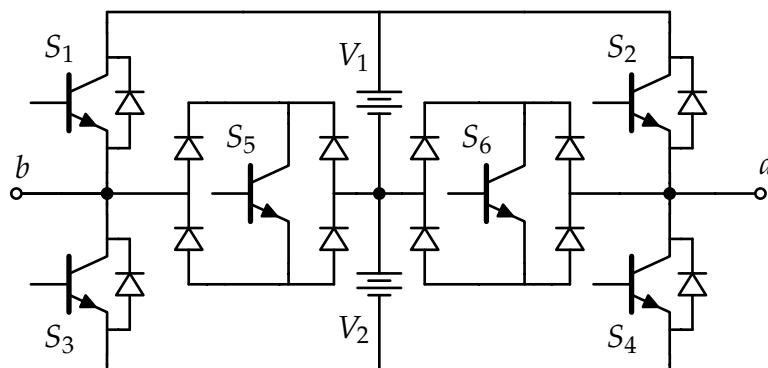

54 The basic unit of the proposed MLI (see Fig. 1) is comprise two DC power sources ( $V_1$  and  $V_2$ ),

55 four unidirectional switches ( $S_1, S_2, S_3$  and  $S_4$ ), and two bidirectional switches ( $S_5$  and  $S_6$ ). This basic

56 unit, it is capable of generating 5-level output voltage (i.e.,  $V_{ab}$ ), when  $V_1 = V_2$  (i.e., symmetric mode

57 operation), and 7-level output voltage when  $V_1 \neq V_2$  (i.e., asymmetric mode operation). The basic unit

58 can be cascaded to generate more voltage levels. If  $m$  number of basic units are cascaded as shown

59 in Fig. 2, the inverter can generate up to  $(2^{m+1} + 1)$  and  $(2^{2m+1} - 1)$  ( $m = 1, 2, 3, \dots$ ) output voltage

60 levels for symmetric and asymmetric operations, respectively.

61 In order to avoid short-circuiting of the DC power sources, only one of the left side switches (i.e.,

62  $S_1, S_3, S_5$ ) can conduct at any instant. Similarly, only one of the right side switches (i.e.,  $S_2, S_4, S_6$ ) can

63 be ON at the same time. That is,

$$S_1 + S_3 + S_5 = 1; S_2 + S_4 + S_6 = 1 \quad (1)$$

64 where  $S_k$  denotes the switching function of switch  $k$  ( $k = 1, 2, \dots, 6$ ), and takes the value of 1 when ON,

65 and 0 when OFF. Based on (1), Table 1 shows all the switching states of the basic unit and the resulting

66 inverter output voltage. It consists of three null states Based on (1), Table 1 shows all the switching

67 states of the basic unit and the resulting inverter output voltage. It consists of three null states (i.e.,

Figure 1. Structure of the proposed topology as standalone.

**Figure 2.**  $m$  cascaded units to generate more voltage levels.

**Table 1.** Switches states for basic unit

| States | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $V_{ab}$       |

|--------|-------|-------|-------|-------|-------|-------|----------------|

| 1      | 0     | 0     | 1     | 1     | 0     | 0     | 0              |

| 2      | 0     | 0     | 1     | 0     | 0     | 1     | $+V_2$         |

| 3      | 0     | 0     | 0     | 1     | 1     | 0     | $-V_2$         |

| 4      | 0     | 0     | 0     | 0     | 1     | 1     | 0              |

| 5      | 0     | 1     | 1     | 0     | 0     | 0     | $+(V_1 + V_2)$ |

| 6      | 0     | 1     | 0     | 0     | 1     | 0     | $+V_1$         |

| 7      | 1     | 0     | 0     | 1     | 0     | 0     | $-(V_1 + V_2)$ |

| 8      | 1     | 0     | 0     | 0     | 0     | 1     | $-V_1$         |

| 9      | 1     | 1     | 0     | 0     | 0     | 0     | 0              |

68  $V_{ab} = 0V$ ) and six active states. The three redundant null states may be utilized to achieve different

69 control objectives. The authors did not investigate this in this paper. In Table 1, the states shown in

70 light-gray (i.e., all except 4) are the states utilized in this paper. The bidirectional switches protect the

71 inverter from short circuits when it operates in asymmetrical mode.

72 The use of bidirectional switches distorts the output waveform (at low voltage levels, but is

73 insignificant at medium high voltage level applications) due to the voltage drop in each one of the

74 diodes of the rectifier bridge (two diodes forward biased simultaneously,  $V_{drop} \approx 2 \times 0.7 = 1.4$  V).

75 and six active states Table 1 shows that there are three redundant null states (0V output). The states

76 shown in light-gray are the ones used in this paper. The bidirectional switches protect the inverter from

77 short circuits when it operates in asymmetrical mode. The use of bidirectional switches distorts the

78 output waveform (at low voltage levels, but is insignificant at medium high voltage level applications)

79 due to the voltage drop in each one of the diodes of the rectifier bridge (two diodes forward biased

80 simultaneously,  $V_{drop} \approx 2 \times 0.7 = 1.4$  V).

## 81 2.2. Operation principle

82 The generation of the multilevel voltage output is based on the switching states given in Table 1.

83 For example, to produce a 7-level output ( $V_{ab}$ ), at least one null state (i.e., state 1, 4 or 9) and all the

84 active states (i.e., 2, 3, 5, 6, 7, and 8) are fired in a sequence to achieve the 7-level output. For uniform

85 power dissipation among the six switches, two null states (i.e., 1 and 9) are utilized; with state 1 during

86 the positive half-cycle and state 9 in the negative half-cycle. The Phase Disposition PWM (PD-PWM)

87 is selected based on its superior performance [19], but any PWM method may be used to control the

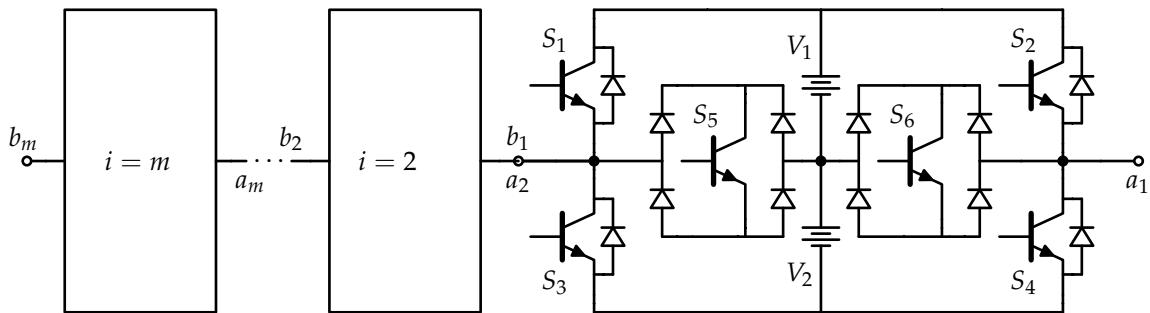

88 semiconductor switches. Fig. 3 show the current commutation for each switching state. For example,

89 to produce ( $V_1 + V_2$ ) in the positive half-cycle, switches  $S_1$  and  $S_3$  must be turned ON (i.e., state 5 in

90 Table 1). The current flow is as shown in Fig. 3e. Fig. 3 show the current commutations for all the 7

91 voltage levels. Note that if  $V_1 = V_2$ , a maximum of 5-level output can be realized.

### 92 3. Comparison with similar topologies

93 In this section, the proposed topology is compared with the topologies presented in [20,21], and

94 the conventional cascaded H-bridge topology also discussed in [21]. The comparison is made in

95 terms of (i) total number of semiconductor devices , (ii) number of active components in current path

96 (conduction losses) and voltage stress that each switch will be required to handle.

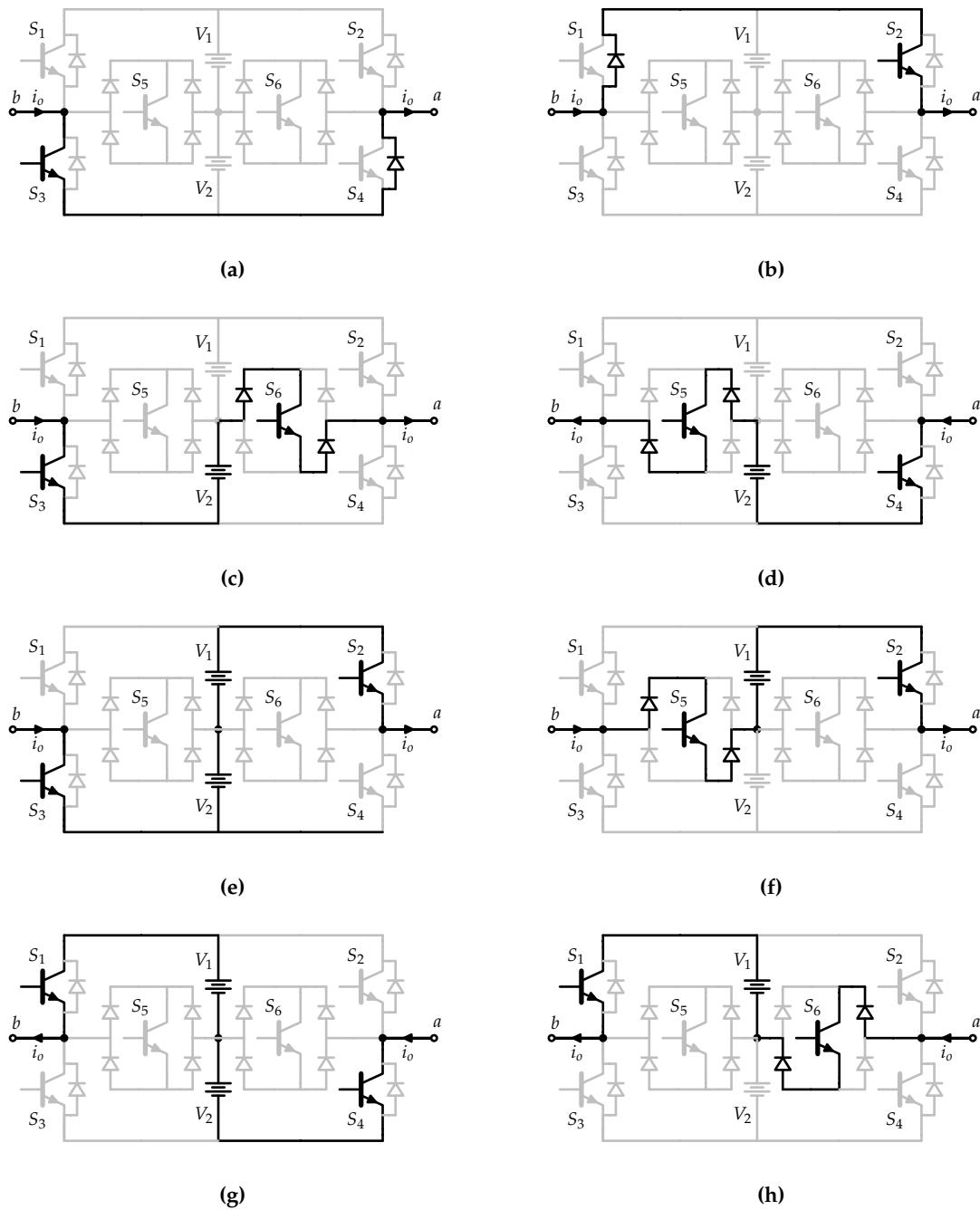

#### 97 3.1. Number of semiconductor devices

98 The number of semiconductor devices have an impact on the cost and size/weight of the MLI

99 unit; being able to generate the same number of voltage levels in the output of the inverter by using

100 less number of switches will lower cost and at the same give a compact inverter. Fig. 4a and Fig. 4b

101 show the number of switches ( $N_{sw}$ ) needed to generate the same number of voltage levels ( $N_l$ ) in the

102 output for the different topologies in symmetric and asymmetric mode respectively. In symmetric

103 mode (Fig. 4a), it is obvious that the proposed proposed topology outperforms the 3 other topologies

104 with the lowest switch count for the same voltage level. In asymmetric mode (i.e., Fig. ??, however,

105 the proposed topology fares better at lower voltage levels ( $N_l \leq 50$ ), but this advantage diminishes at

106 higher voltage levels.

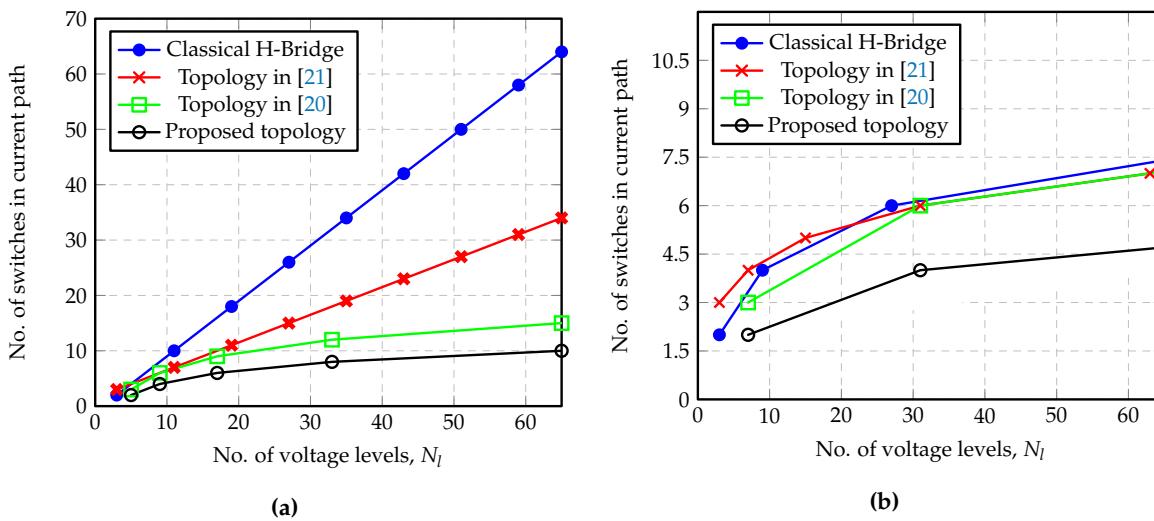

#### 107 3.2. Number of semiconductors in current path

108 Unlike in deal cases when we assume a switch or diode can turn-on or turn-off instantaneously

109 without any power loss, real semiconductor switches have a finite switching transition time. This finite

110 transition period is accompanied by power losses transients [22]. Hence, the less number of switches

111 required to produce a voltage level implies less power losses. Fig. 5a and Fig. 5b show the number of

112 switches in the current path for the same voltage levels for the different topologies in symmetric and

113 asymmetric mode respectively. The proposed topology performs better than in both modes resulting

114 in higher efficiency at every voltage level.

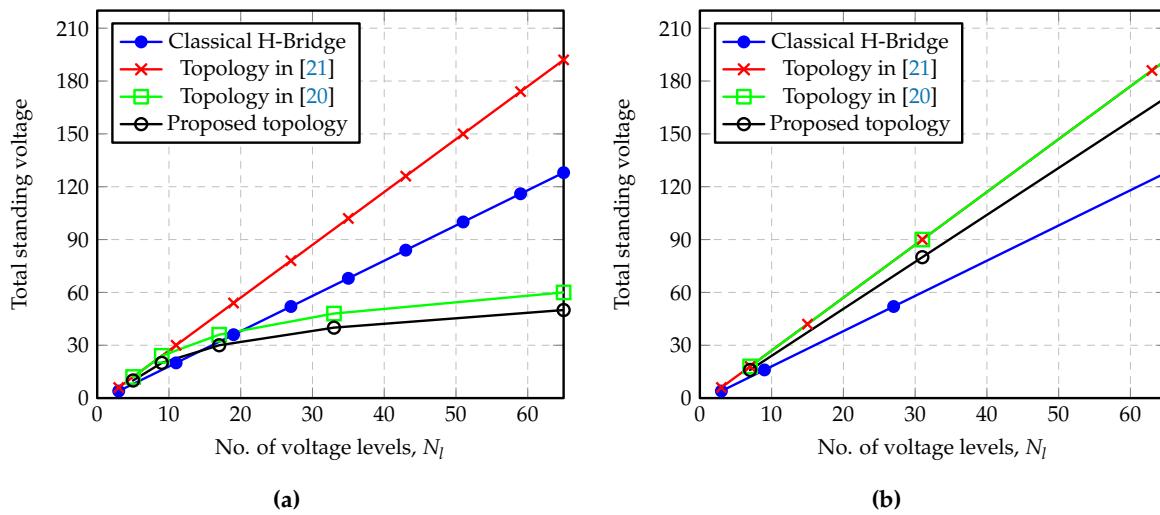

#### 115 3.3. Total standing voltage

116 Another important factor that should be taken into consideration when comparing the topologies

117 is the minimum voltage rating of the switches. This minimum voltage rating, which will influence on

118 the price and size of the switches, is related to the voltage stress that they need to handle in blocking

119 state. This is also called standing voltage and the total standing voltage is obtained by addition of the

120 blocking voltage requirement of each switch of a topology.

121 For comparison purposes, a value of 1V was assumed for  $V_{dc}$ . Fig. 6a and Fig. 6b show the total

122 standing voltage in symmetric and asymmetric modes respectively for all the topologies. In both

123 symmetric and asymmetric modes, it can be shown that the proposed topology outperforms all others

124 topologies.

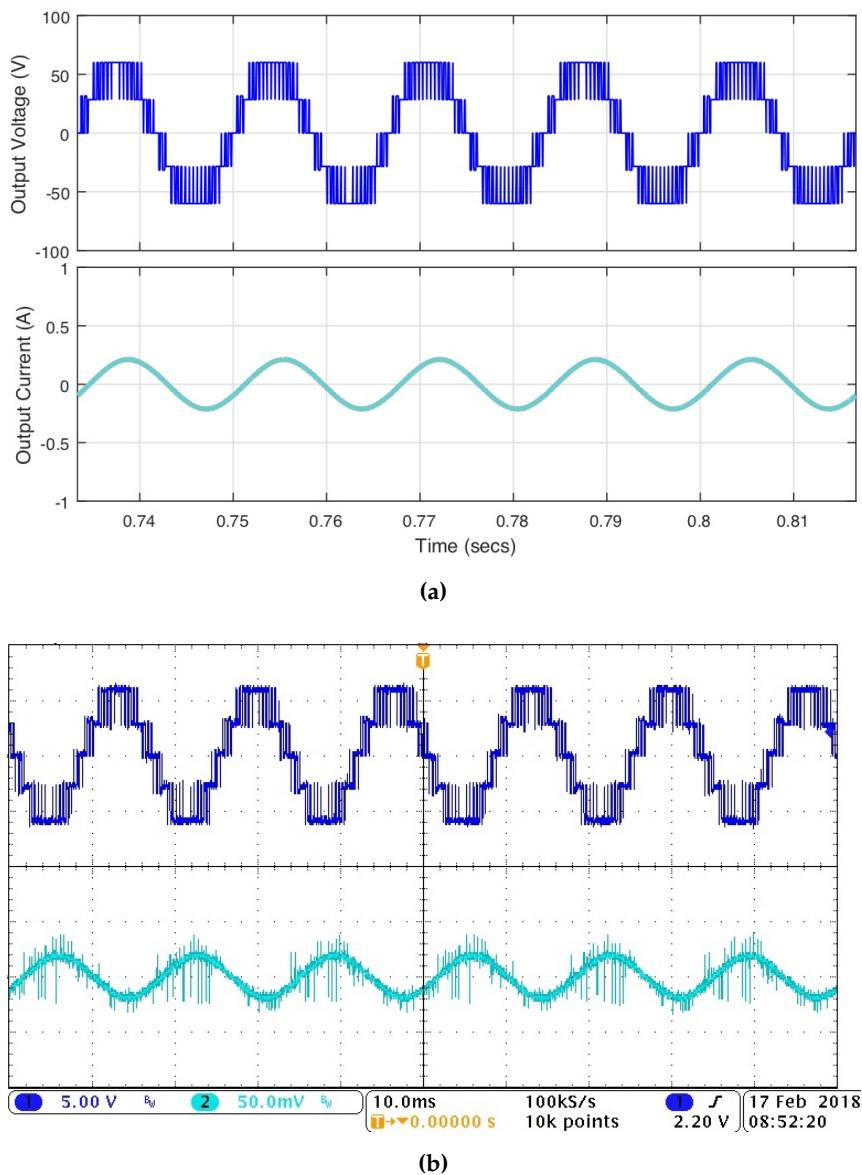

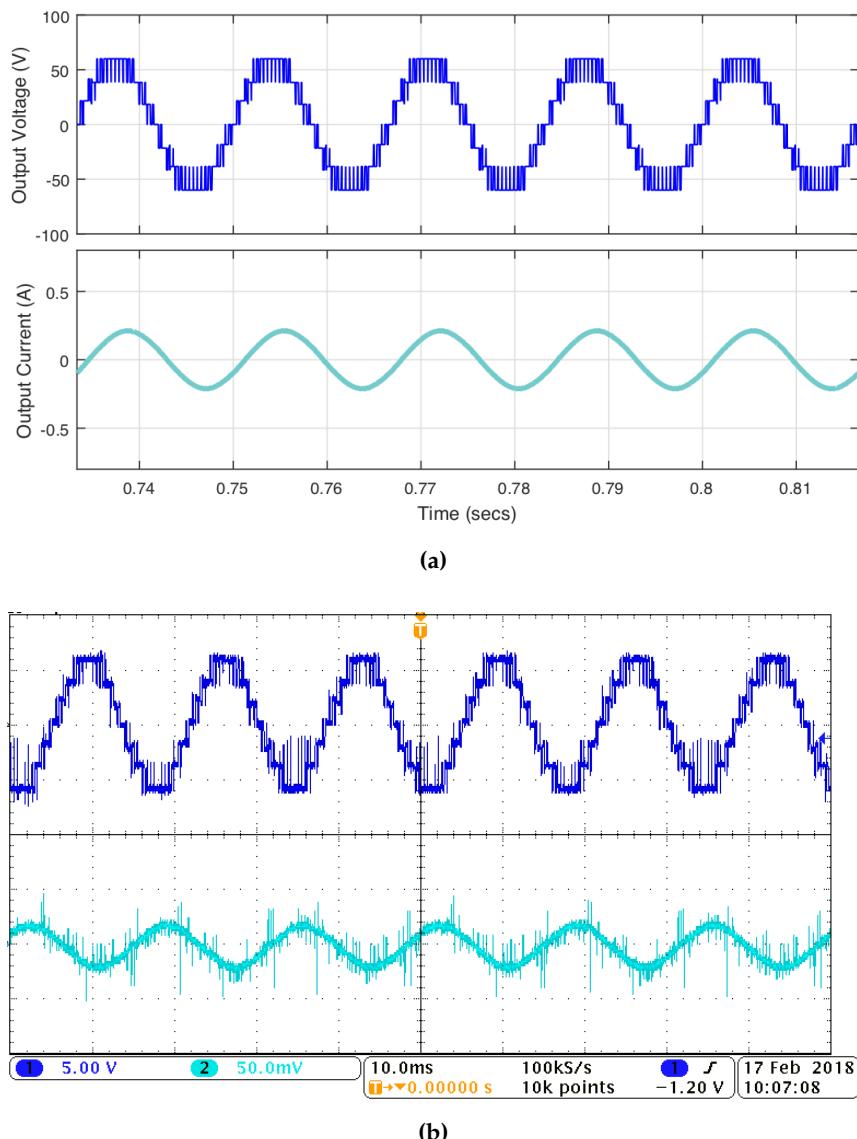

### 125 4. Simulation and Experimental Results

126 Fig 7 shows a laboratory prototype built to validate the proposed topology. Simulations were

127 carried out using MATLAB/Simulink. The semiconductor switches are IGBT IXGN120N60A3D1 with

128 voltage and current ratings of 600 V, 120 A, respectively. The gate control signals were implemented

129 using OPAL-RT OP5700 RCP/HIL FPGA-based Real-time Simulator. Two low power DC sources were

130 engaged in supplying the required voltages. Table 2 list specifications of the inverter used for both

131 simulations and experiment.

132 Fig. 8a shows the simulation results of the converter output voltage and load current waveforms

133 the 5-level (symmetrical) operation. The THD of the voltage and current waveforms are 28.08% and

134 1.46%, respectively. The corresponding experimental waveforms for the symmetrical operations are

135 shown in Fig. 8b. The experimental waveforms confirm accurate 5-level output voltage, having a

136 current waveform with small THD. The results of the asymmetrical operation (7-level) are presented in

**Table 2.** Parameters for 7-level and 31-level simulations.

| Parameter                  | Value                           |

|----------------------------|---------------------------------|

| Frequency $f$              | 60 Hz                           |

| Switching Frequency $f_s$  | 2340 Hz                         |

| Modulation Index $m_a$     | 0.95                            |

| DC power sources (5-level) | $V_1 = 30 V$ $V_2 = 30 V$       |

| DC power sources (7-level) | $V_1 = 40 V$ $V_2 = 20 V$       |

| Load                       | $R = 250 \Omega$ ; $L = 350 mH$ |

137 Fig. 9. Fig. 9a) show simulated voltage and current waveforms whilst Fig. 9b present the corresponding

138 experimental waveforms. The THD of the voltage and current waveforms for the 7-level operation

139 are 19.00% and 1.13%, respectively. As in the case of the symmetrical operation, the experimental

140 waveforms confirm accurate 7-level output voltage, with an almost sinusoidal current waveform. The

141 presented results clearly verify the feasibility of the proposed inverter topology.

## 142 5. Conclusions

143 In this paper, a new topology for switched-source multilevel inverter (SS MLI) has been proposed.

144 The structure and principle of operation are discussed and validated by both theoretical simulations

145 and experiments. The basic unit can operate in symmetric and asymmetric modes. The new SS MLI

146 topology is compared to three similar SS MLI topologies in terms of the number of switches required

147 to generate a voltage level, the number of switches in current path (power losses) and total standing

148 voltage the switches need to handle. The proposed topology outperforms the other topologies in most

149 of the scenarios, presenting a significant reduction on the total cost and size of the unit, as well as

150 a reduction in power losses. MATLAB/Simulink simulations and experiments using a laboratory

151 prototype are presented for 5- and 7-level operations.

152 **Acknowledgments:** The authors acknowledge with thanks to Will Mefford who produced the PCB and built most

153 parts of the multilevel inverter prototype.

154 **Author Contributions:** Cristopher Luciano and Kennedy Aganah conceived and designed the experiments;

155 Cristopher Luciano performed the experiments; Cristopher Luciano, Kennedy Aganah and Mandoye Ndoye

156 wrote the paper; Gregory Murphy contributed supplies/simulation tools;

157 **Conflicts of Interest:** The authors declare no conflict of interest.

158

- 159 1. Krug, D.; Busse, S.; Beuermann, M. Complete performance test of MV drive with modular multilevel

160 topology for high power oil & gas applications. Petroleum and Chemical Industry Technical Conference

161 (PCIC), 2016. IEEE, 2016, pp. 1–6.

- 162 2. Ma, K.; Blaabjerg, F. Modulation methods for neutral-point-clamped wind power converter achieving loss

163 and thermal redistribution under low-voltage ride-through. *IEEE Transactions on Industrial Electronics* **2014**,

164 61, 835–845.

- 165 3. Wang, J.; Gao, Y.; Weidong, J. A Carrier-Based Implementation of Virtual Space Vector Modulation for

166 Neutral Point Clamped Three-Level Inverter. *IEEE Transactions on Industrial Electronics* **2017**.

- 167 4. Shimmyo, S.; Mochikawa, H.; Morishima, Y. Development of high power density converter using

168 flying capacitor multilevel circuits for PV systems. Electrical Machines and Systems (ICEMS), 2016 19th

169 International Conference on. IEEE, 2016, pp. 1–6.

- 170 5. Lei, Y.; Barth, C.; Qin, S.; Liu, W.C.; Moon, I.; Stillwell, A.; Chou, D.; Foulkes, T.; Ye, Z.; Liao, Z.; others.

171 A 2 kW, Single-Phase, 7-Level Flying Capacitor Multilevel Inverter with an Active Energy Buffer. *IEEE*

172 *Transactions on Power Electronics* **2017**.

- 173 6. Babaie, E.; Laali, S.; Alilu, S. Cascaded multilevel inverter with series connection of novel H-bridge basic

174 units. *IEEE Transactions on Industrial Electronics* **2014**, 61, 6664–6671.

175 7. Babaei, E.; Laali, S.; Bayat, Z. A single-phase cascaded multilevel inverter based on a new basic unit with

176 reduced number of power switches. *IEEE Transactions on industrial electronics* **2015**, *62*, 922–929.

177 8. Fazel, S.S.; Bernet, S.; Krug, D.; Jalili, K. Design and comparison of 4-kV neutral-point-clamped,

178 flying-capacitor, and series-connected H-bridge multilevel converters. *IEEE Transactions on Industry

179 Applications* **2007**, *43*, 1032–1040.

180 9. Naderi, R.; Smedley, K. A new hybrid active neutral point clamped flying capacitor multilevel inverter.

181 Applied Power Electronics Conference and Exposition (APEC), 2015 IEEE. IEEE, 2015, pp. 794–798.

182 10. Naderi, R.; Rahmati, A. Phase-Shifted Carrier PWM Technique for General Cascaded Inverters. *IEEE

183 Transactions on Power Electronics* **2008**, *23*, 1257–1269.

184 11. Mohan, D.; Kurub, S.B. A comparative analysis of multi carrier SPWM control strategies using fifteen level

185 cascaded H-bridge multilevel inverter. *International Journal of Computer Applications* **2012**, *41*.

186 12. du Toit Mouton, H. Natural balancing of three-level neutral-point-clamped PWM inverters. *IEEE

187 transactions on industrial electronics* **2002**, *49*, 1017–1025.

188 13. Choi, H.; Zhao, W.; Ciobotaru, M.; Agelidis, V.G. Large-scale PV system based on the multiphase

189 isolated dc/dc converter. Power Electronics for Distributed Generation Systems (PEDG), 2012 3rd IEEE

190 International Symposium on. IEEE, 2012, pp. 801–807.

191 14. Villanueva, E.; Correa, P.; Rodríguez, J.; Pacas, M. Control of a single-phase cascaded H-bridge

192 multilevel inverter for grid-connected photovoltaic systems. *IEEE Transactions on Industrial Electronics* **2009**,

193 *56*, 4399–4406.

194 15. Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-balanced Step-up Multilevel Inverter based on

195 Switched-Capacitor Structure. *IEEE Transactions on Power Electronics* **2017**.

196 16. Barzegarkhoo, R.; Kojabadi, H.M.; Zamiry, E.; Vosoughi, N.; Chang, L. Generalized structure for a single

197 phase switched-capacitor multilevel inverter using a new multiple dc link producer with reduced number

198 of switches. *IEEE Transactions on Power Electronics* **2016**, *31*, 5604–5617.

199 17. Chinnaiyan, V.K.; Shanmugam, P.K.; others. A Multilevel Inverter topology using Single Source and

200 Double Source Module with reduced Power Electronic Components. *The Journal of Engineering* **2017**, *1*.

201 18. Banaei, M.; Salary, E. Asymmetric Cascaded Multi-level Inverter: A Solution to Obtain High Number of

202 Voltage Levels. *Journal of Electrical Engineering and Technology* **2013**, *8*, 316–325.

203 19. Xiao, M.; Xu, Q.; Ouyang, H. An Improved Modulation Strategy Combining Phase Shifted PWM and

204 Phase Disposition PWM for Cascaded H-Bridge Inverters. *Energies* **2017**, *10*, 1327.

205 20. Ahmed, B.; Aganah, K.A.; Ndoye, M.; Arif, M.A.; Luciano, C.; Murphy, G.V. Single-phase cascaded

206 multilevel inverter topology for distributed DC sources. Ubiquitous Computing, Electronics and Mobile

207 Communication Conference (UEMCON), 2017 IEEE 8th Annual. IEEE, 2017, pp. 514–519.

208 21. Babaei, E.; Hosseini, S.H. New cascaded multilevel inverter topology with minimum number of switches.

209 *Energy Conversion and Management* **2009**, *50*, 2761–2767.

210 22. Lakkas, G. MOSFET power losses and how they affect power-supply efficiency. *Analog Applications* **2016**.

**Figure 3.** Structure of the proposed topology as standalone.

**Figure 4.** Number of switches vs. output voltage levels of proposed inverter compared with 3 other topologies in (a) symmetric mode and (b) asymmetric mode.

**Figure 5.** Number of switches in current path vs. output voltage level of proposed inverter compared with 3 other topologies in (a) symmetric mode and (b) asymmetric mode.

**Figure 6.** Total standing voltage vs. output voltage levels of proposed inverter compared with 3 other topologies in (a) symmetric mode and (b) asymmetric mode.

**Figure 7.** Picture of experimental test set-up

**Figure 8.** Results of 5-level SSMLI: (a) Simulated output voltage (top) and load current (b) experimental output voltage (top, 25V/div ) and current (bottom, 0.25 A/div).

**Figure 9.** Results of 7-level SSMLI: (a) Simulated output voltage (top) and load current (b) experimental output voltage (top, 25V/div) and load current (bottom, 0.25A/div).