1 Article

# 2 Fully solution-processable fabrication of

# 3 multi-layered circuits on flexible substrate using laser

- 4 Seok Young Ji<sup>1, 2</sup>, Wonsuk Choi<sup>2, 3</sup>, Hoon-Young Kim<sup>2, 3</sup>, Jin-Woo Jeon<sup>3</sup>, Sung-Hak Cho<sup>2, 3</sup> and Won Seok Chang<sup>1, 2,\*</sup>

- Department of Nano Mechanics, Nanomechanical Systems Research Division, Korea Institute of Machinery and Materials, 156 Gajeongbuk-Ro, Yuseong-Gu, Daejeon 34103, Republic of Korea

- Department of Nano-Mechatronics, Korea University of Science and Technology (UST), 217 Gajeong-Ro,

Yuseong-Gu, Daejeon 34113, Republic of Korea

- Department of Laser & Electron Beam Application, KIMM, Korea Institute of Machinery and Material, 156

Gajeongbuk-Ro, Yuseong-Gu, Daejeon 34103, Korea

- 12 \* Corresponding Author: paul@kimm.re.kr; Tel.: +82-42-868-7134

Abstract: The development of printing technologies has enabled the realization of electric circuit fabrication on flexible substrate. However, the current technique remains restricted to single-layer patterning. In this paper, we demonstrate a fully solution-processable patterning approach for multi-layer circuits using a combined method of laser sintering and ablation. Selective laser sintering of silver (Ag) nanoparticle-based ink is applied to make conductive patterns on a heat-sensitive substrate and insulating layer. The laser beam path and irradiation fluence are controlled to create circuit patterns for flexible electronics. Microvia drilling using femtosecond laser through the polyvinylphenol-film insulating layer by laser ablation, as well as sequential coating of Ag ink and laser sintering, achieves an interlayer interconnection between multi-layer circuits. The dimension of microvia is determined by a sophisticated adjustment of laser focal position and intensity. Based on these methods, the flexible electronic circuit with chip-size-package light-emitting diodes was successfully fabricated and demonstrated with functional operations.

Keywords: Interconnection, multi-layer patterning, laser sintering, femtosecond laser ablation

26 27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

13

14

15

16

17

18

19

20

21

22

23

24

25

### 1. Introduction

Functional-ink-based printing technology has greatly advanced in recent years for use with flexible electronics [1,2]. Printing techniques, such as micro-contact (μ-contact) [2–4], inkjet [5–8], screen [9,10], flexography [11,12] and gravure [13–15] approaches, have made it possible to fabricate conductive patterns in large areas at a reasonable cost. As printing technologies have matured, electronic applications, such as resistor-capacitor circuits [16], radio frequency identification [17], sensors [18], displays [19], organic field-effect transistors [20,21], and solar cells [22], have been reported. However, these techniques support only single-layer circuit printing and are thus not well suited for the manufacturing of multi-layer circuits. Multi-layer circuit manufacturing is desirable because it not only reduces the circuit routing complexity, but it also enables fabrication of integrated circuits (IC) [23-26]. Moreover, multi-layer circuit fabrication requires stacking of single-layer circuits and hole creation for interconnecting layer-to-layer. Previous studies suggested an interconnection method by dry etching [23,24], which is slow, expensive, and harmful to the environment. Another approach is to use a drilling mechanism that employs a hole opener [26]. This method consumes a small amount of energy and enables interconnection in a short time. Nevertheless, it is only available for the fabrication of double-sided circuits, and it is difficult to implement miniaturization of electronic device because the minimum via-hole size is 500 μm.

44 45

46

In this study, we developed a fully solution-processable fabrication process for the multi-layer circuit on flexible substrate using a combined method of selective laser sintering (SLS) and ablation (SLA). SLS with double irradiation enables low-temperature metal patterning without damaging the heat-sensitive substrate [27]. The double irradiation method uses a higher laser power than the single irradiation method to fabricate electrodes with high conductivity on heat-sensitive substrates. In addition, we introduced femtosecond laser-based SLA through a polyvinylphenol (PVP) insulator to create microvias for interconnections between layers. For ablating insulating layers without damaging the bottom electrode, we investigated the correlation between a femtosecond laser and materials such as sintered Ag electrode and PVP insulating layer. The laser-based process was managed by the optimized conditions of laser fluence and focal position to achieve a suitable microvia diameter and depth. A multi-layered flexible electric circuit was constructed using the suggested process and operated with assembly of chip-size-package light-emitting diodes (LEDs) for process verification.

#### 2. Materials and Methods

61 2.1 Experimental setup

47

48

49

50

51

52

53

54

55

56

57

58

59

60

71

81

- A continuous wave (CW) laser (mpc6000, Ventus) was implemented for the SLS, which has a

- maximum power of 1.6 W, power stability of <0.4% rms, and beam size of 1.5  $\pm$  0.1 mm. A galvano

- 64 scanner (intelliSCAN®10, SCANLAB) was used for the laser beam scanning. It has a maximum

- making speed of 3.0 m/s, scan area of  $45 \times 45$  mm<sup>2</sup>, scan angle of  $\pm 22$  degrees, and nonlinearity of < 3.5

- 66 mrad. The SLA source was the second harmonic 515 nm femtosecond Yb:KGW laser from Light

- 67 Conversion (Pharos SP), which has a maximum power of 6 W, pulse duration of 190 fs, maximum

- pulse energy of >1.0 mJ, and beam quality of TEM00; M2 <1.3. The laser beams were focused at a

- 69 normal incidence onto the insulating layer by a single x50 infinity corrected objective lens with a the

- 70 numerical aperture (NA) of 0.42.

- 72 2.2 Materials and preparation

- 73 For this study, commercially available conductive ink and insulating layer were applied. The silver

- 74 (Ag) nanoparticle (NP) inks were from Harima Chemicals, Inc. (NPS-J) and had Ag particles of a 12

- 75 nm mean diameter and metal content of 65%. The poly (vinylphenol) (PVP) and methylated poly

- 76 (melamine-co-formaldehyde) (MMF) for the polymer insulator layer were purchased from

- 77 Sigma-Aldrich and used without further purification. The PVP-MMF solution (PVP : MMF = 1 : 1.25)

- 78 was dissolved in propylene glycol monomethyl ether acetate (PGMEA) at a solid concentration of

- 79 100 mg/ml. These solutions were then filtered through a 0.45 µm polytetrafluoroethylene syringe

- 80 filter before deposition by spin-coating.

- 82 2.3 Multi-layer patterning process

- 83 Figure 1 shows a detailed multi-layer patterning process flow. First, the bottom pattern was

- prepared by SLS on PI substrate, as shown in Figure 1(a-c). The Ag NP ink was spin-coated onto the

- PI substrate, followed by pre-drying in ambient conditions on a hot plate at 70°C to stop the flow of

- the Ag NP ink (Figure 1(a)). The thickness of the Ag NP ink films before sintering was ~70 nm. The

- 87 prepared Ag NP film was selectively sintered by a scanning laser beam with a Galvano scanner to

- draw the desired patterns (Figure 1(b)). Then, the un-sintered Ag NPs were simply washed away

- with the solvent (toluene) to reveal the metal patterns (Figure 1(c)).

To remove the remaining impurities and increase the surface energy, the substrates with patterns were sequentially cleaned in an ultrasonic bath with deionized water and 2-propanol for 10 min each. The PVP solution was spin-coated onto the cleaned substrates, followed by pre-baking at 120 °C for 10 min and inducing thermal cross-linking at 220 °C for 60 min (Figure 1(d)). The thickness of the PVP polymer insulator films was ~500 nm. Next, the insulator film was selectively ablated using the femtosecond laser (Figure 1(e)). The laser sintering method was sequentially applied to form the top patterns and interconnection between the top and bottom circuit (Figure 1(f)).

Ag ink deposition

Selective laser irradiation

Cleaning with solvent

Laser sintering method

Laser sintering

Selective ablation

Selective ablation

(d)

Figure 1. Schematic of the multi-layer patterning process using selective laser sintering and ablation

## 3. Results

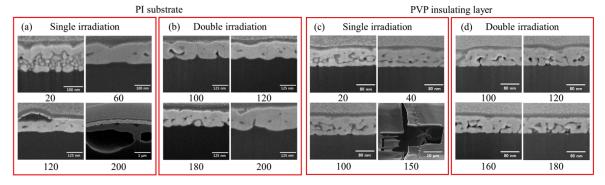

To fabricate the multi-layer circuit, conductive patterns and the interconnection between layers must be achieved on the heat-sensitive substrate without thermal damage. Figure 2 shows cross-sectional scanning electron microscope (SEM) images of patterns using laser sintering at various laser powers using the single irradiation method (Figure 2(a), (c)) and double irradiation method (Figure 2(b), (d)) on the PI substrate and PVP insulating layer. The Ag NPs show a high-energy absorption rate at a wavelength of 532 nm [31], which enables surface sintering features even at a low laser power of 10 mW. The patterns fabricated with a laser power of 40 mW or lower show surface sintering; however, the interior ink of the pattern is not completely sintered. Thus, it was detached or damaged during the cleaning process due to insufficient adhesion of the partially sintered Ag layer with the substrate.

A higher laser power should give a higher electric conductivity and adhesion of sintered Ag NP film than lower ones because of the incomplete coalescence of Ag nanoparticles and the diminished electron scattering [28–30]. However, when we induced a high laser power for obtaining high electric conductivity, portions of the patterns incurred defects and burning effects because the higher laser power directly irradiated the heat-sensitive substrate through the Ag NP layer. It thus influenced the pattern conditions, such as conductivity and roughness. To circumvent this problem, we used a double laser sintering method, which involved two processes: first, irradiation using a low laser power was performed on Ag NP films to pre-sinter the surface layer,

called surface-sintering (SS); second, the un-sintered interior ink was post-sintered by the high laser power, called complete-sintering (CS).

In the SS step, a low (less than 20 mW) laser power successfully sintered the surface layer, which preserved the heat-sensitive substrate by the following high-power laser irradiation. When we irradiated with the high-power laser in the CS step, the interior Ag NP layer of the pattern was sintered by vertical heat conduction. The substrates remained unaffected by the direct laser irradiation on account of the surface layer sintered in the previous SS step.

Figure 2(b) shows optical images of the patterns using the double irradiation method. For this method, we employed 20 mW of laser power in the SS step and varied the laser power in the CS step. It was confirmed that the pattern was fabricated without damage in the conditions with the high laser-power, which usually caused defects in the single irradiation method as shown in Figure 2(a), (c). Nevertheless, some patterns incurred defects owing to the excessive vertical heat conduction, which affected the substrate in the CS step (laser power of 250 mW and 200 mW on the PI substrate and PVP insulating layer, respectively (Figure S1(b) and S2(b)).

**Figure 2.** Cross-sectional SEM images of Ag electrode sintered by (a), (c) single and (b), (d) double laser irradiation with different power on PI substrate and PVP insulating layer. The numbers underneath the SEM image indicate laser power.

To verify the patterns condition when irradiating with various laser powers, we measured the conductivity for the three process conditions: single laser irradiation, double irradiation with pre-sintering at a laser power of 10, and the latter approach at a laser power of 20 mW. The laser power was adjusted from 60 mW to 250 mW because the pattern fabricated with less than 40 mW was partially detached during the cleaning process. We attempted an experiment on PI substrate (Figure S3(a)) and PVP insulating layer (Figure S3(b)), respectively. The graphs of laser-power versus conductivity show that the measured conductivity increased as the laser power increased. The trend of increasing conductivity with laser power is readily elucidated by various sintering models [31-34]. It is noted that the Ag NP grain-growth mechanisms upon laser irradiation [31] can explain the high conductivity at a high laser-power; nonetheless, thermal damage was incurred by the printed pattern. The fabricated pattern with SS at 20 mW and CS at 240 mW had the highest conductivity, but it has been confirmed that substrate is damaged by 50 % probability. We selected a laser power that did not damage on the substrate even after 100 repetition test.

Consequentially, we fabricated the pattern with a conductivity of  $6.21 \times 10^5$  S/cm and an rms roughness of  $7.09 \pm 0.5$  nm on PI without damage using the double irradiation method with SS at a laser power of 20 mW and CS at 160 mW. This result was approximate to the conductivity of bulk silver of  $6.3 \times 10^5$  S/cm. On the other hand, the pattern on the PVP layer had slightly lower conductivity of  $4.25 \times 10^5$  S/cm. It is because we induced relatively low laser power of 20 mW and 140 mW for SS and CS, respectively, considering the PVP layer thickness of 500 nm.

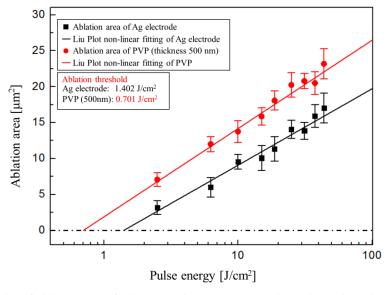

The multi-layer circuit manufacturing includes not only fabrication of conductive patterns on a heat-sensitive substrate, but also an interconnection between layers. Thus, selective laser ablation using femtosecond laser was performed to make microscale via-hole (named "microvia") through the insulating PVP layer without damaging the bottom electrode. We need to know the ablation

threshold of sintered Ag electrode (EAg) and PVP insulating layer (EPVP) for ablating of PVP layers in interconnection region without damage on bottom Ag electrode. The laser fluence would be determined between EPVP and EAg. To determine the ablation thresholds of each material for the complete series of ablation spot, the relevant ablation areas have to be plotted versus laser pulse fluence on a logarithmic scale. Then the ablation threshold of each material can be derived by extrapolating the relationship between laser fluence and the relevant areas on a Liu-plot [31,32]. For this purpose, the objective lens was focused on the surface of the materials, and the relevant ablation area was observed and measured with an optical microscope (OM), while increasing or decreasing laser fluence. The results of this analysis are shown in Figure 3. It is obvious that the value of EPVP (0.701 J/cm²) for ablating the insulating layer is about a half of EAg (1.402 J/cm²). Based on the results, we can fabricate microvia that can be used for interconnection by selected laser fluence (~0.9 J/cm<sup>2</sup>). The microvia diameter ranged from 100 to 10 µm, and the stable minimum diameter was 10 µm. After fabricating the microvia, the Ag NP ink filled the empty microvia space during the spin-coating step of the SLS process. In the laser-sintering step of the top pattern, the laser beam path was specifically modified for the double CS step on the microvia position to increase the heat penetration depth.

**Figure 3.** Liu-plot of ablation areas for laser irradiation on sintered Ag electrode and PVP insulating layer. The value of ablation threshold has been extracted from experimental results. (Liu-plot non-linear fitting).

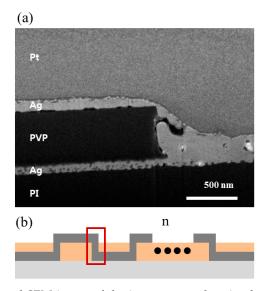

Figure 4(a) shows a cross-sectional scanning electron microscopy (SEM) image of the interconnected part between the top and bottom layers. To confirm that the interconnection had consistency on patterns, we measured the resistance of the patterns with a different number of interconnections, as shown in Figure 4(b). Table 1 shows that the resistance has similar values regardless of the number of interconnections. Thus, we could expect that the electric current flow was not affected by the interconnection. Using the multi-layer patterning process with interconnections, more complicated circuits with two or more layers could be fabricated.

**Table 1.** The Measured resistances (mean ± standard deviation) according to the number of interconnections.

| The number of interconnection | Resistance $(\Omega)$ |

|-------------------------------|-----------------------|

| None                          | $12.35 \pm 0.33$      |

| #1                            | $12.37\pm0.42$        |

| #2                            | $12.41\pm0.35$        |

| #3                            | $12.40\pm0.38$        |

| #4                            | $12.43 \pm 0.36$      |

**Figure 4.** (a) Cross-sectional SEM image of the interconnected region between top and bottom Ag electrode. (b) Schematic of cross-sectional sample structure fabricated by SLS and SLA.

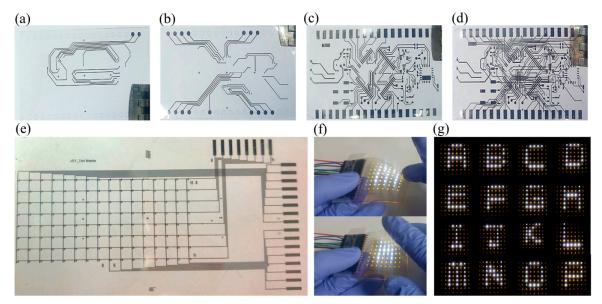

We designed a flexible micro-controller-unit (MCU) circuit with triple layers consisting of a ground circuit on the first layer, a voltage circuit on the second layer, and a main circuit on the third layer. The device circuit has full size of  $25 \times 45$  mm<sup>2</sup> with a line width of 30  $\mu$ m,. Figures 5 (a–c) show the separated patterns of the ground, voltage, and main circuit on the PI, respectively. To achieve a multi-layered circuit on the same substrate, it usually requires a complex etching and deposition process for connecting between layers. We demonstrated that the entire MCU circuit could be fabricated by the multi-layer patterning process on the PI as shown in Figure 5(d).

Finally, we try to manufacture a functional device using the multi-layer patterning process to verify that this process is applicable to flexible applications. As shown in Figure 5(e), the 8 × 16 dot matrix circuit was obtained with a full device size of 45 × 85 mm2, and LED connection pad of 150 × 80 µm2. After patterning the dot matrix circuits, the chip-size-package LEDs were mounted on the prepared circuit. An MCU (Texas Instruments, mpc430), connected using copper wires (diameter ~500 µm), was used to input the signal to the LEDs. As shown in Figure 5(f), the LED operation according to the input signal was well maintained during the bending state, thus demonstrating excellent possibilities for flexible electronic device applications. Figure 5(g) shows the various capital letters (from A to P) represented by the controlled input pins on the dot matrix.

**Figure 5.** Optical photographs of MCU board circuit for (a) ground (first layer), (b) voltage (second layer), (c) main (third layer), and (d) final circuits fabricated by the multi-layer patterning process on the PI substrate. (e) Fabricated dot-matrix circuit using the multi-layer patterning process. (f) Bending test of the fabricated electric device. (g) Expression of various capital letters using LED.

#### 5. Conclusions

Using a combined SLS and SLA method, we developed a fully solution-processable fabrication process for multi-layer patterns on flexible substrate. We verified that the electric resistance of the fabricated patterns was not affected by the number of interconnections. Moreover, to demonstrate that the multi-layer patterning process can be used for flexible applications an electric device circuit with two and three layers was fabricated using this process.

This research provides several guidelines for the study of the laser sintering method on heat-sensitive substrate and the fabrication of multi-layer patterns. In addition, it enables the achievement of a desirable microvia diameter and suitable depth by controlling the laser focus position and intensity to make interconnections. The electric device fabricated with our technology showed successful operation. We expect that the proposed approach can be a key technology for implementing user-designed flexible electronic devices in near future.

**Acknowledgments:** This work was supported by the Center for Advanced Soft-Electronics funded by the Ministry of Science, ICT and Future Planning (CASE-2016M3A6A5929198) Korea, and the Basic Research Fund of Korea Institute of Machinery & Materials (SC1240).

### 245 References

- 1. Gupta, R.; Walia, S.; Hösel, M.; Jensen, J.; Angmo, D.; Krebs, F. C.; Kulkarni, G. U. Solution processed large area fabrication of Ag patterns as electrodes for flexible heaters, electrochromics and organic solar cells. *J.*

- 248 *Mater. Chem. A* **2014**, 2, 10930.

- 249 2. Ko, S. H.; Pan, H.; Grigoropoulos, C. P.; Fréchet, J. M. J.; Luscombe, C. K.; Poulikakos, D. Lithography-free

- high-resolution organic transistor arrays on polymer substrate by low energy selective laser ablation of

- inkjet-printed nanoparticle film. *Appl. Phys. A Mater. Sci. Process.* **2008**, 92, 579–587.

- 252 3. Loo, Y.; Someya, T.; Baldwin, K. W.; Bao, Z.; Ho, P.; Dodabalapur, A.; Katz, H. E.; Rogers, J. A. Soft,

- $253 \hspace{1cm} \text{conformable electrical contacts for organic semiconductors: high-resolution plastic circuits by lamination.} \\$

- 254 *Proc. Natl. Acad. Sci. U. S. A.* **2002**, 99, 10252–6.

- 255 4. Zaumseil, J.; Someya, T.; Bao, Z.; Loo, Y. L.; Cirelli, R.; Rogers, J. A. Nanoscale organic transistors that use

- source/drain electrodes supported by high resolution rubber stamps. *Appl. Phys. Lett.* **2003**, *82*, 793–795.

- 5. Chung, S.; Jang, M.; Ji, S. B.; Im, H.; Seong, N.; Ha, J.; Kwon, S. K.; Kim, Y. H.; Yang, H.; Hong, Y. Flexible

- high-performance all-inkjet-printed inverters: Organo-compatible and stable interface engineering. *Adv.*

- 259 *Mater.* **2013**, 25, 4773–4777.

- 260 6. Chen, S.; Su, M.; Zhang, C.; Gao, M.; Bao, B.; Yang, Q.; Su, B.; Song, Y. Fabrication of Nanoscale Circuits on Inkjet-Printing Patterned Substrates. *Adv. Mater.* **2015**, 27, 3928–3933.

- 7. Yu, P.-C.; Hong, C.-C.; Liou, T.-M. Bendable transparent conductive meshes based on multi-layer inkjet-printed silver patterns. *J. Micromechanics Microengineering* **2016**, *26*, 35012.

- 8. Jeong, J. A.; Kim, J.; Kim, H. K. Ag grid/ITO hybrid transparent electrodes prepared by inkjet printing. *Sol.*

- 265 Energy Mater. Sol. Cells **2011**, 95, 1974–1978.

- 9. Bao, Z. N.; Feng, Y.; Dodabalapur, A.; Raju, V. R.; Lovinger, A. J. High-performance plastic transistors fabricated by printing techniques. *Chem. Mater.* **1997**, *9*, 1299.

- 268 10. Garnier, F.; Hajlaoui, R.; Yassar, A.; Srivastava, P. All-Polymer Field-Effect Transistor Realized by Printing Techniques. *Science* (80-. ). **1994**, 265, 1684–1686.

- 270 11. Leppäniemi, J.; Huttunen, O. H.; Majumdar, H.; Alastalo, A. Flexography-Printed In2O3 Semiconductor

- 271 Layers for High-Mobility Thin-Film Transistors on Flexible Plastic Substrate. Adv. Mater. 2015, 27,

- 272 7168–7175.

- 273 12. Furukawa, T.; Kawamura, N.; Inoue, J.; Nakada, H.; Koden, M. OLED Lighting Devices Fabricated by

- 274 Flexography Printing of Silver Nanowire and Conducting Polymer Tadahiro Furukawa \*, Norifumi

- 275 Kawamura \*, Junichi Inoue \*\*, Hitoshi Nakada \*, and Mitsuhiro Koden \*. 2015, 1355–1358.

- 276 13. Koo, H.; Lee, W.; Choi, Y.; Sun, J.; Bak, J.; Noh, J.; Subramanian, V.; Azuma, Y.; Majima, Y.; Cho, G.

- 277 Scalability of carbon-nanotube-based thin film transistors for flexible electronic devices manufactured

- using an all roll-to-roll gravure printing system. Sci. Rep. 2015, 5, 14459.

- 279 14. Shin, K. H.; Nguyen, H. A. D.; Park, J.; Shin, D.; Lee, D. Roll-to-roll gravure printing of thick-film silver electrode micropatterns for flexible printed circuit board. *J. Coatings Technol. Res.* **2017**, *14*, 95–106.

- 281 15. Park, J.; Lee, J.; Park, S.; Shin, K. H.; Lee, D. Development of hybrid process for double-side flexible printed

- 282 circuit boards using roll-to-roll gravure printing, via-hole printing, and electroless plating. *Int. J. Adv.*

- 283 Manuf. Technol. 2016, 82, 1921–1931.

- 284 16. Kurra, N.; Dutta, D.; Kulkarni, G. U. Field effect transistors and RC filters from pencil-trace on paper. *Phys.*

- 285 Chem. Chem. Phys. 2013, 15, 8367.

- 286 17. Komoda, N.; Nogi, M.; Suganuma, K.; Kohno, K.; Akiyama, Y.; Otsuka, K. Printed silver nanowire

- antennas with low signal loss at high-frequency radio. *Nanoscale* **2012**, *4*, 3148.

- 288 18. Radha, B.; Sagade, A. A.; Kulkarni, G. U. Flexible and semitransparent strain sensors based on micromolded Pd nanoparticle-carbon??-stripes. *ACS Appl. Mater. Interfaces* **2011**, *3*, 2173–2178.

- 290 19. Sandström, A.; Dam, H. F.; Krebs, F. C.; Edman, L. Ambient fabrication of flexible and large-area organic light-emitting devices using slot-die coating. *Nat. Commun.* **2012**, *3*, 1002.

- 292 20. Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* **2004**, 432, 488–492.

- 295 21. Kwon, J.; Kyung, S.; Yoon, S.; Kim, J. J.; Jung, S. Solution-processed vertically stacked complementary organic circuits with inkjet-printed routing. *Adv. Sci.* **2015**, *3*, 1–6.

- Sommer-Larsen, P.; Jørgensen, M.; Søndergaard, R. R.; Hösel, M.; Krebs, F. C. It is all in the

Pattern—High-Efficiency Power Extraction from Polymer Solar Cells through High-Voltage Serial

Connection. Energy Technol. 2013, 1, 15–19.

- 300 23. Kutchoukov, V. G.; Shikida, M.; Mollinger, J. R.; Bossche, a Through-wafer interconnect technology for silicon. *J. Micromechanics Microengineering* **2004**, *14*, 1029–1036.

- Zhuang, X.; Ergun, A. S.; Huang, Y.; Wygant, I. O.; Oralkan, O.; Khuri-Yakub, B. T. Integration of

trench-isolated through-wafer interconnects with 2d capacitive micromachined ultrasonic transducer

arrays. Sensors Actuators, A Phys. 2007, 138, 221–229.

- 305 25. Ji, C.-H.; Herrault, F.; Allen, M. G. A metallic buried interconnect process for through-wafer interconnection. *J. Micromechanics Microengineering* **2008**, *18*, 85016.

- Ta, T. Interconnection and Double Layer for Flexible Electronic Circuit with Instant Inkjet Circuits.

Proceedings of the 2015 ACM International Joint Conference on Pervasive and Ubiquitous Computing, ACM 2015,

181–190.

- 310 27. Young, S.; Tea, W.; Noh, Y.; Seok, W. Laser Sintering of Silver Nanoparticle for Flexible Electronics. *Journal* 311 of the Korean Society of Manufacturing Technology Engineers 2015, 1, 135–139.

- 312 28. Mayadas, A. F.; Shatzkes, M. Electrical-resistivity model for polycrystalline films: The case of arbitrary reflection at external surfaces. *Phys. Rev. B* **1970**, *1*, 1382–1389.

- 314 29. Greer, J. R.; Street, R. A. Thermal cure effects on electrical performance of nanoparticle silver inks. *Acta* 315 *Mater.* **2007**, *55*, 6345–6349.

- 31. Pan, H.; Ko, S. H.; Grigoropoulos, C. P. The Solid-State Neck Growth Mechanisms in Low Energy Laser

31. Sintering of Gold Nanoparticles: A Molecular Dynamics Simulation Study. *J. Heat Transfer* **2008**, 130,

318 92404.

- 31. Liu, J. M. Simple technique for measurements of pulsed Gaussian-beam spot sizes. Opt. Lett. 1982, 7, 196.

- 32. Liu, J. M.; Yen, R.; Kurz, H.; Bloembergen, N. Phase transformation on and charged particle emission from a silicon crystal surface, induced by picosecond laser pulses. *Appl. Phys. Lett.* **1981**, *39*, 755–757.