Peer-reviewed version available at Energies 2016, 9, 799; doi:10.3390/en9100799

Article

# Design and Optimization of an Efficient (96.1%) and Compact (2 kW/dm<sup>3</sup>) Bidirectional Isolated Single-Phase Dual Active Bridge Ac–Dc Converter

## **Jordi Everts**

Department of Electrical Engineering, Electromechanics and Power Electronics (EPE) group, Eindhoven University of Technology (TU/e), 5600 MB Eindhoven (Postbox 513), The Netherlands; j.everts@tue.nl

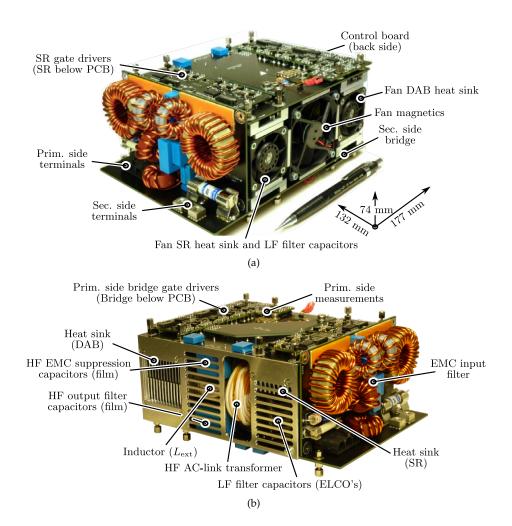

**Abstract:** The growing attention for plug-in electric vehicles, and the associated high-performance demands, have initiated a development trend towards highly efficient and compact on-board battery chargers. These isolated ac-dc converters are most commonly realized using two conversion stages, combining a non-isolated power factor correction (PFC) rectifier with an isolated dc-dc converter. This, however, involves two loss stages and a relatively high component count, limiting the achievable efficiency and power density and resulting in high costs. In this paper a single-stage converter approach is analyzed to realize a single-phase ac-dc converter, combining all functionalities into one conversion stage and thus enabling a cost-effective efficiency and power density increase. The converter topology consists of a quasi-lossless synchronous rectifier followed by an isolated dual active bridge (DAB) dc-dc converter, putting a small filter capacitor in between. To show the performance potential of this bidirectional, isolated ac-dc converter, a comprehensive design procedure and multi-objective optimization with respect to efficiency and power density is presented, using detailed loss and volume models. The models and procedures are verified by a 3.7 kW hardware demonstrator, interfacing a 400 V dc-bus with the single-phase 230 V, 50 Hz utility grid. Measurement results indicate a state-of-the-art efficiency of 96.1% and power density of 2 kW/dm<sup>3</sup>, confirming the competitiveness of the investigated single-stage DAB ac–dc converter.

**Keywords:** ac–dc power converters; battery chargers; dual active bridge; DAB; optimal design; power MOSFETs; single-stage

## 1. Introduction

## 1.1. Overview and Objectives

Single-phase utility-interfaced ac–dc converters with power factor correction (PFC) and galvanic isolation cover a wide range of applications such as chargers for plug-in hybrid electrical vehicles (PHEVs) and battery electric vehicles (BEVs) [1,2], interfaces for residential dc distribution systems and energy storage systems [3,4], and inverters for photovoltaic modules. Bidirectional power flow is increasingly required since the traditional electricity grid is evolving towards a smart interactive service network (customers/operators) in which energy systems play an active role in providing different types of support to the grid [5], e.g. vehicle-to-grid (V2G) concepts [6].

The above mentioned isolated ac–dc converters are most commonly realized using a dual-stage (2-S) approach, involving a non-isolated power factor correction (PFC) rectifier, followed by a dc-link to which a high-frequency (HF) isolated dc–dc converter is connected. An extensive review of uniand bidirectional single-phase PFC rectifier topologies with improved power quality is presented in [7], including some variants with galvanic isolation. Examples of soft-switched, single-phase, non-isolated, bidirectional PFC rectifiers are the boost-type PFC with passive snubber cell presented in [8] and the multi-cell totem-pole PFC described in [9,10], which employs a triangular current mode (TCM) modulation scheme. Extensive overviews, topology surveys, analyses, and comparative evaluations of common topologies used for the isolated dc–dc converter stage are presented in [11–18], inter alia including numerous (soft-switching) dual active bridge (DAB) topologies and

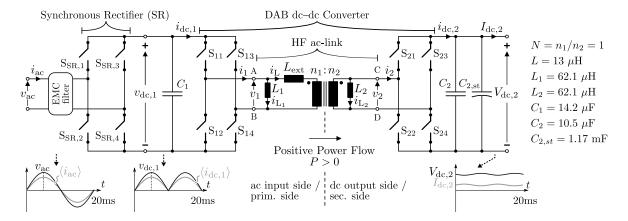

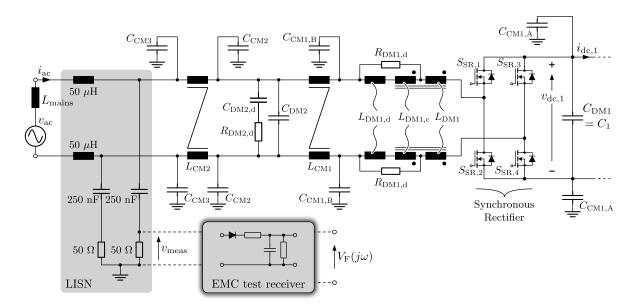

**Figure 1.** Schematic of the single-stage (1-S), single-phase, bidirectional, isolated DAB ac–dc converter topology. The nominal ac input voltage, input current, and power are respectively 230  $V_{rms}$ , 16  $A_{rms}$ , and 3.7 kW, while the specified output voltage range is  $V_{dc,2} = 370 - 470$  V, with  $V_{dc,2,nom} = 400$  V.

resonant topologies, whether or not combined with active auxiliary snubber circuits and/or a second, typically hard-switched and non-isolated, dc-dc conversion stage.

Besides the 2-S approach, several single-stage (1-S), single-phase, isolated ac-dc PFC converter topologies have been proposed in literature, which combine all functionalities into one conversion stage and thus (potentially) enable a cost-effective efficiency and power density increase through the omission of a complete loss stage and through reduction of the component count. Moreover, due to the absence of an intermediate dc-link there is no need anymore for bulky, failure-prone electrolytic capacitors. This, however, is at the expense of an increased filtering effort at the dc output side due to the double line-frequency (i.e. 100 Hz) power pulsation that is seen by the output, where large low-frequency (LF) filter capacitors are required in case a low output voltage ripple is desired. An example of a 1-S, single-phase, bidirectional, isolated ac-dc converter is presented in [19,20], using a cyclo-converter at the primary side and a voltage source converter at the secondary side of a medium frequency transformer. Another well known example is the 1-S DAB ac-dc converter topology analyzed in [21–27], which is able to effectively obtain PFC while producing high-quality waveforms and complying to regulations on low- and high-frequency distortions of the mains ac power lines. The topology is shown in Figure 1 and is the subject of this paper. It consists of a quasi-lossless synchronous rectifier (SR) and an isolated full-bridge full-bridge DAB dc-dc converter, putting a small HF filter capacitor in between. Moreover, using advanced modulation schemes such as the one recently presented in [25], the DAB can be operated with minimum HF circulating currents and under full-operating-range zero voltage switching (ZVS) conditions, quasi completely eliminating the losses associated with the switching of the, in the case of this paper, MOSFET-type power switches.

Whether or not used in a 1-S ac–dc converter, previous research on DAB converters mainly has been focusing on the improvement of modulation schemes in order to facilitate increased converter efficiency and/or power density, e.g. as in [25,28]. This paper, on the other hand, presents a comprehensive design procedure and multi-objective optimization with respect to efficiency and power density, in particular for the 1-S, single-phase DAB ac–dc converter topology shown in Figure 1. Thereby it aims to show and prove the performance potential of this promising 1-S architecture, and the competitiveness with 2-S topologies [29], and therefore complements previous publications on DAB converters. The operating conditions and converter specifications for the investigated ac–dc converter are summarized in Table 1 and are based on the requirements for future on-board electric vehicle battery chargers, interfacing the high-voltage battery (400 V) of the vehicle with the single-phase utility grid (230  $V_{rms}$ , 50 Hz). The nominal ac input current of the converter is 16  $A_{rms}$ , allowing domestic charging/discharging at a nominal power of 3.7 kW. Bidirectional power flow enables V2G functionality, while galvanic isolation ensures safety. The converter needs to have

Table 1. Operating Conditions and Converter Specifications

| Property       |                                         | Value                                                  |

|----------------|-----------------------------------------|--------------------------------------------------------|

|                | V <sub>ac</sub> (V <sub>rms</sub> )     | 230 (nominal)                                          |

| ac-side        |                                         | $207 \leqslant V_{\rm ac} \leqslant 253$               |

| ис-зис         | I <sub>ac,nom</sub> (A <sub>rms</sub> ) | 16 (nominal)                                           |

|                | f <sub>L</sub> (Hz)                     | 50                                                     |

| dc-side        | $V_{\text{dc,2}}\left(V\right)$         | $370 \leqslant V_{\rm dc,2} \leqslant 470$             |

| EMC compliance |                                         | CISPR 22 Class B                                       |

| PF             |                                         | $> 0.9$ (at $I_{ac} \geqslant 0.1 \cdot I_{ac,nom}$ )  |

| THD            |                                         | IEC 61000-3-2 standard, and                            |

|                | IIID                                    | THD $\leq$ 5% (at $I_{ac} \geq 0.3 \cdot I_{ac,nom}$ ) |

| Additional requirements                                      |   |

|--------------------------------------------------------------|---|

| Galvanic isolation                                           |   |

| Bidirectional power flow capability                          |   |

| • High conversion efficiency ( $\eta > 94\%$                 | ) |

| within reasonable power range)                               |   |

| • High power density ( $\rho \geqslant 2 \text{ kW/liter}$ ) | ) |

| Autonomous air cooling                                       |   |

| MOSFET-type power switches                                   |   |

a very high conversion efficiency and power density, high power factor (PF), and low total harmonic distortion (THD) of the ac input current while complying to the CISPR 22 Class B standard for EMC.

#### 1.2. Outline

At first, in Section 2 the general operating principle of the 1-S DAB ac–dc converter and the operating conditions of the DAB dc–dc converter, as core building block, are presented. Next, in Section 3 the operating principle, available modulation parameters, and relevant switching modes of the DAB are detailed and the method used for calculating an efficient full-operating-range ZVS modulation scheme is summarized. The selection of the high-level circuit variables such as the switching frequency, the inductance values, and the transformer's turns ratio is outlined as well. Based on the available degrees of freedom in the design of the 1-S DAB ac–dc converter, in Section 4 the modeling of the losses and volumes of the employed components is discussed and the corresponding optimization results are presented. Subsequently, in Section 5 the designed hardware demonstrator is shown and its performance, i.e. in terms of losses (& efficiency) and volume (& power density), is calculated. In order to verify the optimization results, different measurement results are presented in Section 6. Finally, conclusions are drawn in Section 7.

## 2. General Operating Principle of the 1-S DAB Ac-Dc Converter

The investigated single-stage (1-S), single-phase ac–dc converter topology shown in Figure 1 consists of a synchronous rectifier (SR) and isolated full-bridge full-bridge dual active bridge (DAB) dc–dc converter as the core building block, putting a small high-frequency (HF) filter capacitor  $C_1$  in between. Also shown in Figure 1 are the principle current and voltage waveforms at the different converter ports. The SR switches at each zero-crossing of the ac line voltage  $v_{\rm ac}$ , folding it into a dc voltage  $v_{\rm dc,1}$  that varies according to the absolute value of  $v_{\rm ac}$ , i.e. at twice the 50 Hz line frequency (2 ·  $f_{\rm L}$ ), and that is directly fed to the input of the DAB dc–dc converter:

$$v_{\rm dc,1} = |v_{\rm ac}| = |\hat{V}_{\rm ac}\sin(\omega_{\rm L}t)|, \tag{1}$$

where  $\hat{V}_{ac}$  is the amplitude of  $v_{ac}$  and  $\omega_L = 2 \pi f_L$ . The DAB performs the PFC by actively shaping the switching-cycle averaged value  $\langle i_{dc,1} \rangle$  of its input current  $i_{dc,1}$  in phase with  $v_{dc,1}$ :

$$\langle i_{\text{dc},1} \rangle = dir \cdot |\hat{I}_{\text{ac}}^* \cdot \sin(\omega_{\text{L}} t)|,$$

(2)

where  $\hat{I}_{ac}^*$  (=  $\sqrt{2} I_{ac}^*$ ) is the amplitude set-point of ac input current  $i_{ac}$  and dir the power flow direction in accordance to Figure 1:

$$dir = \begin{cases} 1 & \text{if } P > 0 : \text{prim. side} \to \text{sec. side,} \\ -1 & \text{if } P < 0 : \text{sec. side} \to \text{prim. side.} \end{cases}$$

(3)

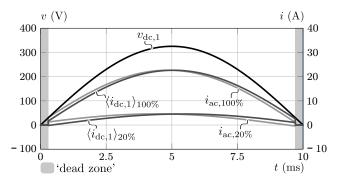

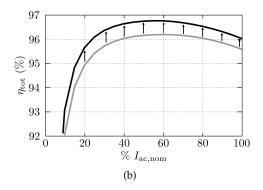

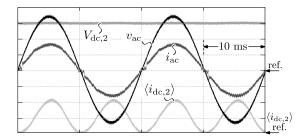

Since the differential mode (DM) EMC input filter capacitance  $C_{\rm DM}$  (see Section 4.4.1), which includes capacitor  $C_1$ , draws a small reactive current from the grid, this current should be compensated in order to achieve unity power factor. This is done by controlling  $\langle i_{\rm dc,1} \rangle$  slightly lagging on  $v_{\rm dc,1}$ , as can be seen in Figure 2 which depicts  $v_{\rm dc,1}$ ,  $v_{\rm dc,1}$ ,  $v_{\rm dc,1}$ , within a 10 ms half period of the grid voltage  $v_{\rm ac}$  for ac line current values of  $I_{\rm ac}^* = I_{\rm ac,nom} = 16~{\rm A_{rms}}$  and  $I_{\rm ac}^* = 0.2 \cdot I_{\rm ac,nom} = 3.2~{\rm A_{rms}}$ . These currents respectively correspond to 100% and 20% of the nominal ac input power of 3.7 kW. The exact control equation for  $\langle i_{\rm dc,1} \rangle$ , which compensates for  $C_{\rm DM}$ , is given by Eq. (2) of [25] and is not shown here for brevity of this paper. For the same reason, in the following only positive power flow operation (P > 0) is discussed as, due to symmetry, the analysis and results for negative power flow are identical.

**Figure 2.** Ideal ac input-side quantities  $v_{\text{dc},1}$ ,  $i_{\text{ac}}$ , and  $\langle i_{\text{dc},1} \rangle$  within a 10 ms half period of the grid voltage  $v_{\text{ac}}$  for  $I_{\text{ac}} = I_{\text{ac,nom}} = 16 \text{ A}_{\text{rms}}$  (100% power) and  $I_{\text{ac}} = 0.2 \cdot I_{\text{ac,nom}} = 3.2 \text{ A}_{\text{rms}}$  (20% power).

## 3. Optimal Zero Voltage Switching (ZVS) Operation of the DAB Dc-Dc converter

#### 3.1. Operating Principle, Available Modulation Parameters, and Relevant Switching Modes

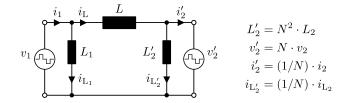

Control of the switching-cycle averaged DAB input current  $\langle i_{\rm dc,1} \rangle$  according to (2) can be done by proper modulation of the full bridges ( $S_{11...14}$  and  $S_{21...24}$ ) of the DAB dc-dc converter [] (see Figure 1). Thereby, the bridges produce phase-shifted edge-resonant square wave voltages  $v_1$  and  $v_2$  at the terminals of a HF ac-link. This link consists of a HF transformer (ratio  $N=n_1/n_2$ ) and external series inductor  $L_{\rm ext}$ . Also included in the ac-link are, so called, commutation inductances  $L_1$  and  $L_2$  which 'inject' relatively small, purely reactive currents into the bridges of the DAB, enhancing the commutation of the bridge legs without contributing to the power flow. In [25] and [26] they have been shown to be essential elements for achieving full-operating-range ZVS of the DAB with smooth modulation parameter trajectories. On the assumption of ideal components, the DAB can be represented by the primary-side referred equivalent model shown in Figure 3, where the main energy transfer inductance L consists of external inductance  $L_{\rm ext}$  combined with the leakage inductances  $L_{\sigma 1}$  and  $L_{\sigma 2}$  (not shown in Figure 1) of the transformer:

$$L = L_{\text{ext}} + L_{\sigma 1} + N^2 \cdot L_{\sigma 2}. \tag{4}$$

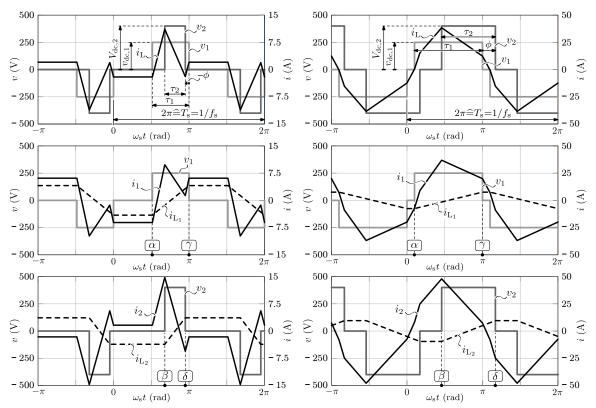

Figure 4, which depicts general waveforms of  $v_1$  and  $v_2$  for the two most appropriate switching modes, i.e. low-power mode 1 and high-power mode 2, for positive power flow of the DAB, defines the parameters available to modulate these voltages, being the phase-shift angle  $\phi$  between  $v_1$  and  $v_2$ , the respective pulse-width modulation angles  $\tau_1$  and  $\tau_2$ , and the switching frequency  $f_s$ . As in the following it is assumed that the switching frequency value/pattern is predefined (see Section 3.3),

Note that around the zero crossing ( $-30 \text{ V} \leqslant v_{ac} \leqslant 30 \text{ V}$ ) the bridges of the DAB are inactive ('dead zone') as zero voltage switching (ZVS) power conversion is quasi impossible when the input voltage of the DAB is close to zero [25].

Figure 3. Simplified (lossless), primary-side referred equivalent model of the DAB dc-dc converter.

- (a) Switching mode 1; low input current/power intervals.

- (b) Switching mode 2; high input current/power intervals.

Figure 4. Ideal HF ac-link voltage/current waveforms for (a) mode 1 and (b) mode 2, being derived using:  $v_{\rm dc,1}=250$  V,  $V_{\rm dc,2}=400$  V, and  $f_{\rm s}=120$  kHz. For mode 1 the selected modulation parameters are:  $\tau_1 = 1.53$  rad.,  $\tau_2 = 0.85$  rad.,  $\phi = -0.16$  rad., resulting in  $\langle i_{dc,1} \rangle = 2$  A. For mode 2 the selected modulation parameters are:  $\tau_1=2.83$  rad.,  $\tau_2=2.24$  rad.,  $\phi=0.54$  rad., resulting in  $\langle i_{dc,1}\rangle=22$  A.

this results in a total of three 'free' modulation parameters:  $\mathbf{x} = \{\phi, \tau_1, \tau_2\}$ . The respective inductor currents, induced by voltages  $v_1$  and  $v_2$ , are also shown in Figure 4, whereby:

$$\frac{di_{L}(t)}{dt} = \frac{v_{1}(t) - Nv_{2}(t)}{L}, \quad (5) \qquad \frac{di_{L_{1}}(t)}{dt} = \frac{v_{1}(t)}{L_{1}}, \quad (6) \qquad \frac{di_{L_{2}}(t)}{dt} = \frac{v_{2}(t)}{L_{2}}. \quad (7)$$

$i_{L_1}$  and  $i_{L_2}$ , induced in commutation inductances  $L_1$  and  $L_2$ , are the purely reactive currents that are 'injected' into the bridges of the DAB. As a result, the bridge currents  $i_1$  and  $i_2$  are calculated as:

$$i_1 = i_L + i_{L_1},$$

(8)  $i_2 = N i_L - i_{L_2}.$

Both active bridges of the DAB act as ac-dc converters towards their respective dc side, transforming bridge currents  $i_1$  and  $i_2$  into net dc currents  $i_{dc,1}$  and  $i_{dc,2}$ . Filter capacitors  $C_1$  and  $C_2$  bypass the HF components of  $i_{dc,1}$  and  $i_{dc,2}$ . The dc component of  $i_{dc,1}$  is thus the mentioned switching-cycle averaged DAB input current  $\langle i_{dc,1} \rangle$ , which is calculated by averaging  $i_{dc,1}$  over one HF switching period  $T_s = 1/f_s$ , e.g. at a random instant  $kT_s$ :

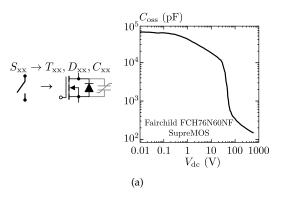

**Figure 5.** (a) Characteristic of the non-linear parasitic output capacitance of the used FAIRCHILD FCH76N60NF MOSFETs. (b) Charge required to charge/discharge the MOSFET's non-linear parasitic output capacitance  $C_{\rm oss}$  from 0 V to  $V_{\rm dc}$  (or vice versa) during commutation of a bridge leg.

$$\langle i_{dc,1} \rangle = \frac{1}{T_s} \int_{kT_s}^{(k+1)T_s} i_{dc,1}(t) dt.$$

(10)

Equations for  $\langle i_{dc,1} \rangle$ , regarding the two switching modes of Figure 4, can be found in [25].

## 3.2. Efficient ZVS Modulation Scheme

The method used to calculate an efficient, full-operating-range ZVS modulation scheme for the DAB is presented in [25]. It is based on a constrained numerical optimization algorithm that calculated the modulation parameters  $\mathbf{x} = \{\phi, \tau_1, \tau_2\}$  in each DAB operating point  $\{\langle i_{\text{dc},1} \rangle, v_{\text{dc},1}, V_{\text{dc},2} \rangle$  based on a given switching frequency  $f_{\text{s}}$  ( $v_{\text{dc},1}$ ) and given circuit variables  $\mathbf{h} = \{L, L_1, L_2, N\}$  (see next section). Through this algorithm, in each DAB operating point the most appropriate switching mode, i.e. mode 1 or mode 2 of Figure 4, is automatically selected. The resulting modulation scheme leads to quasi-lossless ZVS operation at near-minimum rms values of the HF bridge currents  $i_1$  and  $i_2$  and thus minimum conduction losses. Thereby, ZVS at all switching instants<sup>2</sup>  $\theta_{\mathbf{i}} = \{\alpha, \beta, \gamma, \delta\}$  of the DAB, which are defined in Figure 4, is ensured through incorporation of the charge  $Q_{\text{req}}(V_{\text{dc}})$  that is required to charge/discharge the MOSFETs' non-linear parasitic output capacitances  $C_{\text{oss}}$  from 0 V to the corresponding dc-bus voltage  $V_{\text{dc}}$  (or vice versa) during commutation of the respective bridge legs.  $Q_{\text{req}}(V_{\text{dc}})$  for the used MOSFETs<sup>3</sup> is depicted in Figure 5(b), which is calculated using the characteristic of  $C_{\text{oss}}$  that is given in the data-sheet of the devices and shown in Figure 5(a):

$$Q_{\text{req}}(V_{\text{dc}}) = \int_{0}^{V_{\text{dc}}} 2 C_{\text{oss}}(v) d(v).$$

(11)

For the primary-side active bridge (index 'p') this charge is function of the DAB's input voltage and is denoted  $Q_{\text{req,p}}(v_{\text{dc,1}})$ . For the secondary-side active bridge (index 's') this charge is function of the DAB's output voltage and is denoted  $Q_{\text{req,s}}(V_{\text{dc,2}})$ .

<sup>&</sup>lt;sup>2</sup> In Figure 4, switching instants  $\alpha$  and  $\beta$  correspond with the positive rising edge of respectively  $v_1$  and  $v_2$  while  $\gamma$  and  $\delta$  correspond with the respective positive falling edges. Consequently, the primary-side active bridge switches at  $\theta_i = \{\alpha, \gamma\}$ , while the secondary-side active bridge switches at  $\theta_i = \{\beta, \delta\}$ .

The selection of the FAIRCHILD FCH76N60NF MOSFETs for the DAB is further detailed in Section 4.1.1.

#### 3.3. Selection of Circuit Variables

## 3.3.1. Switching Frequency $f_s(v_{dc,1})$

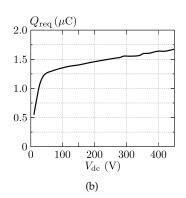

A nominal switching frequency of  $f_{\rm s,nom}=120~{\rm kHz}$  is selected to accommodate a compact converter design without causing excessive switching frequency related losses. Moreover, thermal limitations apply at high switching frequencies, resulting in an increased total converter volume. The frequency of 120 kHz is chosen to stay well below these thermal limits. Furthermore, it has been been shown in [25] that at both ends of the 10 ms half mains period, where the DAB input voltage  $v_{\rm dc,1}$  is low (see Figure 2), it is beneficial to linearly reduce  $f_{\rm s}$ . In these regions, ZVS is hard to achieve without making commutation inductances  $L_1$  and  $L_2$  very small, which would result in unacceptably high circulating currents and thus a low conversion efficiency. This has led to the following predefined switching frequency pattern (see also Figure 6(a) of Section 3.4):

$$f_{\rm s} ({\rm Hz}) = \begin{cases} 120\,000 & \text{if } v_{\rm dc,1} \geqslant 150\,{\rm V}, \\ 75\,000 + 375\cdot (v_{\rm dc,1} - 30) & \text{if } v_{\rm dc,1} < 150\,{\rm V}. \end{cases}$$

(12)

## 3.3.2. Transformer Turns Ratio N

A good design rule is to determine the turns ratio  $N = n_1/n_2$  of the HF transformer such that  $(N V_{\rm dc,2,min}) > (v_{\rm dc,1,max} + 10 \text{ V})$  [25]. Given the in- and output voltage range of the DAB converter, where  $V_{\rm dc,2,min} = 370 \text{ V}$  and  $v_{\rm dc,1,max} = \hat{v}_{\rm ac} = 358 \text{ V}$ , this results in:

$$N > \left(\frac{v_{\rm dc,1,max} + 10}{V_{\rm dc,2,min}} = 0.9946\right) \rightarrow N = 1.$$

(13)

## 3.3.3. Main Energy Transfer Inductance L

The maximum achievable DAB input current  $\langle i_{\text{dc,1,max}} \rangle$  is obtained at  $\tau_1 = \tau_2 = \pi$  and  $\phi = \pi/2$ , mode 2, and is given by  $\langle i_{\text{dc,1,max}} \rangle = N \, V_{\text{dc,2}} / (8 \, f_{\text{s}} \, L)$  [25]. This maximum current needs to be higher than the peak value of the ac input current at maximum power, which equal to  $\hat{i}_{\text{ac}}$  (=  $\sqrt{2} \, I_{\text{ac,nom}} = \sqrt{2} \cdot 16 \approx 23$  A). Therefore, the maximum allowable inductance value  $L_{\text{max}}$  is determined by:

$$L_{\text{max}} = \frac{N V_{\text{dc,2,min}}}{8 f_{\text{s}} \langle i_{\text{dc,1,max}} \rangle} = \frac{1 \cdot 370}{8 \cdot 120000 \cdot 23} = 16.7 \ \mu\text{H}. \tag{14}$$

A good design guideline is to choose the value L in the range  $L \approx (0.75 \dots 0.85) \cdot L_{\text{max}}$  [25], leaving sufficient margin for control purposes. This yields the final design value of  $L = 13 \, \mu\text{H}$ .

## 3.3.4. Commutation Inductances $L_1$ and $L_2$

As mentioned in Section 3.3.1, there is a strong correlation between the lower value of  $f_s$  (i.e. at low  $v_{\rm dc,1}$ ) and the maximum allowed values of commutation inductances  $L_1$  and  $L_2$ . Determination of these values requires some iteration. Assuming  $L_1$ = $L_2$ , the highest value for  $L_1$  and  $L_2$  that leads to full-operating-range ZVS, i.e. regarding the switching frequency pattern given by (12), has been found to be  $L_1 = L_2 = 62.1~\mu\text{H}$ , which is also the final design value.

## 3.4. Simulation Results

Figure 6 illustrates the relevant simulation results that are obtained using the constrained numerical optimization algorithm presented in [25] for a run through a half-cycle (i.e.  $T_{\rm L}/2 = 1/(2\,f_{\rm L}) = 10$  ms) of the nominal ac input voltage ( $V_{\rm ac} = 230~V_{\rm rms}$ , 50 Hz) at the nominal ac input current of  $I_{\rm ac} = 16~A_{\rm rms}$  (positive power flow) and the nominal dc output voltage of  $V_{\rm dc,2} = 400~V$ . Note that the values applied for  $\langle i_{\rm dc,1} \rangle$  correspond with line  $\langle i_{\rm dc,1} \rangle_{100\%}$  in Fig 2. The used circuit variables  $\mathbf{h} = \{L, L_1, L_2, N\}$  are derived in the previous section and are listed in the right inset of Figure 1 while the predefined switching frequency pattern  $f_{\rm s}(v_{\rm dc,1})$  is given by (12) and shown in

**Figure 6.** Resulting value trajectories of several quantities calculated for a half cycle of the nominal ac input voltage ( $V_{ac} = 230 \text{ V}_{rms}$ , 50 Hz) at the nominal ac input current of  $I_{ac} = 16 \text{ A}_{rms}$  (positive power flow) and the nominal dc output voltage of  $V_{dc,2} = 400 \text{ V}$ .

Figure 6(a). The modulation parameters  $\mathbf{x} = \{\phi, \tau_1, \tau_2\}$  that result from the simulation are shown in Figure 6(b), expectedly comprising only switching modes 1 and 2. From Figures 6(c) and 6(d) it can be seen that the available commutation charges  $Q_{\alpha,A/B}$  and  $Q_{\delta,A/B}$  at the two most critical switching instants  $\theta_{\mathbf{i}} = \{\alpha, \delta\}$  are higher than or equal to the minimum required commutation charges for achieving ZVS, i.e. respectively  $Q_{\text{req},p}$  (primary-side active bridge) and  $Q_{\text{req},s}$  (secondary-side active bridge). The same goes for the available commutation charges at the non-critical switching instants  $\theta_{\mathbf{i}} = \{\beta, \gamma\}$  which are not shown for brevity. This means that ZVS of all the semiconductor devices is guaranteed in all operating points of the simulation run.

## 4. Modeling and Optimization of the Main Functional Elements

Based on the ZVS modulation scheme, the switching frequency pattern  $f_s(v_{dc,1})$ , and circuit variables  $\mathbf{h} = \{L, L_1, L_2, N\}$  derived in Section 3, in this section the main functional elements of the 1-S DAB ac–dc converter are designed and optimized. Each sub-section is dedicated to the design of the individual elements, combining state-of-the art design methods/procedures, models for the component losses, and volume models with custom developed component-level optimization algorithms in order to obtain a high-efficiency and high-power-density converter design that is in compliance with the system requirements specified in Table 1. This implies separation of the partial converter functions and omission of outer optimization loops, i.e. with regard to the circuit level variables and the switching frequency.

#### 4.1. Semiconductors and Heat Sinks

#### 4.1.1. Semiconductor Selection

Each full-bridge of the DAB consists of four HF-switched MOSFETs, requiring characteristics that enable an excellent (soft-) switching performance and low conduction losses. The FCH76N60NF (FAIRCHILD) SupreMOS® high-voltage super-junction MOSFETs are selected, showing:

- A highly non-linear, not too big, parasitic output capacitance  $C_{oss}$ , enabling ZVS turn-off and turn-on. The  $C_{oss}$  characteristic of the FCH76N60NF MOSFETs is shown in Figure 5(a);

- A low drain to source on-resistance  $R_{DS(on)}$  and a low junction to case thermal resistance  $R_{th,J-C}$ , being beneficial regarding the DAB's conduction losses;

- A low total gate charge  $Q_g$ , leading to reduced turn-on and turn-off times, improved ZVS behavior (fast turn-off) [30], and reduced gate drive losses;

- An integrated fast body diode with low reverse recovery charge  $Q_{rr}$  and low reverse recovery time  $t_{rr}$ , ensuring that all the energy will timely leave the transistor after a ZVS commutation.

Of main importance for the four LF-switched MOSFETs of the SR are the characteristics that enable a reduction of the SR's conduction losses, being a low on-resistance  $R_{\rm DS(on)}$  and low junction to case thermal resistance  $R_{\rm th,J-C}$ . The switching-performance related characteristics are of less importance since the SR's MOSFETs only change state two times per mains period. The STY112N65M5 (ST Microelectronics) MDmesh<sup>TM</sup> V power MOSFETs are chosen. Table A.1 of Appendix A.1 lists the most relevant device parameters of both the FCH76N60NF and the STY112N65M5 MOSFETs.

#### 4.1.2. Loss Models

Since the modulation scheme derived in Section 3.2 results in full-operating-range ZVS of the DAB, switching losses can be neglected in the analysis [10,28]. Therefore, only conduction losses and the losses of the gate drive units are considered. For the SR also the gate drive losses can be neglected as the MOSFETs of the SR are low-frequency switched (100 Hz).

**Conduction losses:** The conduction losses of a MOSFET are proportional to the drain to source on-resistance  $R_{DS(on)}$  and to the squared RMS value of the conducted current<sup>4</sup>. Assuming a negligible junction temperature change within a full line cycle  $T_L$ , the equivalent, line-cycle averaged conduction losses  $P_{S,eq,c}$  of a single MOSFET are determined by:

$$P_{\text{S,eq,c}} = R_{\text{DS(on)}} \cdot I_{\text{S,eq'}}^2$$

(15) with:  $I_{\text{S,eq}} = \sqrt{\frac{1}{T_L} \int_0^{T_L} I_{\text{S}}(t) dt}$ . (16)

$I_{\rm S}$  is the local, switching-cycle averaged RMS value of the current conducted by the switch under consideration, and is used in (16) to calculate the equivalent, line-cycle averaged RMS value  $I_{\rm S,eq}$ . In steady-state, each switch of the DAB conducts during half a switching cycle  $T_{\rm s}/2$ . As a result,  $I_{\rm S,eq}$  for the switches of both active bridges are determined by:

$$I_{S_{S11-14},eq} = \sqrt{\frac{1}{T_L} \int_0^{T_L} \frac{I_1(t)}{\sqrt{2}} dt}, \qquad (17) \qquad I_{S_{S21-24},eq} = \sqrt{\frac{1}{T_L} \int_0^{T_L} \frac{I_2(t)}{\sqrt{2}} dt}. \qquad (18)$$

$I_1$  and  $I_2$  are the switching-cycle averaged RMS values of bridge currents  $i_1$  and  $i_2$ . Each SR switch conducts during half a mains period  $T_L$ . Assuming that the HF components of the DAB input current  $i_{dc,1}$  are bypassed by HF filter capacitance  $C_1$ , for each SR switch  $I_{S,eq}$  can be approximated as:

$$I_{\rm S_{SR1-4},eq} \approx \frac{I_{\rm ac}}{\sqrt{2} \cdot \rm PF}.$$

(19)

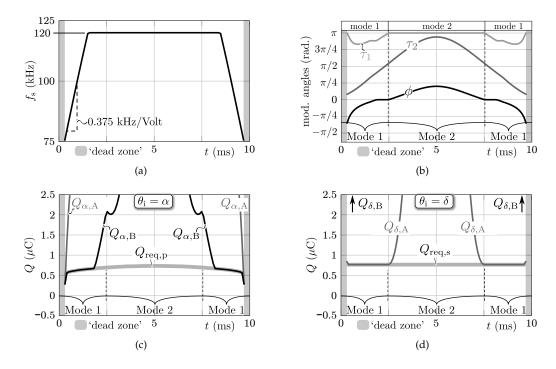

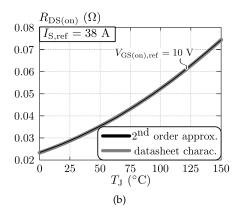

To calculate the resulting conduction losses using (15)-(19), the dependency of the MOSFET's on-resistance on the junction temperature  $T_{\rm J}$  and on the switch current  $I_{\rm S}$  has to be modeled. Figure 7 depicts these dependencies for the FCH76N60NF MOSFETs. The datasheet characteristics (gray lines) can be described by a 2<sup>nd</sup> order approximation<sup>5</sup> (black lines) according to:

<sup>&</sup>lt;sup>4</sup> The conduction losses of the internal body diodes can be neglected as they only conduct current during a very small interval of the switching period *T*<sub>s</sub>.

<sup>&</sup>lt;sup>5</sup> Similarly, a 2<sup>nd</sup> order approximation can be used to describe the characteristics of the SR's STY112N65M5 MOSFETs.

**Figure 7.** Dependency of the on-resistance  $R_{DS(on)}$  on (a) the switch current  $I_S$  and (b) the junction temperature  $T_{I_J}$  regarding the FAIRCHILD FCH76N60NF MOSFETs.

$$R_{\text{DS(on)}}(T_{\text{J}}) \mid_{I_{\text{S,ref}},V_{\text{GS(on),ref}}} = a_0 + a_1 T_{\text{J,eq}} + a_2 T_{\text{J,eq}}^2$$

(20)

$$R_{\rm DS(on)}(I_{\rm S})\mid_{T_{\rm J,ref},V_{\rm GS(on),ref}} = b_0 + b_1 I_{\rm S,eq} + b_2 I_{\rm S,eq}^2$$

(21)

where the equivalent, line-cycle averaged RMS values  $I_{S,eq}$  for the switches of active bridge 1, active bridge 2, and the SR are respectively given by (17), (18), and (19).  $T_{J,eq}$  is the equivalent, line-cycle averaged junction temperature of the switch under consideration:

$$T_{\rm J,eq} = \sqrt{\frac{1}{T_{\rm L}}} \int_0^{T_{\rm L}} T_{\rm J}(t) \, \mathrm{d}t,$$

(22)

which is calculated using the thermal network model that will be presented in Section 4.1.3. The coefficients ( $a_0$ ,  $a_1$ ,  $a_2$  and  $b_0$ ,  $b_1$ ,  $b_2$ ) required to evaluate (20) and (21) for both used MOSFET types are given in Table A.2 of Appendix A.1 where  $T_{\rm J,ref}$ ,  $I_{\rm D,ref}$ , and  $V_{\rm GS(on),ref}$  are the datasheet reference values. By combining (20) and (21), a generalized equation can be found which expresses  $R_{\rm DS(on)}$  as a function of the deviations  $\Delta T_{\rm J}$  (=  $T_{\rm J,eq} - T_{\rm J,ref}$ ) and  $\Delta I_{\rm S}$  (=  $I_{\rm S,eq} - I_{\rm S,ref}$ ) of respectively the junction temperature  $T_{\rm J,eq}$  and the switch current  $I_{\rm S,eq}$  from the reference values  $T_{\rm J,ref}$  and  $I_{\rm S,ref}$ :

$$R_{\rm DS(on)} = \left[ R_{\rm DS(on)} \mid_{T_{\rm J,ref}, I_{\rm S,ref}, V_{\rm GS(on),ref}} \cdot (1 + \alpha_1 \,\Delta T_{\rm J} + \alpha_2 \,\Delta T_{\rm J}^2) \cdot (1 + \beta_1 \,\Delta I_{\rm S} + \beta_2 \,\Delta I_{\rm S}^2) \right] + f_{\rm VGS}. \tag{23}$$

$R_{\mathrm{DS(on)}}$   $|_{T_{\mathrm{J,ref}}, I_{\mathrm{S,ref}}, V_{\mathrm{GS(on),ref}}}$  is the reference datasheet value as listed in Table A.1. The coefficients  $(\alpha_1, \alpha_2 \text{ and } \beta_1, \beta_2)$  for both used MOSFETs are given in Table A.3. In (23) a displacement term  $f_{\mathrm{V_{GS}}}$ , determined using linear interpolation (see Figure 7(a)), is introduced in order to take into account the dependency of  $R_{\mathrm{DS(on)}}$  on the turn-on gate voltage  $V_{\mathrm{GS(on)}}$ . For the FCH76N60NF MOSFET, and regarding the applied turn-on gate voltage of  $V_{\mathrm{GS(on)}} = 14 \text{ V}$ ,  $f_{\mathrm{V_{GS}}}$  was found to be  $f_{\mathrm{V_{GS}}} = -2.247 \, e^{-4} \, \Omega$ . For the STY112N65M5,  $f_{\mathrm{V_{GS}}}$  could not be calculated due to the absence of information in the datasheet about the gate voltage dependency of  $R_{\mathrm{DS(on)}}$ , and is assumed to be zero. This leads to a negligible overestimation of the SR's conduction losses.

*Gate drive losses:* Assuming an efficiency of 90% for the gate drive units ( $\eta_{gd} = 0.9$ ), the equivalent, line-cycle averaged gate drive losses  $P_{S,eq,g}$  are:

$$P_{S_{S11-24},eq,g} = \frac{1}{\eta_{gd}} \cdot \frac{Q_g \Delta V_{GS}^2}{\Delta V_{GS,ref}} \cdot \frac{1}{T_L} \int_{0}^{T_L} f_s(t) dt, \qquad (24) \qquad \text{whereas} \quad P_{S_{SR1-4},eq,g} \approx 0$$

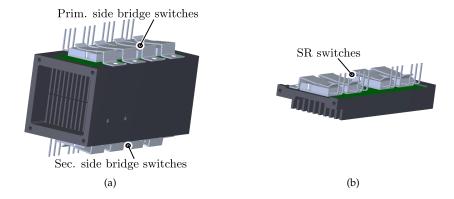

Figure 8. Heat sink - semiconductor assemblies for (a) the DAB and (b) the SR.

since the SR's gate drive losses can be neglected.  $\Delta V_{\rm GS}$  is the gate to source voltage swing which is  $18 \text{ V} (-4 \ldots + 14 \text{ V})$  for the custom designed gate drive circuits.  $Q_g$  is the total (typical) gate charge, measured for the reference gate voltage swing  $\Delta V_{\text{GS,ref}}$  given in Table A.1 of Appendix A.1.

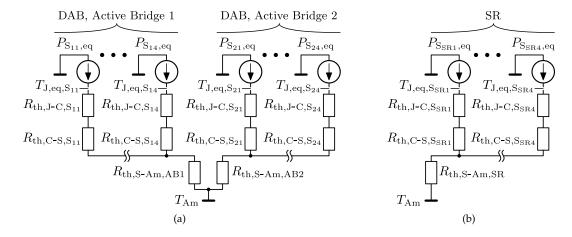

#### 4.1.3. Heat Sink Assembly and Thermal Network Model

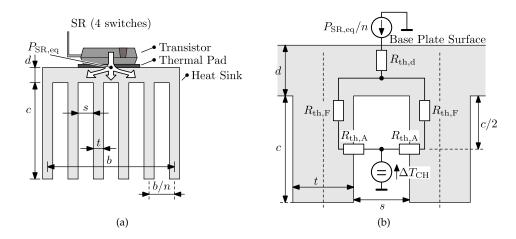

Autonomous air cooling by means of forced convection is one of the system requirements defined in Table 1. Thereby the heat generated by the power devices is subtracted via a finned heat sink in combination with a fan. For the two active bridges of the DAB, a heat sink geometry with dual-sided base plate, as shown in Figure 8(a), is considered. The four switches of the primary-side active bridge (active bridge 1; AB1) are mounted on the top-side base plate while the four switches of the secondary-side active bridge (active bridge 2; AB2) are mounted on the bottom-side base plate. The four switches of the SR are mounted on a heat sink geometry with single-sided base plate, as shown in Figure 8(b). The resulting stationary heat transfer models are depicted in Figure 9, where:

- $R_{\text{th,J-C,S}_{xx}}$  are the junction to case thermal resistances of the switches;

- $R_{\text{th,C-S,S}_{xx}}$  are the thermal resistances of the thermal pads (the Hi-Flow 300P thermal pads from Bergquist are used for all switches).;

- $R_{\text{th,S-Am,AB1}}$  and  $R_{\text{th,S-Am,AB2}}$  (=  $R_{\text{th,S-Am,AB1}}$ ) are the total thermal resistances between the surface of the heat sink (i.e. seen from one base plate) to the ambient, for the heat sink of the DAB;

- $R_{\text{th,S-Am,SR}}$  is the total thermal resistance between the surface of the heat sink (i.e. the surface of the base plate) to the ambient, for the heat sink of the SR.

$R_{\text{th,I-C,S}_{xx}}$  for the used MOSFETs are given in Table A.1 of Appendix A.1, while  $R_{\text{th,C-S}}$  for all switches is defined by  $R_{\text{th,C-S}} = h_{\text{pad}}/(\lambda_{\text{pad}} A_{\text{pad}})$  where  $h_{\text{pad}}$  is the thickness ( $h_{\text{pad}} = 1.2 \, e^{-4}$  m),  $\lambda_{\text{pad}}$  the thermal conductivity ( $\lambda_{\rm pad}=1.6\,{

m W/mK}$ ), and  $A_{\rm pad}$  the cross section area of the thermal pads ( $A_{\rm pad}\approx$  $A_{\rm package}=3.31\,e^{-4}\,{

m m}^{2}$  for the FCH76N60NF MOSFETs and  $A_{\rm pad}\approx A_{\rm package}=3.22\,e^{-4}\,{

m m}^{2}$  for the STY112N65M5 MOSFETs).  $R_{th,S-Am,AB1}$  (=  $R_{th,S-Am,AB2}$ ) and  $R_{th,S-Am,SR}$  are obtained from the heat sink optimizations performed in Section 4.1.4. Referring to Figure 9, the equivalent junction temperature  $T_{\text{J,eq}}$  of a switch can now be expressed as:

$$T_{\text{J,eq}} = T_{\text{Am}} + P_{\text{S,eq}} \cdot (R_{\text{th,J-C}} + R_{\text{th,C-S}} + 4 \cdot R_{\text{th,S-Am}}),$$

(26)

where, under the assumption that half the gate drive losses of a switch are internally dissipated in the switch while the other half is dissipated externally (i.e. in the gate drive units and gate resistors),

$$P_{S,eq} = P_{S,eq,c} + \frac{P_{S,eq,g}}{2}.$$

(27)

$P_{S,eq,c}$  and  $P_{S,eq,g}$  are respectively calculated with (15) and (24)-(25).  $T_{Am}$  is the ambient temperature. At this point all the information required to calculate the equivalent, line-cycle averaged

Peer-reviewed version available at Energies 2016, 9, 799; doi:10.3390/en9100799

12 of 37

Figure 9. Stationary heat transfer model of the heat sink assembly of (a) the DAB and (b) the SR.

semiconductor losses is available. Due to the interdependency of the quantities, a numerical solver is applied to solve:  $P_{S,eq} = f(R_{DS(on)},...)$ ,  $R_{DS(on)} = f(T_J,...)$ , and  $T_J = f(P_{S,eq},...)$ .

## 4.1.4. Heat Sink Optimization

The surface-to-ambient thermal resistances  $R_{\text{th,S-Am,AB1}}$  (=  $R_{\text{th,S-Am,AB2}}$ ) and  $R_{\text{th,S-Am,SR}}$  of the forced-convection-cooled heat sinks are obtained from optimizations in which the heat sink geometries are determined in a way that, for a given fan and for given outer heat sink dimensions, these thermal resistances are minimized. This involves calculation of the thermal resistance for conductive heat transfer through the heat sink material, the thermal resistance for convective heat transfer, and the temperature increase of the air flowing through the heat sink channels. The applied optimization procedure and thermal models are described in detail in [31,32], and are summarized in the following, only considering stationary heat transfer. The involved variables<sup>6</sup> are given in Table 2.

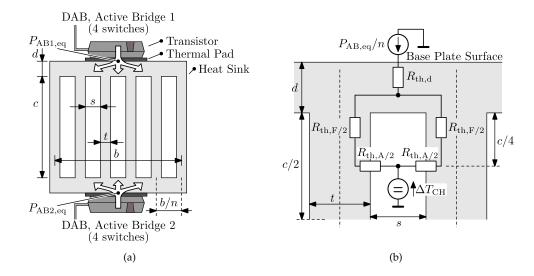

For the heat sink geometry with dual-sided base plate shown in Figure 8(a), the conductive and convective heat transfer are modeled according to Figure 10. The thermal resistance  $R_{th,S-Am}$  from the base plate surface (index 'S') of this heat sink to the ambient (index 'Am'), i.e. the air temperature at the heat sink inlet, is described by:

$$R_{\text{th,S-Am}} = \frac{1}{n} \left( R_{\text{th,d}} + 0.5 \left( R_{\text{th,F/2}} + R_{\text{th,A/2}} \right) \right) + \frac{0.5}{\rho_{\text{AIR}} c_{\text{p,AIR}} 0.5 \, \dot{V}_{\text{AF}}}, \tag{28}$$

with:

$$R_{\text{th,d}} = \frac{d}{\frac{1}{n} A_{\text{BP}} \lambda_{\text{HS}}}, \quad (29) \qquad R_{\text{th,F/2}} = \frac{\frac{1}{4} c}{\frac{1}{2} t L \lambda_{\text{HS}}}, \quad (30) \qquad R_{\text{th,A/2}} = \frac{1}{h L \frac{1}{2} c}. \quad (31)$$

For the heat sink geometry with single-sided base plate shown in Figure 8(b), the conductive and convective heat transfer are modeled according to Figure 11.  $R_{th,S-Am}$  is now described by:

$$R_{\text{th,S-Am}} = \frac{1}{n} \left( R_{\text{th,d}} + 0.5 \left( R_{\text{th,F}} + R_{\text{th,A}} \right) \right) + \frac{0.5}{\rho_{\text{AIR}} \, c_{\text{p,AIR}} \, \dot{V}_{\text{AF}}}, \tag{32}$$

with:

$$R_{\text{th,d}} = \frac{d}{\frac{1}{n} A_{\text{BP}} \lambda_{\text{HS}}},$$

(33)  $R_{\text{th,F}} = \frac{\frac{1}{2} c}{\frac{1}{2} t L \lambda_{\text{HS}}},$  (34)  $R_{\text{th,A}} = \frac{1}{h L c}.$  (35)

$<sup>^6</sup>$  *Pr*,  $\rho_{AIR}$ ,  $\nu_{AIR}$ , and  $\lambda_{AIR}$  are slightly temperature dependent. In order to simplify the analysis, the values at an average channel air temperature of  $T_{CH} = 80^{\circ}$ C are used.

Preprints (www.preprints.org)

13 of 37

**Table 2.** Variables used for the calculation of the thermal resistance of a finned heat sink with fan, and for the calculation of the air flow rate in, and the pressure drop across the air channels of the heat sink.

| Variable                                | Unit               | Description                                               |

|-----------------------------------------|--------------------|-----------------------------------------------------------|

| d                                       | m                  | base plate thickness                                      |

| t                                       | m                  | width of a fin                                            |

| b                                       | m                  | total width of all air channels                           |

| С                                       | m                  | total height of the air channel (=height of the fins)     |

| S                                       | m                  | width of a single air channel                             |

| L                                       | m                  | length of the air channels                                |

| n                                       |                    | number of channels                                        |

| k                                       |                    | fin spacing ratio acc. to (53)                            |

| $A_{\mathrm{BP}}$                       | m <sup>2</sup>     | area of the heat sink base plate ( $A_{BP} = L \cdot b$ ) |

| $d_{\rm h}$                             | m                  | hydraulic diameter of one channel acc. to (52)            |

| $\Delta p_{\mathrm{CH}}$                | N/m <sup>2</sup>   | pressure drop across the heat sink channels               |

| $\dot{V}_{ m AF}$                       | $m^3/s$            | total volume flow of the air in the heat sink channels    |

| Reavg                                   |                    | average Reynolds number acc. to (57)                      |

| $Pr \approx 0.71$                       |                    | Prandtl number (air, 80°C)                                |

| Na                                      |                    | average Nusselt number acc. to (58) for laminar airflow   |

| Nuavg                                   |                    | or acc. to (59) for turbulent airflow                     |

| h                                       | W/m <sup>2</sup> K | convective heat transfer coefficient acc. to (60)         |

| $\lambda_{ m HS}$                       | W/mK               | thermal conductivity of the heat sink material            |

| $ \rho_{\rm AIR} \approx 0.99 $         | kg/m <sup>3</sup>  | air density (80°C)                                        |

| $\nu_{\rm AIR} \approx 2.1 { m e}^{-5}$ | m <sup>2</sup> /s  | cinematic viscosity of air (80°C)                         |

| $c_{\rm p,AIR} \approx 1010$            | J/kgK              | specific thermal capacitance of air                       |

| $\lambda_{\rm AIR} \approx 0.03$        | W/mK               | thermal conductivity of air (80°C)                        |

**Figure 10.** (a) Heat sink geometry with dual-sided base plate, considered to cool the switches of the DAB's active bridges. (b) Thermal network describing stationary heat transfer between the surface of a base plate and the air in the heat sink channel (temperature  $T_{\rm CH}$ ).

The last term of the thermal resistance  $R_{\rm th,S-Am}$  in both (28) and (32) considers the average temperature rise of the air from channel inlet to channel outlet. Calculation of the convective heat transfer coefficient h and the total volume flow  $\dot{V}_{\rm AF}$  of the air in the heat sink channels, which are both required for the calculation of  $R_{\rm th,S-Am}$  in (28) and (32), goes as follows.

Based on (52)-(55) of Appendix A.1, the air flow pressure drop in the heat sink channels for laminar ('lam') and turbulent ('turb') flow can be calculated. Balancing the pressure drop with the pressure of the fan, as defined by the fan characteristic in (56), gives the fan's operating point which defines the air flow and pressure drop in the heat sink channels. Using (57), the Reynolds number is

doi:10.20944/preprints201608.0148.v1

**Figure 11.** (a) Heat sink geometry with single-sided base plate, considered to cool the switches of the SR. (b) Thermal network describing stationary heat transfer between the surface of the base plate and the air in the heat sink channel (temperature  $T_{\rm CH}$ ).

found as well. In case of laminar flow, with Re < 2300, eq. (58) is used to calculate the Nusselt number, which describes the convective heat transfer from the channel walls into the air. In case of turbulent flow, with Re > 2300, the Nusselt number is calculated with eq. (59). Using (60), the convective heat transfer coefficient h of the configuration is finally found.

By repeating the above procedure for different heat sink geometries, an optimal set of geometrical parameters (d, t, b, c, s, L, and n) can be found which leads to the lowest thermal resistance  $R_{\text{th,S-Am}}$ . This is done for both heat sinks, assuming predefined outer heat sink dimensions (i.e. variables b, c, L, and d). As a result, the geometric parameters that are varied during the optimization are the number of channels n and the fin spacing ratio k, which is equivalent to varying the channel width s; see eq. (53). The results are discussed below.

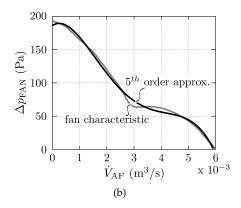

Heat sink of the DAB with dual-sided base plate, conform Figure 10: The fan size defines the heat sink front geometry as only the fins that are facing the fan contribute to the convective heat transfer. After thorough iteration of the mechanical design of the final prototype converter, a 40x40 mm fan turned out to be most feasible, leading to the selection of the SanAce40GA<sup>7</sup> (see Figure 12). Consequently, a heat sink geometry with b=c=40 mm is most appropriate in order to fully utilize the fan. The pressure-flow curve,  $\Delta p_{\rm FAN}(\dot{V}_{\rm AF})$ , of this fan is depicted in Figure 12(b) (gray line) and can be described by a 5<sup>th</sup> order approximation (black line in Figure 12(b)):

$$\Delta p_{\text{FAN}}(\dot{V}_{\text{AF}}) = (5.38 \cdot 10^{13} \cdot \dot{V}_{\text{AF}}^5 - 2.115 \cdot 10^{12} \cdot \dot{V}_{\text{AF}}^4 + 1.96 \cdot 10^{10} \cdot \dot{V}_{\text{AF}}^3 - 6.315 \cdot 10^7 \cdot \dot{V}_{\text{AF}}^2 + 2.828 \cdot 10^4 \cdot \dot{V}_{\text{AF}} + 185.7).$$

(36)

The length L of the heat sink channels must be large enough so that sufficient space is provided on the base plates to mount the switches. Assuming a minimum spacing of 5 mm between the packages of adjacent switches, a minimum spacing of 10 mm between the base plate borders and a package, and a package width of approximately 16 mm for the TO-247 package, the minimum base plate length becomes  $L_{\rm min}=3\cdot 5$  mm  $+2\cdot 10$  mm  $+4\cdot 16$  mm =99 mm. Preferably the maximum base plate length should not be much higher than  $L_{\rm min}$ , assuring homogeneous heat distribution across the base plate. The final base plate length is L=99.8 mm. The base plate thickness d should be

<sup>&</sup>lt;sup>7</sup> The SanAce40GA fan (type 9GA0412P7G001, see Figure 12(a)) has been selected due to its high static pressure, high air flow rate, and low sound pressure level, in combination with an ultra low power consumption.

**Figure 12.** (a) Picture of the selected fan: SanAce40GA, type 9GA0412P7G001, 40x40x15 mm, 12 V. (b) Datasheet pressure-flow curve (gray line) and 5<sup>th</sup> order approximation (black line).

large enough to homogeneously spread the heat and small enough to limit the thermal resistance of the heat sink. The value d=6 mm is selected as a good trade-off between these two considerations.

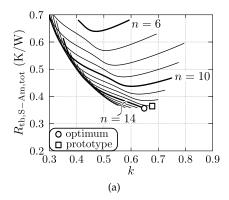

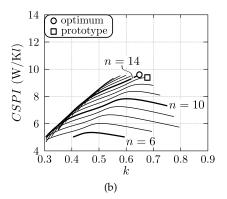

Figure 13 shows the results of the optimization, applying the assumed outer heat sink dimensions, i.e. the above discussed variables b, c, L, and d, and assuming a minimum achievable fin thickness and channel width of 1 mm, which are enabled by using high-end milling machines. Furthermore, aluminium is considered for the heat sink material, defining the thermal conductivity value  $\lambda_{\rm HS} = 210~{\rm W/mK}$ . Figure 13(a) depicts the relation between  $R_{\rm th,S-Am,tot}$  (=  $0.5 \cdot R_{\rm th,S-Am}$ )<sup>8</sup> and the two geometric parameters n and k that are independently varied. The performance indices and parameter values for the resulting (optimal) heat sink design are given in the top inset of Table A.4 of Appendix A.1. There,  $V_{\rm HS}$  is the boxed volume of the heat sink, excluding the fan and an additional airflow inlet between the fan and the heat sink.  $V_{\rm CS}$  is the volume of the cooling system, including the heat sink, the fan, and an additional airflow inlet between the fan and the heat sink. CSPI is the cooling system performance index [31–33], which is an objective measure that allows to compare different cooling system designs with regard to power density. For the cooling system of the DAB, with dual-sided base plate, CSPI is defined as [32]:

$$CSPI = \frac{1}{R_{\text{th,S-Am,tot}} \cdot V_{\text{CS}}} = \frac{1}{0.5 \cdot R_{\text{th,S-Am}} \cdot V_{\text{CS}}}.$$

(37)

If a heat sink design shows a CSPI that is two times higher than the CSPI of another one, the cooling volume  $V_{CS}$  can be made two times smaller for the same thermal resistance. Knowing that typical commercially available heat sink - fan combinations have a CSPI of around 5, the extensive heat sink optimization, achieving  $CSPI \approx 9$ , is justified. The (boxed) volume  $V_{CS,tot}$ , which besides the heat sink, the fan, and the airflow inlet also includes the semiconductor switching devices, is also listed in Table A.4. The bottom inset of Table A.4 shows the performance indices and design parameters of the heat sink used in the final (prototype) converter, and considered for further calculations. It in fact is a near-optimal design, which is due to the fact that the minimum achievable fin thickness and channel width were restricted due to limitations of the in-house manufacturing machines/tools.

Heat sink of the SR with single-sided base plate, conform Figure 11: For the heat sink of the SR, once more the 40x40 mm SanAce40GA fan (see Figure 12) is selected. As the SR requires less cooling effort than the DAB, the heat sink's front geometry values are reduced from b = c = 40 mm (most appropriate in order to fully utilize the fan) to b = 36 mm and c = 10 mm. This allows to use part of

<sup>&</sup>lt;sup>8</sup> The multiplication of  $R_{\text{th,S-Am}}$  with a factor '0.5' is required since  $R_{\text{th,S-Am}}$  is experienced from just one base plate of the heat sink and thus has to be divided by two in order to take both base plates (top and bottom) into account.

Preprints (www.preprints.org)

**Figure 13.** Optimization result for the heat sink of the DAB (geometry with dual-sided base plate, cf. Figure 10), assuming a minimum achievable fin thickness and channel width of 1 mm. (a) Total surface-to-ambient thermal resistance  $R_{\text{th,S-Am,tot}}$  (=  $0.5 \cdot R_{\text{th,S-Am}}$ ) as function of n and k, which are independently varied. (b) Cooling system performance index CSPI as function of n and k.

the fan's airflow to cool other electronic components. The reduced airflow in the heat sink channels due to the area reduction of the heat sink's front geometry is taken into account by multiplying  $\dot{V}_{\rm AF}$  with the heat-sink-front-area to fan-area ratio  $(b\cdot c)/(40\cdot 40)$ . Furthermore, a slightly increased channel length of L=104 mm is used and a base plate thickness of d=5 mm is applied. Once more, a minimum achievable fin thickness and channel width of 1 mm are assumed.

The performance indices and parameter values for the resulting (optimal) heat sink design are given in the top inset of Table A.5 of Appendix A.1. The bottom table inset shows the values for the heat sink design of the final (prototype) converter. For the reason mentioned above this is a near-optimal design and is considered for further calculations. Note that the part of the fan that does not faces fins is not included in the calculation of  $V_{\text{CS,tot}}$ , and that for the heat sink with single-sided base plate CSPI is defined as [32]:

$$CSPI = \frac{1}{R_{\text{th.S-Am}} \cdot V_{\text{CS}}}.$$

(38)

#### 4.2. Magnetic Elements of the DAB: Inductors and Transformer

As mentioned before, the DAB dc–dc converter consists of three discrete magnetic elements: the HF ac-link transformer, the external series inductor  $L_{\rm ext}$ , and the primary-side commutation inductor  $L_1$ . The secondary-side commutation inductance  $L_2$  is implemented by the magnetizing inductance of the transformer ( $L_2 = L_{\rm M}$ ), avoiding increased volume and costs. Referring to the equivalent DAB model shown in Figure 3, the main energy transfer inductance L is calculated with eq. (4), where  $L_{\sigma,1}$  and  $L_{\sigma,2}$  are the primary- and secondary-side leakage inductances of the transformer. Consequently, to determine the inductance value  $L_{\rm ext}$ , the transformer needs to be designed first (i.e.  $L_{\sigma,1}$  and  $L_{\sigma,2}$  result from the final transformer design). Remind that the values of L,  $L_1$ ,  $L_2$ , and N (=  $n_1/n_2$ ) are derived in Section 3.3 and are given in the right inset of Figure 1.

#### 4.2.1. Design and Optimization Procedure

Two optimization algorithms, i.e. for the transformer and for the inductors, are developed in order to optimize each magnetic element with regard to the losses and their (boxed) volume. Apart from the currents and voltages, losses in inductors and transformers depend on the geometry and the arrangement of the windings, the type of wires, the type of the core, and the geometry and material of the core. The resulting volume is mainly determined by the core geometry and the end turns of the windings. For the different optimizations, planar cores are considered because of their excellent electromagnetic and thermal characteristics and their advantageous properties with

respect to the achievable power density [34,35]. All possible EELP and EILP core combinations from FERROXCUBE (ferrite core material: 3F3 and 3F4) and EPCOS (ferrite core material: N49, N87, N92, and N97) in the dimensions range from ELP32 up to ELP64 are considered. The number of stacked cores is limited by setting a maximum of 15 cm to the total core length. Litz wires are chosen to reduce eddy current losses in the windings [36–38], being particularly effective at high switching frequencies. Furthermore, four possible winding arrangements are investigated, including split, concentric, hexagonal and orthogonal type windings. Also the paralleling of several Litz bundles, as well as the interleaving (for the transformer) of the windings, is implemented in the algorithms.

All possible combinations of above mentioned design variables are top level iterated. For each iteration, in a **first step** the reluctance model  $R_{\rm m}$  of the considered magnetic element is calculated according to the methods proposed in [39], which inter alia provides a new analytical approach in order to determine the 3D air gap reluctance  $R_{\rm m,air}$ . The inductance values, i.e.  $L_{\rm ext}$ ,  $L_{\rm 1}$ , and  $L_{\rm 2}$  (=  $L_{\rm M}$ ), are controlled with the air gap length  $l_{\rm g}$  (constrained to  $0 \leqslant l_{\rm g} \leqslant l_{\rm g,max} = 1$  mm), while guaranteeing that the peak flux density  $\hat{B}$  does not exceed a predefined maximum value  $\hat{B}_{\rm max}$ . This introduces an upper and a lower limit to the possible number of turns. For the transformer, the minimum and maximum number of turns, i.e.  $n_{\rm 1,min}$  respectively  $n_{\rm 1,max}$ , for the primary-side winding are determined by:

$$n_{1,\text{min}} = \text{ciel}\left(\frac{(V \cdot s)_{\text{p,max}}}{2\,\hat{B}_{\text{max}}\,A_{\text{c}}}\right), \quad (39) \quad n_{1,\text{max}} = \text{floor}\left(\sqrt{L'_{\text{M}}\left(R_{\text{m,core}} + R_{\text{m,air}}\right)|_{l_{\text{g}} = l_{\text{g,max}}}}\right), \quad (40)$$

where  $(V \cdot s)_{\rm p,max}$  is the maximum primary-side referred Volt-seconds product,  $A_{\rm c}$  the effective core cross section,  $R_{\rm m,core}$  the core reluctance,  $R_{\rm m,air}$  the air gap reluctance, and  $L'_{\rm M}$  (=  $N^2 \cdot L_{\rm M}$ ) the primary-side referred magnetizing inductance. The number of turns  $n_1$  for the primary-side winding of the transformer then needs to be in the range  $n_{1,{\rm min}} \leq n \leq n_{1,{\rm max}}$ . Evidently, the number of turns  $n_2$  for the secondary-side winding is directly linked to  $n_1$  via the transformer's turns ratio  $N = n_1/n_2$ . For the inductors, the minimum and maximum number of turns, i.e.  $n_{\rm ind,min}$  respectively  $n_{\rm ind,max}$ , are determined by:

$$n_{\text{ind,min}} = \text{ciel}\left(\frac{L_{\text{ind}} i_{\text{ind,max}}}{\hat{B}_{\text{max}} A_{\text{c}}}\right), \quad (41) \quad n_{\text{ind,max}} = \text{floor}\left(\sqrt{L_{\text{ind}} \left(R_{\text{m,core}} + R_{\text{m,air}}\right) \mid_{l_{\text{g}} = l_{\text{g,max}}}}\right), \quad (42)$$

where  $i_{\rm ind,max}$  is the peak inductor current and  $L_{\rm ind}$  (=  $L_{\rm ext}$  or  $L_1$ ) the inductance value of the considered inductor. The number of turns  $n_{\rm ind}$  for the inductors then needs to be in the range  $n_{\rm ind,min} \leqslant n_{\rm ind} \leqslant n_{\rm ind,max}$ . The upper boundary of the maximum allowed flux density  $\hat{B}_{\rm max}$  is set by the core material saturation flux density  $B_{\rm sat}$  at a core temperature of  $100^{\circ}$ C, applying a 30% safety margin. Subsequently, using an inner iteration loop, the number of turns  $n_1$  (transformer) is varied from  $n_{1,\rm min}$  to  $n_{1,\rm max}$  while the number of turns  $n_{\rm ind}$  (inductors) is varied from  $n_{\rm ind,min}$  to  $n_{\rm ind,max}$ .

In a **second step**, a predefined objective function, which is determined by the sum of the core losses and the winding losses of the magnetic element at nominal operating conditions of the DAB, is minimized for each of above iterations. The applied loss models are summarized in Section 4.2.2. The optimization algorithm used to minimize the cost function iterates the number of strands in the Litz bundles, as well as the diameter of the individual strands, in order to achieve a window filling that is optimal with regard to the winding losses. Thereby, constraint functions set restrictions on the positioning of the individual Litz bundles by bringing into relation the number of strands, the strand diameter, and wire positioning functions with the given core window area, taking into account creepage distances.

#### 4.2.2. Loss Models

In this section, the models used to calculate the winding and core losses of the magnetic elements are summarized. For the calculation of the **core losses**, the improved Generalized Steinmetz Equation

(iGSE) [38,40] has been evaluated as the most accurate model which only requires the Steinmetz material parameters. This method takes into account the losses due to domain wall motion, which is directly related to the time dependency dB/dt of the core's flux density. Therefore the iGSE is applicable for non-sinusoidal flux waveforms such is the case for the magnetic components of the DAB, which experience piecewise-linear flux-time functions. With the iGSE, the per-unit-volume (index 'V') core losses are calculated using the Steinmetz parameters k,  $\alpha$ , and  $\beta$ , according to:

$$P_{\text{core,V}} = \frac{1}{T} \int_0^T k_i \left| \frac{dB}{dt} \right|^{\alpha} (\Delta B)^{\beta - \alpha} dt, \quad (43) \quad \text{with: } k_i = \frac{k}{(2\pi)^{\alpha - 1} \int_0^{2\pi} |\cos \theta|^{\alpha} 2^{\beta - \alpha} d\theta}, \quad (44)$$

where  $\Delta B$  is the peak-to-peak flux density. The Steinmetz parameters k,  $\alpha$ , and  $\beta$  are extracted out of the core's data sheets, providing information about the per-volume-unit core losses as a function of frequency f, peak flux density  $\hat{B}$ , and temperature T. This enables extraction of k,  $\alpha$ , and  $\beta$  using the empirical Steinmetz Equation  $P_{\text{core},V} = k f^{\alpha} \hat{B}^{\beta}$ , which is valid for sinusoidal excitation only.

Regarding winding losses, the ohmic losses in the Litz wires (further referred to as Litz bundles) can be separated into skin effect losses  $P_{\rm S}$  from self-induced eddy currents inside the conductors, external proximity effect losses  $P_{\rm P,e}$  from eddy currents due to the external magnetic field  $H_{\rm e}$  that originates in the air gap fringing field and in the magnetic field from neighboring Litz bundles, and internal proximity effect losses  $P_{\rm P,i}$  from eddy currents due to the internal magnetic field  $H_{\rm i}$  that is produced by the bundle itself. The per-unit-length (index 'L') skin-effect losses (including the dc losses) of a Litz bundle consisting of  $n_{\rm S}$  strands, are calculated with [38]:

$$P_{S,L} = n_s \cdot R_{dc,s,L} \cdot F_R(f) \cdot \left(\frac{\hat{I}}{n_s}\right)^2, \tag{45}$$

where  $\hat{l}$  are the Fourier amplitude coefficients of the total current in the Litz-wire bundle at the different harmonic frequencies f.  $R_{\text{dc,s,L}}$  is the per-unit-length dc resistance of a single strand:  $R_{\text{dc,s,L}} = 4/(\sigma\pi d_s^2)$ , with  $d_s$  the diameter of the strand and  $\sigma$  the electric conductivity of the conductor material ( $\sigma = 5.26 \cdot 10^7 \text{ 1/}\Omega\text{m}$  for the considered Litz wires).  $F_R$  is the skin-effect factor:

$$F_{R}(f) = \frac{\xi}{4\sqrt{2}} \cdot \left(\frac{\text{ber}_{0}(\xi) \text{bei}_{1}(\xi) - \text{ber}_{0}(\xi) \text{ber}_{1}(\xi)}{\text{ber}_{1}(\xi)^{2} + \text{bei}_{1}(\xi)^{2}} - \frac{\text{bei}_{0}(\xi) \text{ber}_{1}(\xi) + \text{bei}_{0}(\xi) \text{bei}_{1}(\xi)}{\text{ber}_{1}(\xi)^{2} + \text{bei}_{1}(\xi)^{2}}\right), \quad (46)$$

with  $\xi = d_s/(\sqrt{2}\,\delta)$ , where  $\delta$  is the skin depth according to  $\delta = 1/\sqrt{\pi\,\mu_0\,\sigma\,f}$ .  $\mu_0$  is the permeability of the conductor material ( $\mu_0 = 4\,\pi\,10^{-7}$  H/m for air and copper). The per-unit-length proximity losses in a Litz bundle are calculated as [38]:

$$P_{P,L} = P_{P,e,L} + P_{P,i,L} = n_{s} \cdot R_{dc,s,L} \cdot G_{R}(f) \left( \hat{H}_{e}^{2} + \frac{\hat{I}^{2}}{2 \pi^{2} d_{b}^{2}} \right).$$

(47)

$d_b$  is the diameter of the Litz bundle while  $G_R$  is the proximity-effect factor:

$$G_{\rm R}(f) = -\frac{\xi\,\pi^2\,d_{\rm s}^2}{2\sqrt{2}}\cdot \left(\frac{{\rm ber_2}(\xi)\,{\rm ber_1}(\xi) + {\rm ber_2}(\xi)\,{\rm bei_1}(\xi)}{{\rm ber_0}(\xi)^2 + {\rm bei_0}(\xi)^2} + \frac{{\rm bei_2}(\xi)\,{\rm bei_1}(\xi) - {\rm bei_2}(\xi)\,{\rm ber_1}(\xi)}{{\rm ber_0}(\xi)^2 + {\rm bei_0}(\xi)^2}\right). \eqno(48)$$

$H_{\rm e}$  is the external magnetic field that originates in the air gap fringing field and in neighboring Litz bundles, and is calculated using the 2D analytical approach proposed in [38]. This approach relies on an imaging and mirroring method in order to inter alia model the impact of a surrounding magnetic conducting material. Thereby the air gap fringing fields are modeled by means of fictitious conductors with eddy currents equal to the magneto-motive force across the air gap.  $H_{\rm i}$ , with  $\hat{H}_{\rm i}^2 = \hat{I}^2/(2\pi^2 d_{\rm b}^2)$ ; see last term of (47), is the internal magnetic field across one strand, which originates in its neighboring strands. For the calculation of  $H_{\rm i}$  it is assumed that the current is equally distributed over the Litz bundle's cross-sectional area.

Preprints (www.preprints.org)

19 of 37

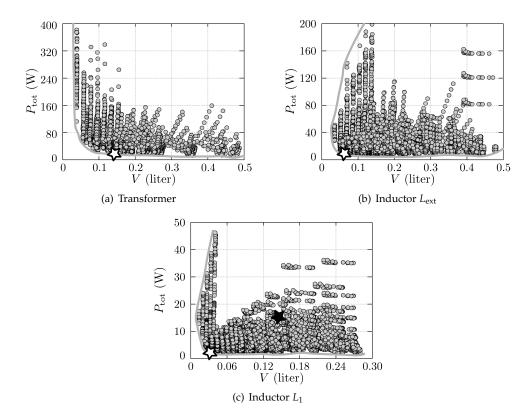

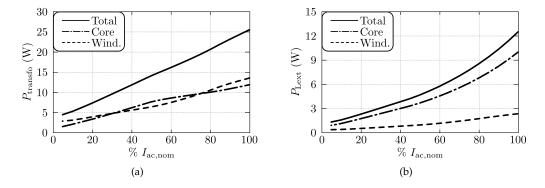

Figure 14. Two-dimensional losses vs. volume performance spaces for (a) the HF ac-link transformer, (b) inductor  $L_{\text{ext}}$ , and (c) inductor  $L_1$ , calculated for nominal DAB operating conditions.

#### 4.2.3. Optimization Results

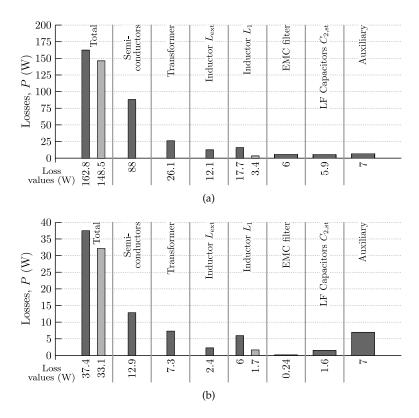

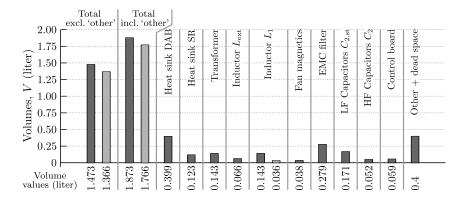

For each magnetic element of the DAB, the outcome of the optimization is a two-dimensional performance space, showing the losses at nominal operating conditions versus the (boxed) volume of the component. Figures 14(a), 14(b), and 14(c) respectively depict the resulting performance spaces for the HF transformer and for inductors  $L_{\text{ext}}$  and  $L_1$ . The designs that are chosen for the hardware realization of the transformer and of inductor  $L_{\text{ext}}$  are marked with  $\stackrel{\leftrightarrow}{\sim}$ . As these designs are located in the corner point of the so called 'Pareto Front', they are an optimal trade-off between efficiency and power density. It should be noted that the hardware realization of  $L_1$ , marked with  $\star$ , is a duplicate of the HF transformer with one of the two windings removed and with the air gap length adapted according to the calculated inductance value  $L_1$ . The realization of  $L_1$  is thus non-optimal, and is referred to as the 'prototype' (prot.) design. A better solution would be to use the design marked with \$\pri\$, which is referred to as the 'optimal' (opt.) design. The detailed parameter values of the transformer and inductor designs are listed in Tables A.6-A.8 of Appendix A.2, where Table A.8 lists the values for both the 'prot.' and the 'opt.' design of  $L_1$ . The implication of using the improved design 'opt.' for  $L_1$  on the converter performance is further discussed in Section 5.

## 4.3. Output Filter Capacitors

## 4.3.1. LF Output Filter Capacitors

Since the DAB handles the double line frequency component of the converter's ac input power, a LF filter capacitor  $C_{2,st}$  is placed at the converter's dc output side (see Figure 1), limiting the output voltage ripple. Assuming unity power factor, where the ac input current  $i_{ac}(t)$  and input voltage  $v_{\rm ac}(t)$  are in phase, the output voltage ripple  $V_{\rm dc,2}(t)$  is calculated as:

$$\tilde{V}_{dc,2}(t) = \frac{-P_{dc,2} \cdot \sin(2\omega_L t)}{2\omega_L C_{2,st} V_{dc,2}},$$

(49)

where  $P_{\text{dc,2}}$  ( $\approx P_{\text{ac}} = V_{\text{ac}} \cdot I_{\text{ac}}$ ) is the constant output power component,  $\omega_{\text{L}} = 2 \,\pi \,f_{\text{L}}$  the angular frequency of the grid, and  $V_{\text{dc,2}}$  the average dc output voltage of the converter. As a result, the amplitude of the output voltage ripple is equal to  $\hat{V}_{\text{dc,2}} = P_{\text{dc,2}}/(2 \,\omega_{\text{L}} \,C_{2,\text{st}} \,V_{\text{dc,2}})$ .

In the final hardware demonstrator, the LF output filter capacitance  $C_{2,\rm st}$  is realized using three 390  $\mu$ F, 500 V dc, electrolytic capacitors (ELCOs), type EETED2W391EA, from Panasonic, which are placed in parallel. This leads to a total LF output filter capacitance value of  $C_{2,\rm st}=1170~\mu$ F. For nominal conditions, i.e.  $V_{\rm ac}=230~{\rm V_{rms}}$ ,  $I_{\rm ac}=16~{\rm A_{rms}}$ , and  $V_{\rm dc,2}=400~{\rm V}$ , this results in an very acceptable output voltage ripple amplitude of  $\hat{V}_{\rm dc,2}\approx12~{\rm V}$ . The worst case (i.e. at  $V_{\rm ac}=V_{\rm ac,max}=253~{\rm V_{rms}}$ ,  $I_{\rm ac}=I_{\rm ac,nom}=16~{\rm A_{rms}}$ , and  $V_{\rm dc,2}=V_{\rm dc,2,min}=370~{\rm V}$ ) ripple amplitude is  $\hat{V}_{\rm dc,2}\approx14.2~{\rm V}$ , which is still less than 4% of the output voltage.

For the electrolytic LF output filter capacitors, with a diameter of 35 mm and a height of 40 mm (single capacitor), the total boxed volume is 0.147 liter. The part of the SR's fan that does not faces heat sink fins is facing the LF filter capacitors, which are thereby cooled. Consequently, an additional volume of 0.024 liter is added to the LF capacitor's volume for the system volume calculation in Section 5. Remind that this part of the SR's fan is not taken into account in the volume of the SR's cooling system, see Section 4.1.4.

### 4.3.2. HF Output Filter Capacitors

Besides the electrolytic LF capacitors, small HF filter capacitors  $C_2$  are placed at the output of the DAB in order to bypass the HF components of the DAB output current  $i_{\rm dc,2}$ . The HF filter capacitance value  $C_2$  is realized using seven 1.5  $\mu$ F, 630 V dc, metallized polypropylene MKP film capacitors, type B32674D6155, from EPCOS, which are placed in parallel. This leads to a total HF output filter capacitance value of  $C_2 = 10.5 \ \mu$ F and a maximum HF output voltage ripple amplitude of less than 2 V. With a width of 31.5 mm, a depth of 12.5 mm, and a height of 19 mm (single capacitor), the total boxed volume is 0.052 liter.

## 4.3.3. Capacitor Losses

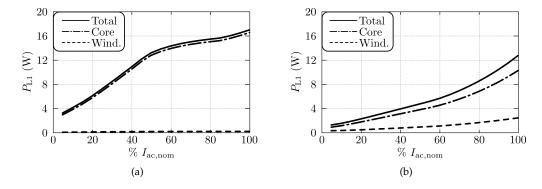

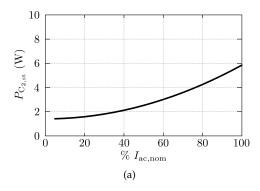

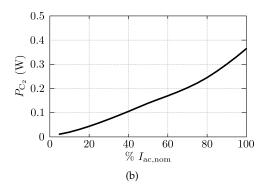

Losses in the LF filter capacitors are caused by their equivalent series resistance (ESR) and leakage current. The ESR value listed in the datasheet of the employed 390  $\mu$ F EETED2W391EA ELCOs from Panasonic is 0.34  $\Omega$  at 120 Hz. According to the datasheet, the leakage current  $I_{\text{leak}}$  of a single capacitor is calculated as  $I_{\text{leak}} = 3 \cdot 10^{-6} \cdot \sqrt{C V}$  (A), with C the capacitance value in  $\mu$ F and V the capacitor voltage. Consequently, the total power loss  $P_{\text{C2-st}}$  in the LF capacitors is calculated as:

$$P_{\text{C}_{2,\text{st}}} = 3 \cdot (I_{\text{C}_{2,\text{st}}}^2 \cdot \text{ESR} + I_{\text{leak}} \cdot V_{\text{dc},2}), \tag{50}$$

where  $I_{C_{2,st}}$  is the RMS value of the current in a single capacitor. The factor 3 is applied since three capacitors are placed in parallel. Since the leakage current of polypropylene film capacitors is very low, the losses in the EPCOS HF capacitors are mainly caused by the ESR, producing a total loss of less than 0.5 W, which can be neglected.

## 4.4. EMC Input Filter

In order to comply with the CISPR 22 Class B standard [41] for conducted emission (CE), an electromagnetic compatibility (EMC) filter is designed. Thereby, a differential mode (DM) filter is required to attenuate the HF components of the DAB input current  $i_{dc,1}$  (see Figure 1), and a common mode (CM) filter for suppressing the CM noise on the earth wire.

**Figure 15.** Schematic of the DM/CM EMC filters, connected to the synchronous rectifier of the ac–dc converter. Also shown are the line impedance stabilization network (LISN) and the EMC test receiver.

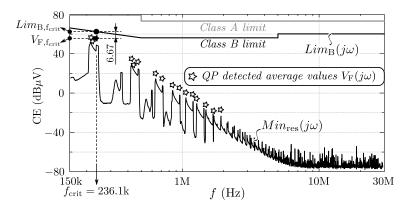

## 4.4.1. Differential Mode (DM) Filter Design

The DM EMC input filter is designed according to the procedure outlined in [42], and conform the guidelines given in [43] regarding filter damping, in order to comply with the CISPR 22 Class B standard [41] in the frequency range of 150 kHz – 30 MHz. The employed procedure includes the correct modeling of the line impedance stabilization network (LISN) and of the EMC test receiver (see Figure 15), i.e. conform the CISPR 16 standard [44]. This enables a prediction of the measurement results and thus gives the basis for the calculation of the required attenuation and for the filter design. The video-filtered quasi-peak (QP) values  $V_F(j\omega)$  at the output of the EMC test receiver need to be lower than the CISPR 22 Class B limit  $Lim_B(j\omega)$ . For the case where no DM filter is present the most critical QP value is found<sup>9</sup> to be  $V_{F,f_{crit}}=170.4~{\rm dB}\cdot\mu{\rm V}$  at a corresponding frequency  $^{10}$  of  $f_{\rm crit}=236.3~{\rm kHz}$ , at which the Class B limit value is equal to  $Lim_{B,f_{\rm crit}}=62.22~{\rm dB}\cdot\mu{\rm V}$ . Therefore, the required attenuation  $Att_{\rm req,f_{crit}}$  of the DM filter, including a margin of 6 dB, is equal to:

$$Att_{\text{req},f_{\text{crit}}} = V_{\text{F},f_{\text{crit}}} - Lim_{\text{B},f_{\text{crit}}} + 6 \text{ dB} = 170.4 - 62.22 + 6 = 114.18 \text{ dB}.$$

(51)

The DM filter needs to provide the required attenuation  $Att_{\rm req,f_{\rm crit}}$  so that, in combination with an appropriate CM filter, the converter complies with the standards. Thereby, control-oriented aspects have to be considered as well, ensuring a satisfactory operation of the converter. Using the recursive design procedure outlined in [42], the two-stage DM filter structure shown in Figure 15 turns out to be most appropriate for achieving these goals. In order to provide sufficient damping of the filter resonances without decreasing the attenuation in the frequency range that is relevant for compliance with the CISPR standard, for each filter stage an (optimized) passive damping network is employed. Thereby, a series inductor damping network with coupled inductors is selected for the

The simulations are performed under nominal operating conditions, i.e. at the nominal ac input voltage of  $V_{\rm ac}=230~{\rm V_{rms}}$ , the nominal ac input current of  $I_{\rm ac}=16~{\rm A_{rms}}$ , and an output voltage of  $V_{\rm dc,2}=400~{\rm V}$ .

Note that towards the dc side of the DAB's input bridge, the bridge current  $i_1$  is rectified into  $i_{dc,1}$ , doubling the frequency. Therefore, and due to operation with variable switching frequency, the value of 236.3 kHz for  $f_{crit}$  can be explained.

The components of the DM filter in Figure 15 are indexed 'DM' (i.e. 'DM1' for the first filter stage and 'DM2' for the second filter stage). The capacitive part  $C_{\text{DM1}}$  of the first filter stage is effectively realized by the HF dc-link capacitor  $C_1$ .

**Figure 16.** Simulation of the QP measurement after insertion of the designed DM input filter and under the assumption of zero mains impedance. Also shown is the absolute lower boundary  $Min_{res}(j\omega)$  for the measurement result and the CE limits according to CISPR 22 Classes A and B.

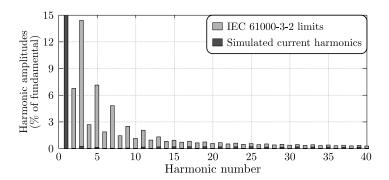

**Figure 17.** Simulated low-frequency harmonics of the mains current  $i_{ac}$  and the IEC61000-3-2 limits.

first filter stage while a parallel capacitor damping network is used for the second filter stage. The resulting values and specifications of the employed DM filter components are listed in Table A.9 of Appendix A.3. Note that the second filter stage is formed by capacitance  $C_{\rm DM2}$  in combination with the LISN ( $R_{\rm LISN}=50~\Omega$ ,  $C_{\rm LISN}=250~\rm nF$ ,  $L_{\rm LISN}=50~\mu H$ , see Figure 15) and the mains inductance  $L_{\rm mains}$ , i.e. no discrete inductor  $L_{\rm DM2}$  is present.

Figure 16 shows the simulated (nominal operating conditions) video-filtered quasi-peak (QP) values  $V_F(j\omega)$  (indicated by a ' $\dot{\alpha}$ '), along with the CISPR 22 Classes A and B limits and the lower boundary value  $^{12}$   $Min_{\rm res}(j\omega)$  after insertion of the designed DM input filter and under the assumption of zero mains impedance. It can be seen that the critical output value  $V_{\rm F,f_{\rm crit}}$  (indicated by a ' $\star$ ') is 6.67 dB lower than the Class B limit  $Lim_{\rm B,f_{\rm crit}}$ , meaning that compliance with the CISPR 22 Class B standard is achieved. Furthermore, the simulated low-frequency harmonics of the mains current  $i_{\rm ac}$ , which in the case at hand need to be below the limits defined in the IEC 61000-3-2 standard [45] for Class A equipment, are depicted in Figure 17 and are well below the limits.

# 4.4.2. Common Mode (CM) Filter Design

In order to successfully design a common mode (CM) filter that suppresses the CM noise on the earth wire, an equivalent CM noise-source model is required [46]. Thereby, detailed knowledge of the relevant parasitic impedances, through which the CM currents circulate, is essential. As a result, the design of the CM EMC filter is mostly performed after the realization of a first converter prototype

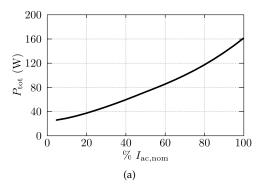

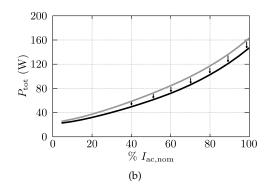

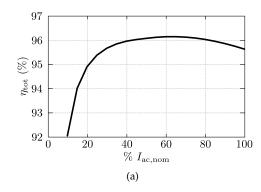

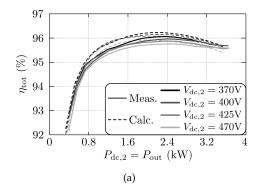

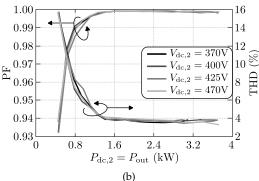

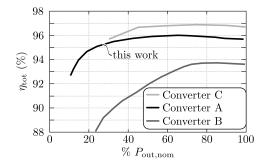

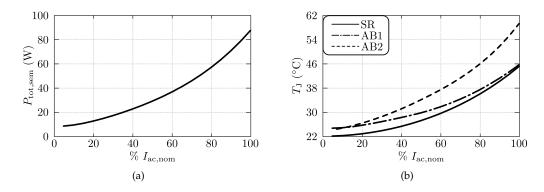

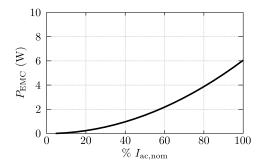

The curve  $Min_{\rm res}(j\omega)$  is obtained as the square root of the sum of the squares of the RMS values of all harmonic components  $V_{\rm meas}(j\omega)$  located within the resolution bandwidth (RBW) of the EMC test receiver [42].