Review

Not peer-reviewed version

# A Survey on Design Space Exploration Approaches for Approximate Computing Systems

<u>Sepide Saeedi</u>\*, <u>Ali Piri</u>, <u>Bastien Deveautour</u>, <u>Ian O'Connor</u>, <u>Alberto Bosio</u>, <u>Alessandro Savino</u>, Stefano Di Carlo

Posted Date: 7 October 2024

doi: 10.20944/preprints202410.0407.v1

Keywords: Approximate Computing; Design Space Exploration; Circuit Design; High Level Synthesis; Multiobjective Optimization

Preprints.org is a free multidiscipline platform providing preprint service that is dedicated to making early versions of research outputs permanently available and citable. Preprints posted at Preprints.org appear in Web of Science, Crossref, Google Scholar, Scilit, Europe PMC.

Copyright: This is an open access article distributed under the Creative Commons Attribution License which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Disclaimer/Publisher's Note: The statements, opinions, and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content.

Review

# A Survey on Design Space Exploration Approaches for Approximate Computing Systems

Sepide Saeedi <sup>1,\*</sup>, Ali Piri <sup>2</sup>, Bastien Deveautour <sup>3</sup>, Ian O'Connor <sup>2</sup>, Alberto Bosio <sup>2</sup>, Alessandro Savino <sup>1</sup>, and Stefano Di Carlo <sup>1</sup>

- Politecnico di Torino

- Univ Lyon, ECL, INSA Lyon, CNRS, UCBL, CPE Lyon, INL, UMR5270, 69130 Ecully, France

- <sup>3</sup> Nantes Université, CNRS, IETR UMR 6164, Nantes, France

- \* Correspondence: sepide.saeedi@polito.it

**Abstract:** Approximate Computing (AxC) has emerged as a promising paradigm to enhance performance and energy efficiency by allowing a controlled trade-off between accuracy and resource consumption. It is extensively adopted across various abstraction levels, from software to architecture and circuit levels, employing diverse methodologies. The primary objective of AxC is to reduce energy consumption for executing error-resilient applications, accepting controlled and inherently acceptable output quality degradation. However, harnessing AxC poses several challenges, including identifying segments within a design amenable to approximation and selecting suitable AxC techniques to fulfill accuracy and performance criteria. This survey provides a comprehensive review of recent methodologies proposed for performing Design Space Exploration (DSE) to find the most suitable AxC techniques, focusing on both hardware and software implementations. DSE is a crucial design process where system designs are modeled, evaluated, and optimized for various extra-functional system behaviors such as performance, power consumption, energy efficiency, and accuracy. A systematic literature review was conducted to identify papers that ascribe their DSE algorithms, excluding those relying on exhaustive search methods. This survey aims to detail the state-of-the-art DSE methodologies that efficiently select AxC techniques, offering insights into their applicability across different hardware platforms and use-case domains. For this purpose, papers were categorized based on the type of search algorithm used, with Machine Learning (ML) and Evolutionary Algorithms (EAs) being the predominant approaches. Further categorization is based on the target hardware, including Field-Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), general-purpose Central Processing Units (CPUs), and Graphics Processing Units (GPUs). A notable observation was that most studies targeted image processing applications due to their tolerance for accuracy loss. By providing an overview of techniques and methods outlined in existing literature pertaining to the DSE of AxC designs, this survey elucidates the current trends and challenges in optimizing approximate designs.

**Keywords:** approximate computing; design space exploration; circuit design; high level synthesis; multi-objective optimization

### 1. Introduction

As large-scale application domains like scientific computing, social media, and financial analytics continue to expand, the computational and storage requirements of modern systems have surpassed the available resources. In the upcoming decade, it is anticipated that the amount of data managed by global data centers will increase by fifty times, while the number of processors will only grow by a factor of ten [1]. This indicates that the demand for performance will soon outstrip resource allocations.

Furthermore, Information and Communication Technology (ICT) devices and services currently contribute significantly to the world's overall energy consumption, with projections indicating that their energy demand will rise to nearly 21% by 2030 [2] Consequently, it becomes evident that relying solely on over-provisioning resources will not suffice to address the impending challenges facing the computing industry.

In recent decades, significant technological advancements and increasing computational demands have driven a remarkable reduction in the size of integrated circuits and computing systems. This

downscaling of CMOS technology has resulted in several key benefits, such as enhanced computational performance, improved energy efficiency, and the ability to increase the number of cores per chip. Smaller transistors allow for faster switching speeds, enabling higher clock frequencies, which translates to quicker data processing and more powerful computing systems. Additionally, as transistors shrink, the power required to switch them can be reduced, leading to lower overall energy consumption, which is crucial for mobile and battery-operated devices.

However, CMOS downscaling is not without its drawbacks. As transistors continue to shrink, the benefits of reduced supply voltage become less significant, and the leakage current (unwanted current that flows even when the transistor is off) becomes more pronounced, leading to higher static power consumption. Moreover, the exponential increase in power consumption due to higher clock frequencies has introduced thermal challenges, as more energy is dissipated as heat, which can damage the chip and reduce its lifespan. The combination of these factors means that the traditional benefits of CMOS scaling are diminishing, and the ability to further increase the number of cores per chip is constrained by power and thermal limits. Consequently, as CMOS technology reaches its scaling limits, it becomes imperative to explore alternative approaches, such as new materials, 3D stacking, or novel architectures, to continue improving computing efficiency without exacerbating these power and thermal issues [3].

In addition to the trends mentioned above, the nature of the tasks fueling the demand for computing has evolved across the computing spectrum, spanning from mobile devices to the cloud. Within data centers and the cloud, the impetus for computing stems from the necessity to efficiently manage, organize, search, and derive conclusions from vast datasets. In contrast, the predominant computing demand for mobile and embedded devices arises from the desire for more immersive media experiences and more natural, intelligent interactions with users and the surrounding environment. Although computational errors are generally undesirable, a common thread runs through this spectrum: these applications are not primarily concerned with computing precise numerical outputs. Instead, "correctness" is defined as generating results that are sufficiently accurate to deliver an acceptable user experience [4].

These applications inherently possess a resilience towards errors, meaning they can produce satisfactory outputs even when some of their computations are carried out in an approximate manner [5]. For instance, in search and recommendation systems, there is not always a single definitive or golden" result; instead, multiple answers falling within a specific range are considered acceptable. Additionally, iterative applications processing extensive data sets may terminate convergence prematurely or employ heuristics [6]. In many machine learning applications, even if a golden result exists, the most advanced algorithms may not be able to achieve it. Consequently, users often have to settle for results that are reasonably inaccurate but still adequate. Furthermore, applications such as multimedia, wireless communication, speech recognition, and data mining exhibit a degree of tolerance toward errors. Human perceptual limitations signify that such errors may not significantly affect applications like image, audio, and video processing. Another example pertains to applications dealing with noisy input data (e.g., image and sensor data processing, and speech recognition). The noise in the input naturally leads to imprecise results, and approximations have a similar impact. In simpler terms, applications that can handle noisy inputs also possess the capability to withstand approximations [7–9]. Finally, some applications utilize computational patterns like aggregation or iterative refinement, which can mitigate or compensate for the effects of approximations.

An encouraging approach to enhance computing efficiency is Approximate Computing (AxC). The concept of AxC encompasses a wide array of techniques that capitalize on the inherent error resilience of applications, ultimately leading to improved efficiency across all layers of the computing stack, ranging from the fundamental transistor-level design to software implementations. These techniques can have varying impacts on both the hardware and the quality of the output. AxC capitalizes on the existence of data and algorithms that can tolerate errors, as well as the limitations in the perception of end-users. It strategically balances accuracy against the potential for performance

improvements or energy savings. In essence, it takes advantage of the gap that often exists between the level of accuracy that computer systems can provide and the level of accuracy required by the specific application or the end-users. This required accuracy is typically much lower than what the computer systems can deliver.

Leveraging AxC involves addressing a few aspects and challenges. The first challenge is identifying the segments within the targeted software or hardware component that can be candidates for approximation. Identifying segments of code or data that can be approximated may necessitate a comprehensive understanding of the application on behalf of the designer.

The second challenge is implementing the AxC technique to introduce approximations. On the one hand, there is a limit to the accuracy degradation that can be introduced so the output remains acceptable. On the other hand, the level of accuracy degradation and the performance improvements or energy savings varies depending on the selected AxC technique. Hence, available AxC techniques should be evaluated and compared to find the most suitable AxC technique tailored for a target application or design.

The next challenge is choosing the suitable error measurement criteria, often tailored to the particular application, and executing the actual error assessment process to ensure that the output adheres to the predefined quality standards [5]. The error assessment usually involves simulating both the precise and approximate versions of applications. However, alternative methods like Bayesian inference [10,11] or Machine Learning (ML)-based approaches [12] have been put forth in the scientific literature.

A Design Space Exploration (DSE) can be performed to address all the previously mentioned challenges. The goal of performing a DSE is to determine the most optimal approximate configurations from those generated by applying a given set of approximation techniques to the design. Hence, the DSE approaches can help systematically evaluate different approximate designs to choose the most suitable AxC techniques and, consequently, the best configurations for any given combination of AxC techniques. Early DSE approaches either combine multiple design objectives into a single-objective optimization problem or optimize a solitary parameter while keeping the remaining variables constant. More recent research, as seen in published works, has tackled circuit design issues by considering a Multi-objective Optimization Problem (MOP) to seek out Pareto-optimal approximate circuit configurations [13]. Regrettably, these approaches predominantly concentrated on simple systems, specifically arithmetic components like adders and multipliers, as they form the foundational components for more intricate designs [14].

This paper aims to cover different DSE approaches leveraged in comparing approximate versions of a target application or design. The structure of this paper is as follows: Firstly, section 2 provides a background on the AxC techniques and DSE approaches. Then, in section 3, the search methodology to find related studies and categorizing them, is explained. In section 4 DSE approaches to compare and choose suitable AxC techniques are reviewed and compared. Finally, a conclusion is provided in section 5.

# 2. Background

AxC represents an emerging paradigm enabling the development of significantly energy-efficient computing systems, including diverse hardware accelerators designed for tasks like image filtering, video processing, and data mining. This approach leverages the inherent error resilience of many applications, allowing for a trade-off between accuracy and energy efficiency [15]. This trade-off can be accomplished through various means, spanning from transistor-level design to software implementations, each with distinct effects on hardware integrity and output quality.

The following sections provide an overview of how different AxC techniques can be classified, followed by a description of the DSE paradigm.

#### 2.1. Classification of Approximate Computing Techniques

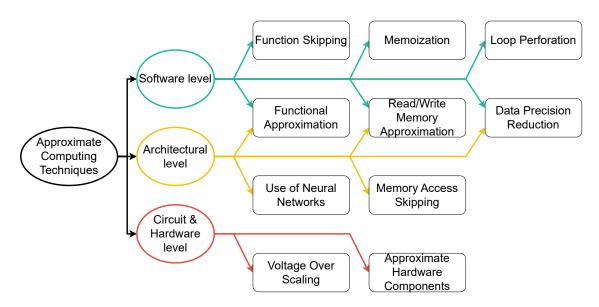

AxC techniques can be classified into three groups based on their implementation level: software, architecture, and hardware, with specific techniques applicable at multiple levels, as shown in Figure 1. For instance, memory read approximation can be achieved through pure software approaches or within memory control units. While Figure 1 highlights some commonly utilized approximation methods from the existing literature, it is essential to note that there exist numerous ways to approximate an application, and the precise definition of what constitutes an approximation is a subject of debate [9,16].

Figure 1. A classification of the AxC techniques.

## 2.1.1. Software-Level Approximate Computing Techniques

The loop-perforation technique serves as a notable example of software approximation, enabling the generation of valuable outcomes without executing every iteration of an iterative code [17]. Similarly, function-skipping involves bypassing specific code blocks during runtime based on predefined conditions [18–20]. Another software approximation method involves reducing the bit-width used for data representation, primarily impacting the memory footprint of the application. While reducing data precision can also affect the execution time and performance of the software, its impact relies on the hardware implementation of operations utilized by the application [21,22].

Memoization is a technique that optimizes performance and conserves energy by storing previously computed values for specific inputs. When the same input is re-encountered later, the stored value is reused, eliminating the need for redundant computation. This trade-off between computation and memory use enhances efficiency and reduces resource consumption [23].

Read/write memory approximation targets data loaded from or written to memory, as well as the memory access operations themselves. This method, commonly applied in video and image processing applications, relaxes accuracy requirements to minimize memory operations [24–26].

Functional approximation focuses on identifying components within algorithms that have a minimal impact on final accuracy. Energy consumption can be reduced by approximating these less critical components, leading to improved execution time performance [27,28].

# 2.1.2. Architectural-Level Approximate Computing Techniques

Neural Networks (NNs) can learn the behavior of a standard function implementation by analyzing how it responds to various inputs. Through software-hardware co-design, traditional code can be transformed into NNs with lower output accuracy but enhanced execution time and performance [29].

Memory access skipping combines memoization and function skipping techniques to omit uncritical memory accesses without significant accuracy loss. Approximate NNs leverage this approach to skip reading entire weight matrix rows for non-critical neurons, reducing energy consumption and improving performance [30].

# 2.1.3. Circuit and Hardware-Level Approximate Computing Techniques

Voltage scaling techniques reduce energy consumption in digital circuits by adjusting the supply voltage at the circuit level. This adjustment directly impacts computation timing and power efficiency, exploiting the inherent error resilience of applications to achieve significant energy savings while maintaining acceptable performance levels [31]. Dynamic Voltage Scaling (DVS) adjusts the supply voltage to decrease power dissipation while maintaining computational accuracy within safe operational limits, balancing power savings against performance degradation [32]. Dynamic Voltage and Frequency Scaling (DVFS) extends this concept by simultaneously adjusting both the voltage and the operating frequency, providing finer control over power and performance trade-offs [31]. In contrast, Voltage Over Scaling (VOS) aggressively reduces the supply voltage beyond nominal levels, intentionally allowing timing violations that can introduce errors in computations [33,34]. While DVS and DVFS ensure accurate results within controlled performance constraints, VOS prioritizes further energy savings by permitting computational inaccuracies, making it suitable for scenarios where approximate results are acceptable.

Hardware-based approximation techniques often employ alternative implementations of arithmetic operators. For instance, variable approximation modes on operators represent one such approach. Hardware approximation also finds application in the image processing domain through approximate compressors [9,16].

Inexact hardware can provide approximation at the hardware level, with numerous examples from the literature of approximate arithmetic circuits designed to balance performance and accuracy. Adders, multipliers, and dividers significantly influence performance and energy efficiency across various computing tasks since they are the most frequent and vital arithmetic components within a processor. Pursuing enhanced speed, power efficiency, and error resilience in numerous applications such as multimedia processing, recognition systems, and data analytics has propelled the advancement of approximate arithmetic design [3].

The aforementioned AxC techniques are a few examples of the many approximation techniques implemented at various abstraction levels. Due to this complexity, the challenges mentioned in the previous section need to be addressed, and DSE emerges as the most promising solution thus far.

#### 2.2. Precision Metrics

Various precision metrics have been proposed to describe and evaluate the effectiveness of AxC techniques and methodologies, as detailed in Table 1.

Error Distance (ED) and Error Probability (EP) are basic error metrics used for measuring the accuracy degradation while applying AxC techniques. ED is the distance between the correct output and the approximate output of a circuit for each scenario and EP is the probability of having a wrong answer which is calculated by the number of wrong answers over the number of all input scenarios. These metrics are formulated in equations (1) and (2) respectively.

$$ED = |O_{AxC}^{(i)} - O_{Acc}^{(i)}| \tag{1}$$

$$EP = \frac{\sum_{i=1}^{N} 1(O_{AxC}^{(i)} \neq O_{Acc}^{(i)})}{N}$$

(2)

where N is the number of possible scenarios,  $O_{Acc}^{(i)}$  and  $O_{AxC}^{(i)}$  are the accurate and approximate outputs of  $i^{th}$  scenario respectively, and  $P(S_i)$  is the probability of the  $i^{th}$  scenario happening.

Mean Error Distance (MED) is the average of all the error distances which is calculated as equation (3).

$$MED = \sum_{i=1}^{N} \frac{|O_{AxC}^{(i)} - O_{Acc}^{(i)}|}{N} \cdot P(S_i)$$

(3)

Mean Relative Error Distance (MRED) is the average of error distances relative to the correct answers formulated as equation (4).

$$MRED = \sum_{i=1}^{N} \frac{|O_{AxC}^{(i)} - O_{Acc}^{(i)}|}{|O_{Acc}^{(i)}|} \cdot P(S_i)$$

(4)

Absolute Worst-Case Error (AWCE) which is defined as the largest error distance that can happen, formulated in equation (5).

$$AWCE = \max_{\forall i} |O_{AxC}^{(i)} - O_{Acc}^{(i)}|$$

(5)

Mean Squared Error (MSE) is the average of the squares of the errors between the approximate values and the accurate values. MSE is formulated as equation (6).

$$MSE = \sum_{i=1}^{N} \frac{(O_{AxC}^{(i)} - O_{Acc}^{(i)})^2}{N} \cdot P(S_i)$$

(6)

Hamming Distance (HD) is a metric used to measure the difference between two strings of equal length. It is defined as the number of positions at which the corresponding symbols are different. For example, consider the binary strings "1011101" and "1001001". The HD is 2 because there are two positions where the strings differ (second and fourth positions).

Error Rate (ER) measures the number of erroneous results over the total number of results. In equation (7),  $N_{err}$  represents the number of erroneous results, while the  $N_{tot}$  represents the total number of results.

$$ER = \frac{N_{err}}{N_{tot}} \tag{7}$$

Bit Error Ratio (BER) is the number of bit errors per unit of time, calculated by dividing the number of bit errors by the total number of bits transferred during a given time interval. BER is a unitless performance measure and is often expressed as a percentage. It is a critical metric for evaluating the accuracy and reliability of data transmission in communication systems. In equation (8),  $N_{bit\_err}$  represents the number of erroneous bits, while the  $N_{bit\_tot}$  represents the total number of bits.

$$BER = \frac{N_{bit\_err}}{N_{bit\_tot}}$$

(8)

Peak Signal-to-Noise Ratio (PSNR) is a metric that evaluates the quality of reconstructed images or videos by comparing them to their originals. It measures the ratio between the maximum possible signal power and the power of corrupting noise, expressed in decibels (dB). Higher PSNR values indicate better quality. PSNR is formulated as equation (9) where *R* is the maximum possible pixel value (e.g., 255 for an 8-bit image), and *MSE* corresponds to the MSE between the original and the distorted image.

$$PSNR = 10\log_{10}\left(\frac{R^2}{MSE}\right) \tag{9}$$

Structural Similarity Index Measure (SSIM) measures image quality by comparing structural information, luminance, and contrast between an image and a reference. Unlike PSNR, SSIM focuses

on perceptual similarity. SSIM values range from -1 to 1, with 1 indicating perfect similarity. SSIM is defined in equation (10), where x and y are the two images being compared. The parameters  $\mu_x$  and  $\mu_y$  represent the mean pixel values of images x and y, respectively.  $\sigma_x^2$  and  $\sigma_y^2$  are the variances of x and y, while  $\sigma_{xy}$  denotes the covariance between the two images. The constants  $C_1$  and  $C_2$  are included to stabilize the division, particularly when the denominators approach zero, and are typically defined as  $C_1 = (K_1 L)^2$  and  $C_2 = (K_2 L)^2$ , where L is the dynamic range of pixel values (e.g., 255 for 8-bit images), and  $K_1$  and  $K_2$  are small constants (commonly set to 0.01 and 0.03, respectively).

SSIM

$$(x,y) = \frac{(2\mu_x \mu_y + C_1)(2\sigma_{xy} + C_2)}{(\mu_x^2 + \mu_y^2 + C_1)(\sigma_x^2 + \sigma_y^2 + C_2)}$$

(10)

Mean Pixel Difference (MPD) is a simpler metric that calculates the average absolute difference in pixel values between two images. Lower MPD values indicate higher similarity. MPD is formulated as equation (11), where N is the number of pixels,  $P_i$  is the original pixel value, and  $Q_i$  is the compared pixel value.

$$MPD = \frac{1}{N} \sum_{i=1}^{N} |P_i - Q_i|$$

(11)

Binary classification is widely used in applied machine learning across fields like medicine, biology, meteorology, and malware analysis. Performance metrics are crucial in research to evaluate and report the effectiveness of classification models. In binary classification, a two-by-two confusion matrix captures the model's performance, consisting of True Positives (TPs), True Negatives (TNs), False Positives (FPs), and False Negatives (FNs). Key metrics such as classification accuracy, precision, and recall are derived from these values [35].

Classification accuracy is the proportion of correct classifications out of all classifications, both positive and negative. Classification accuracy is formulated as equation (12) and reflects the overall correctness of the classifier. A perfect model has an accuracy of 1.0 (or 100%), meaning no FPs or FNs.

Classification Accuracy =

$$\frac{TP + TN}{TP + TN + FP + FN}$$

(12)

Recall or TP rate is the proportion of actual positives that were correctly identified. This metric is formulated in (13) and measures the model's ability to detect all positive instances. A perfect recall is 1.0, indicating a 100% detection rate with no FNs.

$$Recall = \frac{TP}{TP + FN} \tag{13}$$

False positive rate (FPR), also known as the probability of false alarm, is the proportion of actual negatives that were incorrectly classified as positives. This metric is formulated in equation (14) and indicates the likelihood of misclassifying a negative instance as positive. A perfect model has an False Positive Rate (FPR) of 0.0 (or 0%), meaning no FPs.

$$FPR = \frac{FP}{FP + TN} \tag{14}$$

The precision metric is the proportion of correct positive classifications. This metric is formulated in equation (15). Precision assesses the accuracy of the positive predictions made by the model. A perfect precision score is 1.0, achieved when there are no FPs. While Precision improves as FPs decrease, Recall improves as FNs decrease.

$$Precision = \frac{TP}{TP + FP}$$

(15)

**Table 1.** Precision metrics in Approximate Computing [36].

| Metric                                                    | Description                                                                                                                                                                                                                                                                                                              | Application Domain                                           |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ER EP MED/MRED NMED/NMRED Max ED/RED PED/PRED MSE RMSE HD | Error Rate – Erroneous results per total results Error Probability – Probability of error occurrence Mean (Relative) Error Distance Normalized Mean (Relative) Error Distance Maximum (Relative) Error Distance Probability of (Relative) Error Distance > X Mean Squared Error Root Mean Squared Error Hamming Distance | General Computing                                            |

| BER<br>PER                                                | Bit Error Ratio – Bit errors per total received bits<br>Packet Error Ratio – Incorrect packets per total re-<br>ceived packets                                                                                                                                                                                           | Digital Systems, Telecommunications                          |

| PSNR<br>SSIM<br>MPD                                       | Peak Signal-to-Noise Ratio – Quality measurement<br>between images<br>Structural Similarity – Quality measurement be-<br>tween images<br>Mean Pixel Difference                                                                                                                                                           | Image Processing, Video<br>Processing, Computer Vi-<br>sion  |

| Classif. Accuracy<br>Precision<br>Recall                  | Correct classifications per total classifications<br>Relevant instances per total retrieved instances<br>Relevant instances per total relevant instances                                                                                                                                                                 | Pattern Recognition, Information Retrieval, Machine Learning |

#### 2.3. Design Space Exploration

DSE is a systematic process of analyzing and evaluating various design alternatives to find optimal solutions that meet specific requirements and constraints. In the context of embedded system design and AxC, DSE can be defined as systematically evaluating and analyzing various design alternatives to find optimal solutions that balance performance, power consumption, and accuracy trade-offs. The goal of DSE is to find the best approximate versions of an application or circuit that provide significant gains in efficiency (power, speed, area) while maintaining acceptable output quality for the target application [37,38].

Designing modern embedded computer systems presents numerous formidable challenges, as these systems typically must adhere to various strict and sometimes conflicting design criteria. Embedded systems aimed at mass production and battery-powered or passive-cooling devices require cost-effectiveness and energy efficiency. In safety-critical applications like avionics and space technologies, dependability is paramount, especially with the growing autonomy of systems. Furthermore, many of these systems are expected to support multiple applications and standards simultaneously, necessitating real-time performance. For instance, mobile devices must accommodate various communication protocols and digital content coding standards [39].

Additionally, these systems must offer flexibility for future updates and extensions while maintaining programmability despite the necessity of implementing significant portions in dedicated hardware blocks due to performance, power consumption, and cost constraints. Consequently, modern embedded systems often adopt a heterogeneous multi-processor architecture comprising a mix of programmable cores and dedicated hardware blocks for time-sensitive tasks. This trend has led to the development of integrated heterogeneous Multi-Processor System-on-Chip (MPSoC) architectures [40].

To address the intricate design challenges inherent in such systems, a new design methodology known as system-level design has emerged over the past 15 to 20 years [41]. Its primary objective is to elevate the level of abstraction in the design process, thereby enhancing design productivity. Central to this approach are MPSoC platform architectures, which facilitate the reuse of IP components, along with the concept of high-level system modeling and simulation [42,43].

High-level system modeling and simulation enable the representation of platform components and their interactions at a refined level of abstraction. These models streamline the modeling effort,

optimize execution speed, and are thus invaluable for early-stage DSE. Various design alternatives can be examined during DSE, including the number and type of processors utilized, the interconnection network employed, and the spatial and temporal binding of application tasks to processor cores [44,45].

Initiating DSE at the early stages of the design process is crucial, as the choices made can significantly impact the success or failure of the final product. However, the challenges the large design space poses, particularly in its early stages, cannot be overlooked. For instance, when considering different mappings of application tasks to processing resources to optimize system performance or power consumption, the design space expands exponentially with the number of tasks and processors, presenting an NP-hard problem [46]. Consequently, notable research has focused on developing efficient and effective DSE methods in recent years, aiming to tackle the complexities of exploring such expansive design spaces [46].

DSE approaches can be categorized and classified based on many aspects [47]. However, one of the possible classifications is categorizing a DSE as single-objective or multi-objective. Multi-objective DSE refers to simultaneously optimizing multiple conflicting objectives or goals during the design phase. These objectives typically include performance, power consumption, area utilization, reliability, and cost in circuit design. Unlike single-objective optimization, where a single criterion is optimized at the expense of others, multi-objective DSE aims to find a set of trade-off solutions, known as the Pareto-optimal front, where improving one objective comes at the cost of degrading another. That is why finding an optimal solution that optimizes all objectives is impossible. Such a solution does not exist, and this happens when the objectives conflict with each other. Therefore, optimal decisions need to be taken with trading-off between design criteria. [45].

When applying AxC techniques to the design, what makes choosing among different AxC techniques difficult is that all of them can be employed together, requiring the evaluation of the impact of each combination of AxC techniques on the overall computation accuracy. The two main approaches for evaluating this impact comprise executing different approximated versions of the application several times with different configurations [48,49] or devising modeling techniques to simulate different approximated versions of the application in a time-optimized fashion [50,51]. The disadvantage of the first approach is that the evaluation time increases when the exploration reaches an exhaustive search. Applying pruning techniques to the exploration space reduces the exploration time to the application execution time, at best. Conversely, the second approach is more suitable for estimating the impact of AxC techniques on the application computation accuracy because it is faster than the first approach, even though it costs an error margin in the computation accuracy evaluation.

# 3. Literature Search Methodology

The objective of this survey was to systematically identify and classify existing literature on DSE methodologies proposed for finding the most suitable AxC techniques to be applied to a program or hardware design.

The initial search focused on identifying papers that provided a detailed description of the algorithms used for DSE. To maintain a high standard of relevance, only studies that clearly explained their DSE methodologies were included. Papers that utilized exhaustive search methods were deliberately excluded, as the survey aimed to highlight more sophisticated and efficient approaches.

Once the relevant papers were identified, they were categorized based on the type of search algorithm employed for conducting the DSE. Within each category, the papers were further sorted based on the target hardware for which the DSE was conducted. For instance, some studies focus on Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs), particularly in the context of designing accelerators using AxC techniques. Some other studies do not specify a particular target hardware, indicating their proposed methods can be applied universally across different platforms. Additionally, some papers address hardware or software level approximation for Graphics Processing Units (GPUs).

This survey also considers the application domains of the programs targeted for approximation. The application domains usually considered in most studies for selecting benchmarks include image processing, signal processing, scientific computing, financial analysis, Natural Language Processing (NLP), 3D gaming, and robotics.

Additionally, information about employed AxC techniques was extracted from each study to better compare different studies based on the AxC techniques applied at software, architectural, or hardware levels.

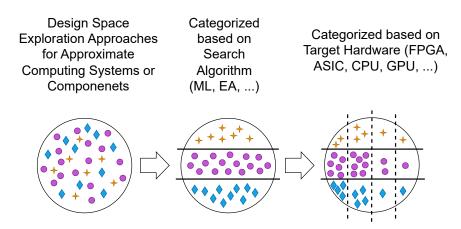

In a nutshell, this survey aimed to identify and evaluate the proposed DSE methods employed to explore the extensive design space of approximate versions of a design. The focus was on understanding whether these methods were well-known search algorithms or custom approaches. Following this structured and systematic methodology, the survey provides a comprehensive overview of the current state-of-the-art proposed DSE methodologies for finding the most suitable AxC techniques, highlighting the diversity of approaches and their applicability to various hardware platforms and application domains. Figure 2 shows the aforementioned process of categorizing different studies.

Figure 2. Literature search methodology.

#### 4. Comparison and Analysis

This section provides an overview and comparison of the proposed DSE approaches in the literature for applying AxC techniques to programs or hardware designs. Though many different search algorithms have been proposed in the literature to explore the vast design space of approximate programs or hardware designs, two categories of algorithms are commonly leveraged: ML algorithms and Evolutionary Algorithms (EAs). ML approaches often leverage data-driven techniques to predict and explore optimal design configurations, while EAs use bio-inspired strategies such as Genetic Algorithms (GAs) to navigate the design space.

Table 2 provides information about the research works that took an ML approach to perform the DSE, while Table 3 includes information about the research works that leveraged EAs to perform the DSE. All the remaining research works that perform the DSE using other heuristic algorithms or combining different optimization algorithms are listed in Tables 4 and 5. While Tables 2, 3, 4, 5, and 6 provide an overview to allow comparison among different studies based on the employed search algorithm, target hardware, and use case domain, Tables 7, 8, 9, 10, and 11 provide an overview of the same sets of studies to allow comparison among different studies based on AxC techniques applied in each study.

$\textbf{Table 2.} \ \ Research \ works \ using \ ML-based \ search \ algorithms \ to \ perform \ the \ DSE.$

| Year | Ref. | Target                                                                                       | Use Case                                                                                                                                                                  | Benchmarks                                                                                | Search                               |

|------|------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------|

|      |      | Hardware                                                                                     | Domains                                                                                                                                                                   |                                                                                           | Algorithm                            |

| 2018 | [52] | FPGA                                                                                         | image processing                                                                                                                                                          | iris scanning                                                                             | RL                                   |

| 2021 | [53] | FPGA                                                                                         | image processing                                                                                                                                                          | kernel-based Gaussian blur filter                                                         | MBO                                  |

| 2019 | [12] | Accelerator (ASIC)                                                                           | image processing                                                                                                                                                          | Sobel, and Gaussian blur filters (one with fixed coefficients, and one with a 3x3 kernel) | ML-based heuristic                   |

| 2023 | [54] | Accelerator (ASIC)                                                                           | signal and image<br>processing, and<br>general arithmetic                                                                                                                 | Adder Tree,<br>RGB2gray, FIR,<br>and Gaussian blur<br>filters                             | AI-based heuristic:<br>modified MCTS |

| 2021 | [55] | FPGA, ASIC,<br>General-purpose<br>computing system                                           | image processing                                                                                                                                                          | RGB2GRAY, Ternary sum. FIR, image sharpening, and Gaussian blur filters                   | ML                                   |

| 2015 | [56] | General-purpose<br>hardware (hetero-<br>geneous mobile,<br>tablet, and server<br>processors) | video encoder, financial analysis, image processing, search engine, digital signal processing, netlist place-and-route, image similarity search, and clustering algorithm | x264, Swaptions, Bodytrack, Swish++, Radar, Canneal, Ferret, and Streamcluster            | RL                                   |

| 2020 | [57] | General-purpose<br>CPU and DNN<br>accelerator                                                | DNNs for Image<br>and Digit Classifi-<br>cation                                                                                                                           | AlexNet, SimpleNet, LeNet, MobileNet, ResNet-20, 10-Layers, and VGG-11/16                 | RL                                   |

| 2023 | [38] | General-purpose<br>CPU                                                                       | ML, digital signal processing, and image processing                                                                                                                       | Matrix Multiplication, and FIR filter                                                     | RL                                   |

**Table 3.** Research works using EAs as a search algorithm to perform the DSE.

| Year | Ref.    | Target             | Use Case             | Benchmarks         | Search            |

|------|---------|--------------------|----------------------|--------------------|-------------------|

|      |         | Hardware           | Domains              |                    | Algorithm         |

| 2021 | [58,59] | FPGA               | Image Processing     | pixel-streaming    | GA                |

|      |         |                    |                      | pipeline           |                   |

| 2023 | [60]    | FPGA-based         | HEVC                 | Multiplierless     | ES algorithm, and |

|      |         | approximate accel- |                      | MCM                | NSGA-II           |

|      |         | erator             |                      |                    |                   |

| 2022 | [61]    | Accelerator (FPGA  | Image processing     | DCT                | NSGA-II           |

|      |         | and ASIC)          | (JPEG compres-       |                    |                   |

|      |         |                    | sion)                |                    |                   |

| 2014 | [62]    | General-purpose    | scientific comput-   | FFT, SOR, MC,      | GA                |

|      |         | CPU (implied)      | ing, 3D gaming,      | SMM, LU, Zxing,    |                   |

|      |         | _                  | 3D image render-     | JMEint, Imagefill, |                   |

|      |         |                    | ing, signal, and im- | and raytracer      |                   |

|      |         |                    | age processing       |                    |                   |

| 2023 | [63]    | GPU                | image classifica-    | MobileNetV2, and   | NAS algorithms:   |

|      |         |                    | tion using CNNs      | ResNet50V2         | EvoApproxNAS      |

|      |         |                    |                      |                    | (based on NSGA-   |

|      |         |                    |                      |                    | II), and Google   |

|      |         |                    |                      |                    | Model Search      |

Table 4. Research works using custom search algorithms to perform the DSE.

| Year | Ref. | Target               | Use Case             | Benchmarks                         | Search             |

|------|------|----------------------|----------------------|------------------------------------|--------------------|

|      |      | Hardware             | Domains              |                                    | Algorithm          |

| 2016 | [64] | ASIC, and FPGA       | HEVC                 | SAD                                | Custom             |

| 2020 | [65] | ASIC, and FPGA       | image classifica-    | ResNet-                            | Custom             |

|      |      |                      | tion using DNNs      | 18/34/38/74,                       |                    |

|      |      |                      |                      | MobileNetV2,                       |                    |

|      |      |                      |                      | and Transformer-                   |                    |

|      |      |                      |                      | base/WikiText-103                  |                    |

| 2016 | [66] | ASIC (implied)       | handwriting recog-   | Array Multiplier,                  | Heuristic          |

|      |      |                      | nition, general      | Carry Lookahead                    |                    |

|      |      |                      | arithmetic, multi-   | Adder, Kogge                       |                    |

|      |      |                      | media, signal, and   | Stone Adder,                       |                    |

|      |      |                      | image processing     | Multiple and Ac-                   |                    |

|      |      |                      |                      | cumulate, SAD,                     |                    |

|      |      |                      |                      | Euclidean distance,                |                    |

|      |      |                      |                      | DCT, FFT, and FIR.                 |                    |

|      |      |                      |                      | All used in a DNN                  |                    |

|      |      |                      |                      | vector accelerator                 |                    |

| 2019 | [67] | ASIC (implied)       | HEVC                 | SAD                                | Custom             |

| 2021 | [68] | ASIC (implied)       | image processing     | Sobel, FIR, and                    | Custom             |

|      |      |                      |                      | Gaussian blur                      |                    |

|      |      |                      |                      | filters, a ReLu                    |                    |

|      |      |                      |                      | Neuron, Euclidean                  |                    |

| 2015 | [(0] | VII CI ( 1           |                      | distance                           |                    |

| 2017 | [69] | VLSI systems and     | image processing     | average number                     | Custom             |

|      |      | HLS, aligning with   |                      | calculator, inverse                |                    |

|      |      | ASIC design          |                      | DCT calculator,                    |                    |

|      |      |                      |                      | Sobel, FIR, in-                    |                    |

|      |      |                      |                      | terpolation and decimation filters |                    |

| 2020 | [70] | HLS tools for accel- | Image and acceptance |                                    | TC with material   |

| 2020 | [70] |                      | Image processing     | Sobel and Sharpen filters          | TS with potential  |

|      |      | erator design        |                      | inters                             | integration of GAs |

Table 5. Research works using custom search algorithms to perform the DSE (continued.)

| Year | Ref.    | Target                                  | Use Case                                                                                                                                                                       | Benchmarks                                                                                                                                                                                             | Search              |

|------|---------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2018 | [71]    | Hardware accelera-                      | Domains ML, digital signal                                                                                                                                                     | Matrix Multiplica-                                                                                                                                                                                     | Algorithm<br>Custom |

| 2010 | [71]    | tor (ASIC implied)                      | processing, and                                                                                                                                                                | tion, Sobel filter,                                                                                                                                                                                    | Custom              |

|      |         |                                         | image processing                                                                                                                                                               | and DCT                                                                                                                                                                                                |                     |

| 2016 | [72]    | ML accelerator (ASIC)                   | Image Processing,<br>and NLP / Text<br>Classification                                                                                                                          | Eye, and Face<br>detection. Optical<br>digit, Digit, Web-<br>page, and Text<br>classification                                                                                                          | GD                  |

| 2021 | [73,74] | ASIC (AI Accelerator)                   | image processing,<br>NLP, and speech<br>recognition                                                                                                                            | VGG16, ResNet50,<br>InceptionV3,<br>InceptionV4,<br>MobileNetV1,<br>SSD300, YoloV3,<br>YoloV3-Tiny,<br>BERT, a 2-layer<br>LSTM, and a 4-<br>layer bidirectional<br>LSTM                                | Custom              |

| 2016 | [75]    | NPU (ASIC)                              | financial analysis, robotics, 3D gaming, image compression, signal, and image processing                                                                                       | Blackscholes, FFT,<br>Inversek2j, Jmeint,<br>JPEG, Sobel filter                                                                                                                                        | Custom              |

| 2019 | [76]    | Not specified (implied general-purpose) | image processing                                                                                                                                                               | Matrix Multiplication, and FIR filter                                                                                                                                                                  | Custom              |

| 2016 | [77]    | GPU                                     | For GPU: ML, signal processing (pattern recognition), image processing, medical imaging, scientific computing, and web mining. For CPU: scientific computing and optimization. | For GPU: Back-prop, Fastwalsh, Gaussian, Heartwall, Matrix-mul, Particle filter, Similarity score, S.reduce, S.srad2, and String match. For CPU: Bwaves, CactusADM, FMA3D, GemsFDTD, Soplex, and Swim. | Custom              |

**Table 6.** Research works that perform the DSE for approximate functions design space instead of a complete system.

| Year | Ref. | Target                                                             | Use Case                                                                                        | Benchmarks                                                                                              | Search    |

|------|------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------|

|      |      | Hardware                                                           | Domains                                                                                         |                                                                                                         | Algorithm |

| 2021 | [78] | FPGA (also ASIC implied)                                           | NA                                                                                              | apex2, b12, clip,<br>duke2, and vg2<br>benchmarks from<br>IWLS'93 Bench-<br>mark Set                    | NSGA-II   |

| 2014 | [79] | FPGA and ASIC (implied)                                            | NA                                                                                              | Ripple Carry,<br>Carry Lookahead,<br>and Kogge Stone<br>Adders. Wallace,<br>and Dadda Multi-<br>pliers. | Custom    |

| 2021 | [80] | FPGA and ASIC<br>(designing fault-<br>tolerant architec-<br>tures) | safety-critical ap-<br>plications: Quadru-<br>ple Approximate<br>Modular Redun-<br>dancy (QAMR) | generic combina-<br>tional circuits                                                                     | NSGA-II   |

| 2021 | [81] | FPGA and ASIC (implied)                                            | NA                                                                                              | approximate<br>adders, multipliers,<br>divisor, barrel<br>shifter, Sine, and<br>Square                  | Heuristic |

| 2022 | [82] | FPGA                                                               | NA                                                                                              | approximate<br>adders, multipliers,<br>decoders, and<br>ALUs                                            | NSGA-II   |

**Table 7.** AxC techniques in research works using ML-based search algorithms to perform the DSE.

| Year | Ref.  | Target                                                                                              | Benchmarks                                                                                |                                                                                                                                                    | AxC Techniques |                                           |

|------|-------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------|

| 1cui | 1101. | Hardware                                                                                            | Zenemiano                                                                                 | Software                                                                                                                                           | Architectural  | Hardware                                  |

| 2018 | [52]  | FPGA                                                                                                | iris scanning                                                                             | reducing<br>search win-<br>dow size and<br>the region<br>of interest in<br>iris images,<br>reducing the<br>parameters of<br>iris segmenta-<br>tion | NA             | reducing the<br>filter kernel<br>size     |

| 2021 | [53]  | FPGA                                                                                                | kernel-based<br>Gaussian blur<br>filter                                                   | approximation of the window size, mode, and stride length for convolution kernels                                                                  | NA             | approximate<br>multipliers,<br>and adders |

| 2019 | [12]  | Accelerator<br>(ASIC)                                                                               | Sobel, and Gaussian blur filters (one with fixed coefficients, and one with a 3x3 kernel) | NA                                                                                                                                                 | NA             | approximate<br>adders and<br>multipliers  |

| 2023 | [54]  | Accelerator<br>(ASIC)                                                                               | Adder Tree,<br>RGB2gray, FIR,<br>and Gaussian<br>blur filters                             | NA                                                                                                                                                 | NA             | approximate<br>adders and<br>multipliers  |

| 2021 | [55]  | FPGA, ASIC,<br>General-<br>purpose<br>computing<br>system                                           | RGB2GRAY, Ternary sum. FIR, image sharpening, and Gaussian blur filters                   | NA                                                                                                                                                 | NA             | approximate<br>adders and<br>multipliers  |

| 2015 | [56]  | General-<br>purpose<br>hardware (het-<br>erogeneous<br>mobile, tablet,<br>and server<br>processors) | x264, Swaptions, Bodytrack, Swish++, Radar, Canneal, Ferret, and Streamcluster            | PowerDial<br>(changes pro-<br>gram inputs<br>data structure),<br>and Loop<br>Perforation                                                           | NA             | NA                                        |

| 2020 | [57]  | General-<br>purpose CPU<br>and DNN<br>accelerator                                                   | AlexNet, SimpleNet, LeNet, MobileNet, ResNet-20, 10-Layers, and VGG-11/16                 | DNN layer<br>Quantization                                                                                                                          | NA             | NA                                        |

| 2023 | [38]  | General-<br>purpose CPU                                                                             | Matrix Multi-<br>plication, and<br>FIR filter                                             | NA                                                                                                                                                 | NA             | approximate<br>adders and<br>multipliers  |

**Table 8.** AxC techniques in research works using EAs as a search algorithm to perform the DSE.

| Year | Ref.    | Target                                   | Benchmarks                                                     |                                                                                                                              | AxC Techniques |                                                                 |

|------|---------|------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------|

|      |         | Hardware                                 |                                                                | Software                                                                                                                     | Architectural  | Hardware                                                        |

| 2021 | [58,59] | FPGA                                     | pixel-<br>streaming<br>pipeline                                | NA                                                                                                                           | NA             | Sparse LUTs,<br>Precision Scal-<br>ing, Approxi-<br>mate Adders |

| 2023 | [60]    | FPGA-based<br>approximate<br>accelerator | Multiplierless<br>MCM                                          | NA                                                                                                                           | NA             | approximate<br>adders and<br>multipliers                        |

| 2022 | [61]    | Accelerator<br>(FPGA and<br>ASIC)        | DCT                                                            | NA                                                                                                                           | NA             | approximate<br>adders                                           |

| 2014 | [62]    | General-<br>purpose CPU<br>(implied)     | FFT, SOR, MC, SMM, LU, Zxing, JMEint, Imagefill, and raytracer | program static<br>instructions                                                                                               | NA             | NA                                                              |

| 2023 | [63]    | GPU                                      | MobileNetV2,<br>and<br>ResNet50V2                              | approximate 8xN bit multipliers emulated using LUTs, approximate depthwise convolu- tion, and quantization- aware train- ing | NA             | NA                                                              |

**Table 9.** AxC techniques in research works using custom search algorithms to perform the DSE.

| Year | Ref. | Target                                                   | Benchmarks                                                                                                                                                            |                                                                                  | AxC Techniques                                                                |                                                                                                                         |

|------|------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|      |      | Hardware                                                 |                                                                                                                                                                       | Software                                                                         | Architectural                                                                 | Hardware                                                                                                                |

| 2016 | [64] | ASIC, and FPGA                                           | SAD                                                                                                                                                                   | NA                                                                               | NA                                                                            | approximate<br>adders and<br>logic blocks                                                                               |

| 2020 | [65] | ASIC, and FPGA                                           | ResNet-<br>18/34/38/74,<br>MobileNetV2,<br>and<br>Transformer-<br>base/WikiText-<br>103                                                                               | Progressive Fractional Quantization (PFQ), Dynamic Fractional Quantization (DFQ) | NA                                                                            | NA                                                                                                                      |

| 2016 | [66] | ASIC (implied)                                           | Array Multiplier, Carry Lookahead Adder, Kogge Stone Adder, Multiple and Accumulate, SAD, Euclidean distance, DCT, FFT, and FIR. All used in a DNN vector accelerator | NA                                                                               | NA                                                                            | Logic isolation<br>using latches<br>or AND/OR<br>gates at the<br>inputs, MUXes<br>at the output,<br>and power<br>gating |

| 2019 | [67] | ASIC (implied)                                           | SAD                                                                                                                                                                   | NA                                                                               | NA                                                                            | Approximate adders                                                                                                      |

| 2021 | [68] | ASIC (implied)                                           | Sobel, FIR, and Gaussian blur filters, a ReLu Neuron, Euclidean distance                                                                                              | NA                                                                               | NA                                                                            | Clock-gating,<br>and Precision<br>reduction<br>of primary<br>inputs at the<br>RTL level                                 |

| 2017 | [69] | VLSI systems<br>and HLS,<br>aligning with<br>ASIC design | average number calculator, inverse DCT calculator, Sobel, FIR, interpolation and decimation filters                                                                   | Source-Code<br>Pruning Based<br>on Profiling                                     | Functional Unit Substitution (additions and multiplications) at the HLS level | Internal Signal<br>Substitution,<br>and Bit-Level<br>Optimization<br>at the RTL<br>level                                |

| 2020 | [70] | HLS tools for<br>accelerator de-<br>sign                 | Sobel and<br>Sharpen filters                                                                                                                                          | NA                                                                               | NA                                                                            | approximate<br>adders and<br>multipliers                                                                                |

**Table 10.** AxC techniques in research works using custom search algorithms to perform the DSE (continued.)

| (cc  | ntinued.) |                                                |                                                                                                                                                                                                                |                                                                                                                                             |                                 |                                                                                |

|------|-----------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------|

| Year | Ref.      | Target                                         | Benchmarks                                                                                                                                                                                                     |                                                                                                                                             | AxC Techniques                  |                                                                                |

|      |           | Hardware                                       |                                                                                                                                                                                                                | Software                                                                                                                                    | Architectural                   | Hardware                                                                       |

| 2018 | [71]      | hardware<br>accelerator<br>(ASIC im-<br>plied) | Matrix Multi-<br>plication, So-<br>bel filter, and<br>DCT                                                                                                                                                      | partial prod-<br>uct perfo-<br>ration in<br>approximate<br>multipliers,<br>and trun-<br>cation in<br>approximate<br>adders/sub-<br>tractors | NA                              | inexact compressor in approximate multipliers, approximate full adder, and VOS |

| 2016 | [72]      | ML accelerator (ASIC)                          | Eye, and Face detection. Optical digit, Digit, Webpage, and Text classification                                                                                                                                | NA                                                                                                                                          | NA                              | Clock Overgating                                                               |

| 2021 | [73,74]   | ASIC (AI Accelerator)                          | VGG16,<br>ResNet50,<br>InceptionV3,<br>InceptionV4,<br>MobileNetV1,<br>SSD300,<br>YoloV3,<br>YoloV3-Tiny,<br>BERT, a 2-<br>layer LSTM,<br>and a 4-layer<br>bidirectional<br>LSTM                               | NA                                                                                                                                          | precision<br>reduction          | approximated activation functions, pooling, normalization, and data shuffling  |

| 2016 | [75]      | NPU (ASIC)                                     | Blackscholes,<br>FFT, Inversek2j,<br>Jmeint, JPEG,<br>Sobel filter                                                                                                                                             | NA                                                                                                                                          | Use of NNs<br>(NPU accelerator) | NA                                                                             |

| 2019 | [76]      | Not specified (implied general-purpose)        | Matrix Multi-<br>plication, and<br>FIR filter                                                                                                                                                                  | NA                                                                                                                                          | NA                              | approximate<br>adders and<br>multipliers                                       |

| 2016 | [77]      | GPÛ                                            | For GPU: Backprop, Fastwalsh, Gaussian, Heartwall, Matrixmul, Particle filter, Similarity score, S.reduce, S.reduce, S.srad2, and String match. For CPU: Bwaves, CactusADM, FMA3D, GemsFDTD, Soplex, and Swim. | NA                                                                                                                                          | NA                              | RFVP                                                                           |

**Table 11.** AxC techniques in research works that perform the DSE for approximate functions design space instead of a complete system.

| Year | Ref. | Target                                                                | Benchmarks                                                                                  |          | AxC Techniques |                                                                |

|------|------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------|----------------|----------------------------------------------------------------|

|      |      | Hardware                                                              |                                                                                             | Software | Architectural  | Hardware                                                       |

| 2021 | [78] | FPGA (also<br>ASIC implied)                                           | apex2, b12,<br>clip, duke2,<br>and vg2<br>benchmarks<br>from IWLS'93<br>Benchmark Set       | NA       | NA             | Logic Falsifica-<br>tion                                       |

| 2014 | [79] | FPGA and<br>ASIC (im-<br>plied)                                       | Ripple Carry, Carry Lookahead, and Kogge Stone Adders. Wallace, and Dadda Multipliers.      | NA       | NA             | Boolean<br>network sim-<br>plifications<br>allowed by<br>EXDCs |

| 2021 | [80] | FPGA and<br>ASIC (de-<br>signing fault-<br>tolerant<br>architectures) | generic combinational circuits                                                              | NA       | NA             | Logic Falsifica-<br>tion                                       |

| 2021 | [81] | FPGA and<br>ASIC (im-<br>plied)                                       | approximate<br>adders, multi-<br>pliers, divisor,<br>barrel shifter,<br>Sine, and<br>Square | NA       | NA             | Approximation based on BMF for truth tables                    |

| 2022 | [82] | FPGA                                                                  | approximate<br>adders, mul-<br>tipliers, de-<br>coders, and<br>ALUs                         | NA       | NA             | customized approximation of Boolean networks                   |