Article

Not peer-reviewed version

# Superior High Transistor's Effective Mobility of 325 cm2/V-s by 5-nm Quasi-Two-Dimensional SnON nFET

Pheiroijam Pooja, Chun Che Chien, Albert Chin\*

Posted Date: 26 May 2023

doi: 10.20944/preprints202305.1883.v1

Keywords: high mobility; thin film transistors; SnON; SnO2; density functional theory

Preprints.org is a free multidiscipline platform providing preprint service that is dedicated to making early versions of research outputs permanently available and citable. Preprints posted at Preprints.org appear in Web of Science, Crossref, Google Scholar, Scilit, Europe PMC.

Copyright: This is an open access article distributed under the Creative Commons Attribution License which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Disclaimer/Publisher's Note: The statements, opinions, and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions, or products referred to in the content.

Article

# Superior High Transistor's Effective Mobility of 325 cm<sup>2</sup>/V-s by 5-nm Quasi-Two-Dimensional SnON nFET

# Pheiroijam Pooja, Chun Che Chien and Albert Chin \*

Department of Electronics Engineering, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan; pheiroijampooja2021@gmail.com (P.P.); dragon85868586@gmail.com (C.C.C.)

Correspondence: achin@nycu.edu.tw, phone number: +886-3-5731841

**Abstract:** This work reports the first nanocrystalline SnON (7.6 % Nitrogen content) nanosheet n-type Field-Effect Transistor (nFET) with transistor's effective mobility ( $\mu_{eff}$ ) as high as 357 and 325 cm²/V-s at electron density ( $Q_e$ ) of  $5\times10^{12}$  cm<sup>-2</sup> and ultra-thin body thickness ( $T_{body}$ ) of 7 nm and 5 nm respectively. At the same  $T_{body}$  and  $Q_e$ , these  $\mu_{eff}$  values are significantly higher than single crystalline Si, InGaAs, thin-body Si-on-Insulator (SOI), two-dimensional (2D) MoS<sub>2</sub> and WS<sub>2</sub>. New discovery of slower  $\mu_{eff}$  decay rate at high  $Q_e$  than SiO<sub>2</sub>/bulk-Si universal curve was found, owing to one order of magnitude lower effective field ( $E_{eff}$ ) by more than 10 times higher dielectric constant ( $\kappa$ ) in channel material, which keeps the electron wave-function away from the gate-oxide/semiconductor interface and lowers the gate-oxide surface scattering. In addition, the high  $\mu_{eff}$  is also due to the overlapped large radius s-orbitals, low 0.29 m<sub>0</sub> effective mass ( $m_e$ ) and low polar optical phonon scattering. SnON nFETs with record-breaking  $\mu_{eff}$  and quasi-2D thickness enable potential monolithic three-dimensional (3D) integrated circuit (IC) and embedded memory for 3D biological brain-mimicking structures.

Keywords: high mobility; thin film transistors; SnON; SnO2; density functional theory

### 1. Introduction

Modern processors, with over 100 billion transistors, are among the most complex systems. To meet the ever-changing demand for small and high-performance devices, processor transistor density and performance must be increased. Therefore, Moore's law must be preserved, i.e., transistor must be kept shrinking in size. Fin Field Effect Transistor (FinFET) technology is a game changer in enabling 22 to 3 nm technology nodes [1,2]. However, at sub-3 nm technology nodes in the near future, FinFET technology will face critical challenges of limited area scaling and performance degradation. The Fin width can no longer be scaled down due to increased threshold voltage ( $V_{th}$ ) shift and lowered transistor's effective mobility ( $\mu_{eff}$ ) [3]. Gate length is also difficult to reduce due to transistor's quantum-mechanical (QM) tunneling from source to drain [4], resulting in high leakage current even when the transistor is off. Nanosheet (NS) transistors are the best solution to overcome these challenges of FinFET scaling, enabling higher drive currents [5,6]. NS-FETs are suitable for high computing needs due to their compatibility with various materials such as InGaAs, two-dimensional (2D) MoS<sub>2</sub> and WS<sub>2</sub>, among others.

The downscaling of Si NS complementary FET is planned to 1 nm node, but further shrinking device is limited by the 2D material and hyper numerical-aperture (NA) extreme-ultraviolet (EUV) lithography. Unfortunately, there is no known solution to form defect-free and uniform monolayer 2D material over the 12-inch wafer. The rapidly increasing cost and huge power consumption are the major bottlenecks to realize hyper-EUV lithography system. Those downscaling barriers may be overcome by the monolithic three-dimensional (3D) structure [4,7,8] that mimic the bio-brain. In addition, monolithic 3D integrated circuits (ICs) can provide better performance of higher operating frequencies and lower power consumption than their 2D counterparts [7]. Yet the poor  $\mu_{eff}$  for transistor made on backend dielectric of an IC is the basic challenge. Peviously, we reported high field-effect mobility ( $\mu_{FE}$ ) of SnO<sub>2</sub> [4,9,10] and SnON FET [11], but the effective mobility ( $\mu_{eff}$ ) is the required important

data for transistors. The  $\mu_{eff}$  can give crucial information on electron scattering mechanisms over the wide range of inversion charge  $(Q_e)$ . The  $Q_e$  or gate voltage  $(V_G)$  dependent  $\mu_{eff}$  is also essential for device modeling used for IC design. In this report, we measure the transistor output current over a wide range of V<sub>G</sub>, equivalent to a  $Q_e$  close to  $1\times10^{13}$  cm<sup>-2</sup>, to analyze the device scaling mechanism. Such high  $Q_e$  is critical to deliver a high transistor's output current and drive the IC speed quickly. The μ<sub>eff</sub> degrades monotonically with increasing charge density is the physical limitation of a Metal-Oxide-Semiconductor FET (MOSFET). However, the MOSFET must be biased at high charge density to deliver a high output current. For the first time, this fundamental restriction is overcome by using a higher dielectric constant ( $\kappa$ ) and high  $\mu_{eff}$  channel. The nanocrystalline SnON n-type FET (nFET) has  $\mu_{eff}$  as high as 325 cm<sup>2</sup>/V-s at  $5\times10^{12}$  cm<sup>-2</sup> electron density (Q<sub>e</sub>) and 5 nm nanosheet body thickness ( $T_{body}$ ). At the same  $T_{body}$ , this  $\mu_{eff}$  is significantly higher than singlecrystalline Si, InGaAs, 2D MoS<sub>2</sub>, 2D WS<sub>2</sub> and 2D WSe<sub>2</sub>. The high  $\mu_{eff}$  is also due to small 0.29 m<sub>o</sub> effective mass ( $m_e^*$ ), overlapped large radius s-orbital, signifincatly lower effective field ( $E_{eff}$ ) by >10× higher  $\kappa$  value than Si, GaAs, InP, GaN and SiC. The N<sup>3</sup>- anions having higher p orbital energy can move up valance band (Ev) from first principle QM calculation and the Oxygen vacancy levels (Vo) residing in the channel layer are reduced to improve the  $\mu_{eff}$ . The 3D 400°C process of SnON does not require a single crystal substrate; thus, the energy consumption is many orders of magnitude lower than today's single crystal Si wafer. The record-high µ<sub>eff</sub> and quasi-2D thickness SnON nFET suggest potential monolithic threedimensional (3D) and embedded dynamic random access memory (DRAM), to mimic the 3D bio-brain structure.

### 2. Materials and Methods

The bottom-metal-gate/high-k/[SnON or SnO<sub>2</sub>] nFETs were made by depositing a 50 nm TaN as bottom gate using reactive sputtering. Then, a 45-nm high-κ HfO<sub>2</sub> and 3-nm SiO<sub>2</sub> were deposited as a gate dielectric using electron-beam evaporator and annealed at 400°C under oxygen environment for 30 minutes using furnace. Further, SnON or SnO2 channel layer were deposited by reactive sputtering using Sn target (purity 99.99%) followed by post-annealing at 400°C. The Sn sputter power, argon flow rate and process pressure is fixed at 30 W, 24 sccm and 7.6 × 10-3 torr respectively. O<sub>2</sub> flow rate is fixed at 20 sccm for SnO2 channel layer. 7.6 % Nitrogen content (30 sccm of Nitrogen) are used for deposition of SnON channel layer. The source-drain electrodes of 80 nm thick Al was deposited and patterned using thermal coater. The fabricated nFET has channel length of 50 µm and width of 500 μm, respectively. The material properties of SnON and SnO<sub>2</sub> were studied using first principle QM calculations [12]. The Broyden-Fletcher-Goldfarb-Shanno (BFGS) minimization technique has been used to optimize the crystal structure [13]. It was done using the self-consistent field approach, which has a convergence precision of 1×10-8 eV/atom. This study made use of the generalized gradient approximation (GGA) with local density approximation plus U (LDA+U) approach. The energy cutoff for enlarging the plane wave basis set was set at 430 eV, and the Brillouin zone was sampled using the Monkhorst-Pack k-point approach with the k-points (6 ×6×5) [14].

### 3. Results

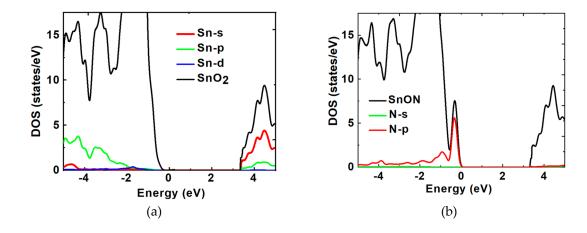

Using first principle calculations based on density functional theory, the density of state (DOS) for SnO<sub>2</sub> and SnON were examined as shown in Figure 1 (a) and (b), respectively. For convenience of analysis, the valence band maximum (VBM) was adjusted to zero. The lower conduction states close to the conduction band minimum (CBM) in SnO<sub>2</sub> and SnON were primarily produced from Sn 5s orbitals [15], while the localized states immediately above the VBM in SnON had a predominance of N 2p character. The N states in the valence band, principally N 2p character, are the main cause of the bandgap reduction in SnON. SnO<sub>2</sub> and N<sub>2</sub> doped SnO<sub>2</sub> have effective electron masses ( $m_e$ \*) of 0.41  $m_o$  and 0.29  $m_o$ , respectively, where  $m_o$  is the free electron mass which is reported in our previous work [11]. The  $m_e$ \* for SnON is evidently smaller than SnO<sub>2</sub>, which could result in a larger  $\mu_{eff}$ .

2

Figure 1. (a) DOS of Sn in  $SnO_2$  and (b) DOS of N in SnON calculated using first principle density functional theory.

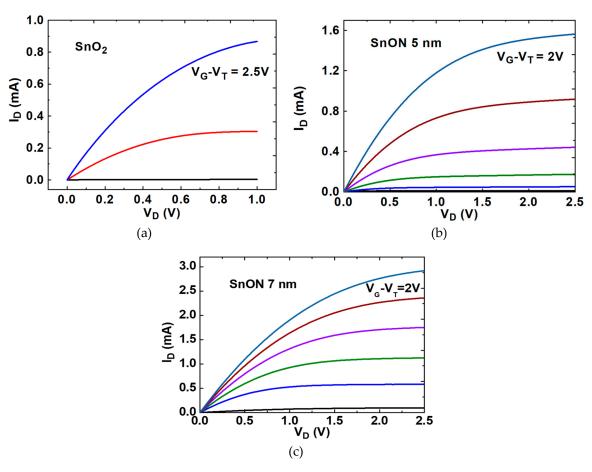

Figure 2 (a)-(c) depicts the transistor's drain-current versus drain-voltage (ID-VD) characteristics at various  $V_G$  for  $SnO_2$  and SnON nFETs with  $T_{body}$  of 5 nm and 7 nm. A clear pinch-off and good current saturation were measured. The SnON nFETs displayed higher ID compared to control  $SnO_2$  device. Because the metal-gate/high- $\kappa$  was made at the same run with identical gate oxide capacitance, the only reason to cause significantly higher ID at the same  $V_G$ - $V_T$  of SnON nFET is due to the higher  $\mu_{eff}$ .

**Figure 2.** ID-VD output characteristics for (a) TaN/HfO<sub>2</sub>/5-nm-SnO<sub>2</sub> nFET (b) TaN/HfO<sub>2</sub>/5-nm-SnON nFET and (c) TaN/HfO<sub>2</sub>/7-nm-SnON nFET.

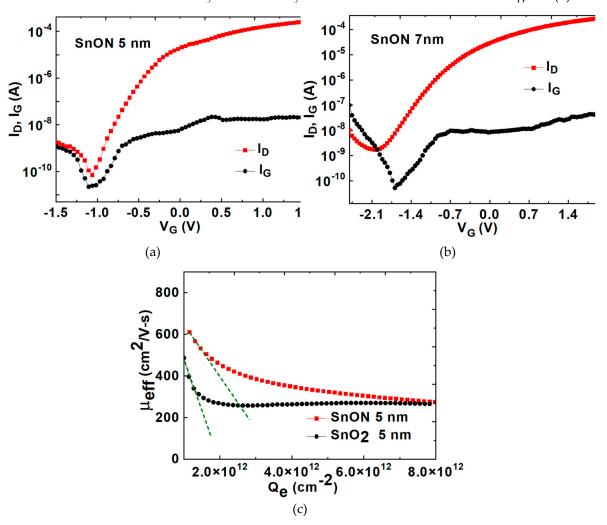

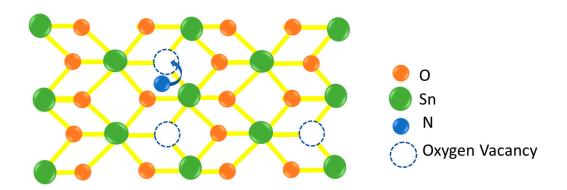

Figure 3 (a) and (b) display gate-current versus gate-voltage (I<sub>G</sub>-V<sub>G</sub>) and I<sub>D</sub>-V<sub>G</sub> transfer characteristics at a V<sub>D</sub>=0.1 V for SnON nFETs with T<sub>body</sub> of 5 and 7 nm. Large on-current/off-current (I<sub>ON</sub>/I<sub>OFF</sub>) is achieved in 5 nm T<sub>body</sub> thickness that is important for IC application. The FET's scattering mechanism is further analyzed by the μ<sub>eff</sub> as a function of Q<sub>e</sub>. As shown in Figure 3 (c), at low to medium Q<sub>e</sub>, the nFET's μ<sub>eff</sub> of SnO<sub>2</sub> is significantly lower than SnON one. The SnO<sub>2</sub> nFET shows much faster μ<sub>eff</sub> degradation with increasing Q<sub>e</sub>. Although the oxide charges in high-κ dielectric is responsible for lower μ<sub>eff</sub> than conventional SiO<sub>2</sub> gate dielectric [16–19], such μ<sub>eff</sub> reduction is most significant at high Q<sub>e</sub> rather than at low Q<sub>e</sub>. It is reported that the μ<sub>eff</sub> at low E<sub>eff</sub> or Q<sub>e</sub> is due to coulomb scattering from charged impurities [20]. The potential reason for such larger μ<sub>eff</sub> of SnON nFET than that of SnO<sub>2</sub> may be related to the lower charged V<sub>o</sub>. By injecting non-oxide nitrogen anions, SnON can lower the defect trap densities. This allows for the removal or passivation of Vo through substitutional alloying with N<sup>3-</sup> to improve the μ<sub>eff</sub> as seen in Figure 4. Similar observations were also found with ZnON [21]. It is well-known that the transition SiO<sub>x</sub> between Si and SiO<sub>2</sub> gives a positive fixed oxide charge, primarily due to structural V<sub>o</sub> defects in the oxide layer. Such positive V<sub>o</sub> charge close to valence band in SnON may be lowered by extra N-band as shown in DOS of Figure 1(b).

**Figure 3.** Ig-Vg and Ip-Vg transfer characteristics for (a) TaN/HfO<sub>2</sub>/5-nm-SnON nFET and (b) TaN/HfO<sub>2</sub>/7-nm-SnON nFET; and (c)  $\mu$ <sub>eff</sub> versus Q<sub>e</sub> for 5-nm SnO<sub>2</sub> and SnON nFETs.

Figure 4. Diagrammatic sketch of substitutional alloying of Oxygen vacancy with Nitrogen atom

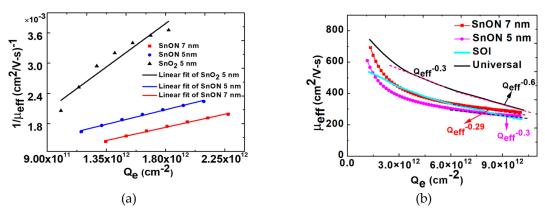

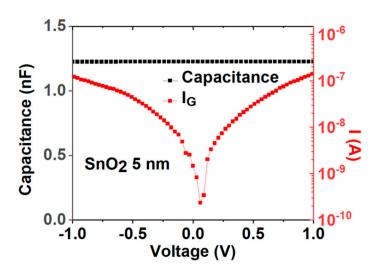

Figure 5 (a) further plots 1/µeff vs. Qe, and the large slope in the low Qe is related to charged Vo scattering in SnO<sub>2</sub> that is lowered by adding N<sup>3</sup> anions. We further compare the µeff-Qe dependence for universal SiO<sub>2</sub>/bulk-Si, SiO<sub>2</sub>/Si-on-Insulator (SOI), high-κ/SnO<sub>2</sub>, and high-κ/SnON nFETs. As shown in Figure 5 (b), the µeff as high as 357 and 325 cm<sup>2</sup>/V-s are achieved at Qe of 5×10<sup>12</sup> cm<sup>-2</sup> and Theody of 7 and 5 nm, respectively. At 1×1013 cm<sup>-2</sup> Q<sub>e</sub>, an ultra-thin 5 and 7 nm thickness, the μeff of high-κ/SnON nFET is 85% and 95% of universal SiO<sub>2</sub>/bulk-Si nFET. The μeff scattering mechanism of SiO<sub>2</sub>/bulk-Si nFET at low, medium, and high Eeff is due to coulomb, phonon, and surface scattering, respectively. The universal µeff of SiO<sub>2</sub>/bulk-Si nFET depends on standard Qe<sup>0.3</sup> in medium Qe, which becomes  $Q_e^{-0.6}$  dependence at high  $Q_e$  to  $1\times10^{13}$  cm<sup>-2</sup>. However, the  $\mu_{eff}$  decay rate of high- $\kappa$ /SnO<sub>2</sub> and high-к/SnON nFETs at high Qe is much slower than universal SiO2/bulk-Si and thin-body SOI nFETs [22]. To understand such abnormal slow  $\mu_{eff}$  dependence on  $Q_e$ , we further measured the dielectric constant, k of 5 nm SnO<sub>2</sub>. Figure 6 shows the measured capacitance under various voltage at 1 kHz. The SnO<sub>2</sub> has a κ of 123 that is >10× larger than major semiconductors of Si, GaAs, InP, GaN, SiC etc [23–27]. This high  $\kappa$  value is also close to the reported data in literature [28]. The novel discovery  $\mu_{\text{eff}}$ dependence on Qe<sup>0.30</sup> at high Qe range is due to the >10× higher κ value to keep high-κ/SnON nFET at medium Eeff range. Here the Eeff is proportional to Qe:

$$E_{eff} = \frac{1}{\varepsilon_{semi}} \left( \frac{|Q_e|}{n} + |N_{dep}| \right) \approx \frac{1}{\varepsilon_{semi}} \left( \frac{|Q_e|}{n} \right) @ \text{ high } Q_e$$

(1)

The  $\varepsilon_{semi}$  equals  $\varepsilon_0 \kappa$ , where  $\varepsilon_{semi}$  and  $\varepsilon_0$  are permittivity of semiconductor and free space respectively.  $N_{dep}$  is the depletion charge of charged impurities in doped Si or charged  $V_0$  in major oxide semiconductors. The n factor in SiO<sub>2</sub>/bulk-Si equals to 2 and 3 for nMOSFET and pMOSFET, respectively. The significantly much higher  $\kappa$  value than most of the commercial semiconductors of Si, GaAs, InP, GaN and SiC allow the channel electrons to keep a low  $E_{eff}$ . This in turn keeps the electron wave-functions in the conduction channel [29] away from the gate-oxide/semiconductor interface and decreases the gate-oxide surface scattering.

**Figure 5.** (a)  $1/\mu_{eff}$  versus  $Q_e$  plot for 5-nm SnO2, 5-nm SnON and 7-nm SnON nTFTs and (b)  $\mu_{eff}$  versus  $Q_e$  with different channel thickness of SnON nFET and comparison with SOI [22] and universal nFETs.

It is important to notice that the  $\mu_{eff}$  of SnON nFET are the highest values among all the oxide-based semiconductors. This is due to the smaller  $m_e^*$  and larger phonon energy  $(E_{op})$  [30] to give high  $\mu_{eff}$ :

$$\mu_{op} \alpha \frac{1}{(\frac{m_e^*}{m_0})^{\frac{3}{2}}} \frac{\exp(\frac{E_{op}}{kT}) - 1}{(\frac{E_{op}}{kT})^{\frac{1}{2}}}$$

(2)

The  $E_{op}$  is higher than ZnO, GaN, and SiC [31–34].

The total  $\mu_{eff}$  can be expressed as:

$$\frac{1}{\mu_{total}} = \frac{1}{\mu_{Vo}} + \frac{1}{\mu_{op}} \tag{3}$$

Here the  $\mu_{Vo}$  is the FET's mobility that is limited by charged  $V_o$ . This  $\mu_{Vo}$  is extremely important at low to medium  $Q_e$  shown in Figure 3 (c). The radius of s-orbital increases with increasing principle quantum number n with  $n^2$  dependence, so the overlapping s-orbitals are stronger for SnO<sub>2</sub> than ZnO [15]. This explains why the mobility of SnON nFET is significantly larger than that of ZnO.

Figure 6. C-V and I-V plot for Ni/SnO<sub>2</sub>/Ni capacitor.

Table 1 compares device performance. The wide energy bandgap ( $E_G$ ) nanocrystalline SnON nFET has the highest  $\mu_{eff}$  among single crystal Si, InGaAs, 2D MoS<sub>2</sub>, and 2D WS<sub>2</sub>. It is noticed that the next 2 nm node commercial NS nFET will use single crystalline Si with a  $T_{body}$  of 7 nm, since the  $\mu_{eff}$  decreases with decreasing  $T_{body}$  with a  $T_{body}^6$  dependence [3]. The  $\mu_{eff}$  of high- $\kappa$ /SnON nFETs is 2.7 times higher than that of Si nFET at the same 5 nm  $T_{body}$ , which could be used for downscaling the NS  $T_{body}$ . The wide- $E_G$  SnON also leads to large  $I_{ON}/I_{OFF}$  as shown in Figure 3 (a).

**Table 1.** Comparisons of 2D semiconductor performances with our present work at  $Q_e$  of  $5 \times 10^{12}$  cm<sup>-2</sup>

| Semiconductor        | E <sub>G</sub> (eV) | meff (mo) | Dielectric Const. | μeff (cm <sup>2</sup> /V-s) @5 nm |

|----------------------|---------------------|-----------|-------------------|-----------------------------------|

| Material             | κ                   |           |                   |                                   |

| SnON                 | ~3.3                | ~0.29     | 123               | 325                               |

| (This work)          |                     |           |                   |                                   |

| Si [5]               | 1.12                | 1.08      | 11.7              | 120                               |

| MoS <sub>2</sub> [5] | 1.8                 | ~0.5      | 4~8 (2~5 layers)  | 184                               |

| WS <sub>2</sub> [5]  | 1.4                 | 0.33      | -                 | 234                               |

| InGaAs [5]           | 0.75                | 0.042     | 12.9              | 200                               |

# 4. Conclusions

In this work, we demonstrated record high  $\mu_{eff}$  5-nm  $T_{body}$  nFETs, made on IC's backend for monolithic 3D usage. For the first time, the  $\mu_{eff}$  of 325 cm²/V-s at  $5\times10^{12}$  cm²  $Q_e$  is 2.7 times higher than that of Si nFET at the same  $T_{body}$  of 5 nm. This was achieved using wide- $E_G$  5 nm quasi-2D SnON channel at 400°C process. Such high FET's  $\mu_{eff}$  is due to the smaller 0.29  $m_o$ , overlapped large-radius s-orbitals, and low polar optical phonon scattering. In addition, smaller  $\mu_{eff}$  decay rate than SiO<sub>2</sub>/bulk-Si nFET at high  $Q_e$  was found, owing to <10×  $E_{eff}$  by >10× higher  $\kappa$  value. Record high  $\mu_{eff}$  SnON nFETs formed on IC's backend is the empowering technology for monolithic 3D ICs.

# **Supplementary Materials:**

**Author Contributions:** Pheiroijam Pooja did the simulation and writing, Chun Che Chien did the experiments; Albert Chin is the principal investigator (PI) to monitor the project. All authors reviewed the manuscript.

**Funding:** This research was funded by National Science and Technology Council of Taiwan, project no. 110-2221-E-A49-137-MY3.

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author. The data are not publicly available due to privacy

**Acknowledgments:** We would like to thank the National Yang Ming Chiao Tung university nano facility center for providing the laboratory instruments.

**Conflicts of Interest:** The authors declare no conflict of interest.

# References

- 1. Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J; Young, A. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In IEEE *Symposium on VLSI Technology*, Kyoto, Japan, **2017**, pp 230-231.

- 2. Jang, D.; Yakimets, D.; Eneman, G.; Schuddinck, P.; Bardon, M.G.; Raghavan, P.; Spessot, A.; Verkest, D.; Mocuta, A. Device exploration of nanosheet transistors for sub-7-nm technology node. *IEEE Trans. Electron Dev.* **2017**, 64, 2707–2713.

- 3. Low, T.; Li, M.F.; Fan, W.J.; Ng, S.T.; Yeo, Y.C.; Zhu, C.; Chin, A.; Chan, L; Kwong, D.L. Impact of surface roughness on silicon and germanium ultra-thin-body MOSFETs, In IEDM Technical Digest. *IEEE International Electron Devices Meeting*, San Francisco, CA, USA, 2004, pp 151-154.

- 4. Shih, C.W.; Chin, A.; Lu, C.F.; Yi, S.H. Extremely high mobility ultra-thin metal-oxide with ns²np² configuration, In IEDM Technical Digest. *IEEE International Electron Devices Meeting* Washington, DC, USA, 2015, pp 145-148.

- 5. Liu, Y.; Duan, X.; Huang, Y; Duan, X. Two-dimensional transistors beyond graphene and TMDCs, *Chem. Soc. Rev.* **2018**, 47, 6388-6409.

- 6. Kim, J.; Lee, J.S.; Han, J.W.; Meyyappan, M. Single-event transient in FinFETs and nanosheet FETs. *IEEE Electron Device Lett.* **2018**, 39, 1840-1843.

- 7. Yu, D. S.; Chin, A.; Laio, C. C.; Lee, C. F.; Cheng, C. F.; Chen, W. J.; Zhu, C.; Li, M.-F.; McAlister, S. P.; Kwong, D. L. 3D GOI CMOSFETs with Novel IrO<sub>2</sub>(Hf) dual gates and high-κ dielectric on 1P6M-0.18μm-CMOS. In IEDM Technical Digest. *IEEE International Electron Devices Meeting*, San Francisco, CA, USA, 2004, pp 181-184.

- 8. Chin, A.; Chen, Y. D. Technologies Toward Three-Dimensional Brain-Mimicking IC Architecture. In EDTM Technical Digest. *IEEE Electron Devices Technology & Manufacturing Conference*, Singapore, **2019**, pp 472-474.

- 9. Yen, T.J.; Chin, A; Gritsenko, V. High-performance top-gate thin-film transistor with an ultra-thin channel layer. *Nanomaterials* **2020**, 10, 2145.

- 10. Shih, C.W.; Chin; A., Lu, C.F.; Su, W.F. Low-temperature processed tin oxide transistor with ultraviolet irradiation, *IEEE Electron Device Lett.* **2019**, 40, 909-912.

- 11. Pooja, P.; Che, C.C.; Zeng, S.H.; Lee, Y.C.; Yen, T.J.; Chin, A. Outstanding High Field-Effect Mobility of 299 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> by Nitrogen-Doped SnO<sub>2</sub> Nanosheet Thin-Film Transistor, *Adv. Mater. Technol.* **2023**, 2201521.

- 12. Bussolotti, F.; Yang, J.; Kawai, H.; Chee, J.Y.; Goh, K.E.J. Influence of many-body effects on hole quasiparticle dynamics in a WS<sub>2</sub> monolayer, *Phys. Rev. B* **2021**, 103, 045412.

- 13. Fischer, T.H.; Almlof, J. General methods for geometry and wave function optimization. *The J. Phys. Chem.* **1992**, 96, 9768-9774.

- 14. Monkhorst, H.J.; Pack, J.D. Special points for Brillouin-zone integrations. Phys. Rev. B 1976, 13, 5188.

7

8

- 15. Shih, C.W.; Chin, A.; Lu, C.F.; Su, W.F. Remarkably high hole mobility metal-oxide thin-film transistors. *Sci. Rep.* **2016**, *6*, 19023.

- 16. X. Yu, C. Zhu, M. Yu, M. F. Li, **Albert Chin**, C. H. Tung, D. Gui, and D. L. Kwong, "Advanced MOSFETs using HfTaON/SiO<sub>2</sub> Gate Dielectric and TaN Metal Gate with Excellent Performance for Advanced Low Standby Power Application," *IEEE International Electron Devices Meeting (IEDM) Tech. Dig.*, pp. 31-34, Washington DC, Dec. 2005.

- 17. D. S. Yu, **Albert Chin**, C. H. Wu, M.-F. Li, C. Zhu, S. J. Wang, W. J. Yoo, B. F. Hung and S. P. McAlister, "Lanthanide and Ir-based Dual Metal-Gate/HfAlON CMOS with Large Work-Function Difference," *IEEE International Electron Devices Meeting (IEDM) Tech. Dig.*, pp. 649-652, Washington DC, Dec. 2005.

- 18. C. H. Wu, B. F. Hung, **Albert Chin**, S. J. Wang, X. P. Wang, M.-F. Li, C. Zhu, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang "High Temperature Stable [Ir<sub>3</sub>Si-TaN]/HfLaON CMOS with Large Work-Function Difference," *IEEE International Electron Devices Meeting (IEDM) Tech. Dig.*, pp. 617-620, San Francisco, CA, Dec. 2006

- C. F. Cheng, C. H. Wu, N. C. Su, S. J. Wang, S. P. McAlister and Albert Chin, "Very Low Vt [Ir-Hf]/HfLaO CMOS Using Novel Self-Aligned Low Temperature Shallow Junctions," in *IEEE International Electron Devices Meeting (IEDM) Tech. Dig.*, pp. 333-336, Washington DC, Dec. 2007.

- Takagi, S.I.; Toriumi, A.; Iwase, M; Tango, H. On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration. *IEEE Trans. on Electron Dev.* 1994, 41, 2357-2362.

- 21. Park, J.; Jeong, H.J.; Lee, H.M.; Nahm, H.H; Park, J.S. The resonant interaction between anions or vacancies in ZnON semiconductors and their effects on thin film device properties. *Sci. Rep.* **2017**, *7*, 2111.

- 22. Rim, K.; Chan, K.; Shi, L.; Boyd, D.; Ott, J.; Klymko, N.; Cardone, F.; Tai, L.; Koester, S.; Cobb, M; Canaperi, D. Fabrication and mobility characteristics of ultra-thin strained Si directly on insulator (SSDOI) MOSFETs. In IEDM Technical Digest. *IEEE International Electron Devices Meeting*, Washington, DC, USA, 2003, pp 1-4.

- 23. Baroni, S; Resta, R. Ab initio calculation of the macroscopic dielectric constant in silicon. *Phys. Rev. B*, **1986**, 33, 7017.

- 24. Kunc, K.; Resta, R. External fields in the self-consistent theory of electronic states: a new method for direct evaluation of macroscopic and microscopic dielectric response. *Phys. Rev. Lett.* **1983**, 51, 686.

- Neidert, R.E.; Binari, S.C.; Weng, T. Dielectric constant of semi-insulating indium phosphide. *Electronic*. Lett. 1982, 18, 987-988.

- 26. Kane, M.J.; Uren, M.J.; Wallis, D.J.; Wright, P.J.; Soley, D.E.J.; Simons, A.J.; Martin, T. Determination of the dielectric constant of GaN in the kHz frequency range. *Semicond. Sci. Technol.* **2011**, 26, 085006.

- 27. Moore, W.J.; Holm, R.T.; Yang, M.J.; Freitas Jr, J.A. Infrared dielectric constant of cubic SiC. *J. Appl. Phys.* 1995, 78, 7255-7258.

- 28. Youssef, A.M; Yakout, S.M. Colossal dielectric constant, electric modulus and electrical conductivity of nanocrystalline SnO<sub>2</sub>: Role of Zr/Mn, Fe or Co dopants. *J. Solid State Chem.*, **2022**, 308, 122902.

- 29. Yi, S.H.; Ruan, D.B.; Di, S.; Liu, X.; Wu, Y.H; Chin, A. High performance metal-gate/high-k GaN MOSFET With good reliability for both logic and power applications. *IEEE J. Electron Devices Soc.* **2016**, 4, 246-252.

- 30. Shih, C.W.; Chin, A. New material transistor with record-high field-effect mobility among wide-band-gap semiconductors. *ACS Appl. Mater. Interfaces* **2016**, 8, 19187–19191.

- 31. Shan, W.; Walukiewicz, W.; Ager, J.W.; Yu, K.M.; Yuan, H.B.; Xin, H.P.; Cantwell, G.; Song, J.J. Nature of room-temperature photoluminescence in ZnO. *Appl. Phys. Lett.* **2005**, 86, 191911.

- 32. Jarzebski, Z.M.; Morton, J.P. Physical properties of SnO<sub>2</sub> materials: III. Optical properties. *J. Electrochem. Soc.* **1976**, 123, 333C.

- 33. Ogino, T; Aoki, M. Photoluminescenece in P-doped GaN. Jpn. J. App. Phys. 1979, 18, 1049.

- 34. Minamitani, E.; Arafune, R.; Frederiksen, T.; Suzuki, T.; Shahed, S.M.F.; Kobayashi, T.; Endo, N.; Fukidome, H.; Watanabe, S; Komeda, T. Atomic-scale characterization of the interfacial phonon in graphene/SiC. *Phys. Rev. B.* **2017**, 96, 155431.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.